| 数字电路基础知识 | 您所在的位置:网站首页 › 电压Vol › 数字电路基础知识 |

数字电路基础知识

|

一、反相器的结构

其中涉及到的的四个重要参数: VIH:输入电压由高到低变化时,输出电压开始上升且传输特性曲线斜率为-1的点,即图中B点对应的输入电压。(仍能维持输出为逻辑 “0” 的最小输入电压) VIL:输入电压由低到高变化时,输出电压开始下降且传输特性曲线斜率为-1的点,即图中A点对应的输入电压。(仍能维持输出为逻辑 “1” 的最大输入电压) VOH:定义为最小合格高电平。(维持输出为逻辑“1”的最小输出电压) VOL:定义为最大合格低电平。(维持输出为逻辑“0”的最大输出电压) CMOS集成电路内部规定Vol = 0v,Voh = Vdd。 三、反相器的噪声容限(VTC曲线)噪声容限定义: 输入为高电平的噪声容限:VNH=VOH-VIH 输入为低电平的噪声容限:VNH=VIL-VOL 当反相器输入电压(Vil+Vih)/2接近于0.5Vdd,CMOS反相器的阈值电压也接近于0.5Vdd,这样输出不确定会是高电平还是低电平,输出呈亚稳态! 对于下面如下首尾相连的反向器结构: 图中的SNN即为静态噪声容限,方框面积越大,表示容限越大。 并且此电路只能工作在三种状态,分别是三个交点,当状态不在这三种状态时,输入、输出会将他们拉向两端。 (1)先解释两个名词: Transition Time(转换时间): 上升时间tr:从10%Vdd上升到90%Vdd的时间, 下降时间tf:从90%Vdd下降到10%dd的时间。 上升时间和下降时间统称为Transition Time,也有定义为20%到80%。 Propagation Delay(传播延时): 在输入信号变化到 50%Vdd到输出信号变化到50%Vdd之间的时间。 Propagation Delay(传播延时): 在输入信号变化到 50%Vdd到输出信号变化到50%Vdd之间的时间。  2)动态功耗 2)动态功耗

反相器从一种稳定状态突然变到另一种稳定状态的过程中,将产生附加的功耗,即动态功耗。 动态功耗包括:负载电容充放电所消耗的功率Pc和PMOS、NMOS同时导通所消耗的瞬时导通功耗PT 在工作频率较高的情况下,CMOS反相器的动态功耗要比静态功耗大得多,静态功耗可以忽略不计。 扇入:是指直接调用该模块的上级模块的个数。扇入大表示模块的复用程序高。 扇出:是指该模块直接调用的下级模块的个数。扇出大表示模块的逻辑复杂度高,需要控制和协调过多的下级模块; 对于一定扇出数的电路,电路的工作频率随之确定,一般工作频率越高,扇出数越小。在低频(< 1MHz)的工作条件下,CMOS电路的扇出数可以达到50以上。 因此。扇入越大越好,扇出越大越坏。在设计中,尽量减小扇出 |

【本文地址】

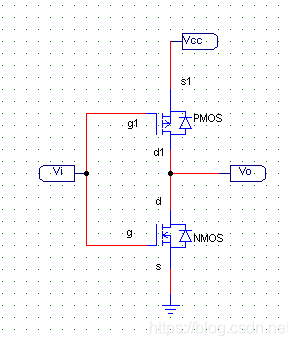

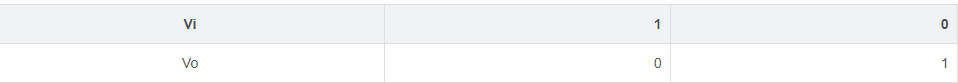

CMOS反相器由一个PMOS管、一个NMOS管、一个输入源Vi和一个直流电源Vcc组成。 具体的真值表如下图所示:

CMOS反相器由一个PMOS管、一个NMOS管、一个输入源Vi和一个直流电源Vcc组成。 具体的真值表如下图所示: ①当Vi为低电平时,对于下管有Vgs|Vgs(th)|,且|Vg1s1|足够大,PMOS管进入可变电阻区,管压降很小,Vo=Vcc。 ②当Vi为高电平时,对于上管有|Vg1s1|Vgs(th),且Vgs足够大,NMOS管进入可变电阻区,管压降很小,Vo=0。

①当Vi为低电平时,对于下管有Vgs|Vgs(th)|,且|Vg1s1|足够大,PMOS管进入可变电阻区,管压降很小,Vo=Vcc。 ②当Vi为高电平时,对于上管有|Vg1s1|Vgs(th),且Vgs足够大,NMOS管进入可变电阻区,管压降很小,Vo=0。 AB:T1导通T2截止 BC:T1T2导通 CD:T1截止T2导通 VTC(Voltage Transfer Characteristics)曲线:

AB:T1导通T2截止 BC:T1T2导通 CD:T1截止T2导通 VTC(Voltage Transfer Characteristics)曲线:  VTC的形状基本上与高于阈值的操作相同。VTC陡峭部分的斜率取决于反向器的亚阈值斜率。

VTC的形状基本上与高于阈值的操作相同。VTC陡峭部分的斜率取决于反向器的亚阈值斜率。

总功耗为P=PT+Pc。

总功耗为P=PT+Pc。