| 浅谈常用ADC的工作原理与选型! | 您所在的位置:网站首页 › 单片机adc工作过程图解 › 浅谈常用ADC的工作原理与选型! |

浅谈常用ADC的工作原理与选型!

|

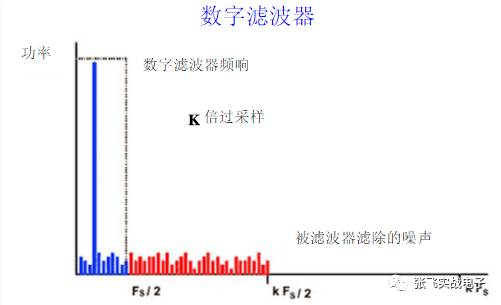

现在的软件、无线电、数字图像采集都需要有高速的A/D采样保证有效性和精度,一般的测控系统也希望在精度上有所突破,人类数字化的浪潮推动了A/D转换器不断变革,而A/D转换器是人类实现数字化的先锋。A/D转换器发展了30多年,经历了多次的技术革新,从Flash、SAR、积分型ADC,到近年来新发展起来的 ∑-Δ型 和 Pipeline ADC,它们各有其优缺点,能满足不同的应用场合的使用。 ADC的工作原理 模拟信号转换为数字信号,一般分为4个步骤进行,即采样、保持、量化和编码。前2个步骤在采样-保持电路中完成,后两步骤则在ADC中完成。ADC是把经过与标准量比较处理后的模拟量转换成以二进制数值表示的离散信号的转换器。故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为最大的可转换信号大小。而输出的数字量则表示输入信号相对于参考信号的大小。 ADC的分类1、Σ-Δ ADC 越来越多的应用,诸如过程控制、称重等,都需要高分辨率、高集成度和价格低廉的ADC。新型Σ-Δ转换技术恰好可以满足上述需求。然而,很多设计者并不十分了解这种AD转换技术,因而更愿意选用传统的逐次比较(SAR)型ADC。Σ-Δ转换器的模拟部分非常简单(类似于一个1位ADC),而数字部分要复杂得多,按照功能可划分为数字滤波和抽取单元。由于Σ-Δ型ADC更接近于数字器件,因而其制造成本非常低廉。 Σ-Δ ADC的工作原理 要理解Σ-Δ型ADC的工作原理,首先应对以下概念有所了解:过采样、噪声成形、数字滤波和抽取。1. 过采样 首先,考虑一个传统ADC的频域传输特性。输入一个正弦信号,然后以频率Sf采样,按照Nyquist定理,采样频率至少倍于输入信号。从FFT分析结果可以看到,一个单音和一系列频率分布于DC到S2f间的随机噪声,如图1所示,这就是所谓的量化噪声,主要是由于有限的ADC分辨率而造成的

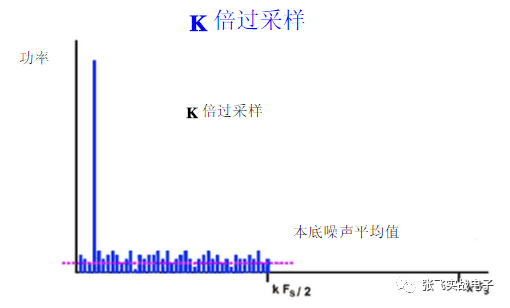

图1 单音(基频)信号的功率与所有频率的噪声的RMS功率之和的比值就是信号噪声比(SNR)。对于一个N位ADC,SNR可由公式:SNR=6.02N+1.76dB得到。为了改善SNR和更为精确地再现输入信号,对于传统ADC来讲,必须增加位数。 如果将采样频率提高一个过采样系数k,即采样频率为Skf,再来讨论同样的问题,如图2所示,FFT分析显示噪声基线降低了,SNR值虽未改变,但噪声能量却分散到更宽的频率范围。Σ-Δ转换器正是利用了这一原理,具体方法就是在1位ADC之后进行数字滤波。如图3所示,由于大部分噪声位于数字滤波器带宽之外而被滤除,这样,RMS噪声就降低了,使得Σ-Δ转换器能够从一个低分辨率ADC获得宽动态范围

图2

图3 那么,简单的过采样和滤波能否改善SNR呢?一个1位 ADC的SNR为7.78dB(6.02+1.76),每4倍过采样可以使SNR增加6dB,SNR每增加6dB等效于分辨率增加1-bit。这样,采用1位 ADC进行64倍(即34倍)过采样可以获得4位分辨率,而要获得16位分辨率就必须进行154倍过采样,这是不切实际的。Σ-Δ转换器采用噪声成形技术消除了这种局限,使得每4倍过采样可增加高于6dB的SNR. 2、SAR型ADC(又名逐次比较型) 数年以来,逐次逼近型ADC一直是数据采集系统的主要依靠。近期设计改良使这类ADC的采样频率扩展至兆赫领域且分辨率为18位。ADI公司的PulSAR®系列SAR ADC采用内部开关电容技术和自动校准,以CMOS工艺实现18位、2 MSPS性能(AD7641),而无需进行昂贵的薄膜激光调整。在16位级别,AD7625(6 MSPS)和AD7626(10 MSPS)还代表着突破性的技术。

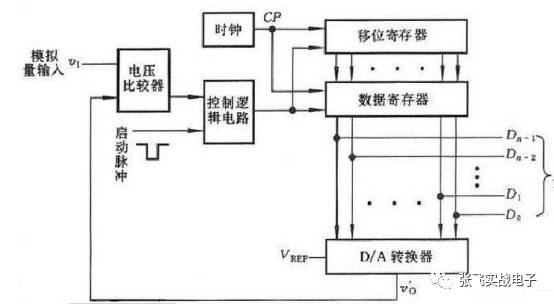

图4 逐次比较型ADC 1.转换方式直接转换ADC 2.电路结构逐次逼近ADC包括n位逐次比较型A/D转换器如图4所示。它由控制逻辑电路、时序产生器、移位寄存器、D/A转换器及电压比较器组成。图4逐次比较型A/D转换器框图 3.工作原理逐次逼近转换过程和用天平称物重非常相似。天平称重物过程是,从最重的砝码开始试放,与被称物体行进比较,若物体重于砝码,则该砝码保留,否则移去。再加上第二个次重砝码,由物体的重量是否大于砝码的重量决定第二个砝码是留下还是移去。照此一直加到最小一个砝码为止。将所有留下的砝码重量相加,就得此物体的重量。仿照这一思路,逐次比较型A/D转换器,就是将输入模拟信号与不同的参考电压作多次比较,使转换所得的数字量在数值上逐次逼近输入模拟量对应值。 对图4的电路,它由启动脉冲启动后,在第一个时钟脉冲作用下,控制电路使时序产生器的最高位置1,其他位置0,其输出经数据寄存器将1000……0,送入D/A转换器。输入电压首先与D/A器输出电压(VREF/2)相比较,如v1≥VREF/2,比较器输出为1,若vI< VREF/2,则为0。比较结果存于数据寄存器的Dn-1位。然后在第二个CP作用下,移位寄存器的次高位置1,其他低位置0。如最高位已存1,则此时vO=(3/4)VREF。于是v1再与(3/4)VREF相比较,如v1≥(3/4)VREF,则次高位Dn-2存1,否则Dn-2=0;如最高位为0,则vO=VREF/4,与vO比较,如v1≥VREF/4,则Dn-2位存1,否则存0……。以此类推,逐次比较得到输出数字量 总结 SAR ADC架构是一种完善、有效且易于理解的架构,非常适合现代细线CMOS工艺。该架构没有“流水线”延迟,因此非常适合单发和多路复用数据采集应用。CMOS工艺允许添加各种各样的数字功能,如自动通道时序控制和自动校准等。此外,许多SAR ADC拥有片上温度传感器和基准电压源。虽然SAR ADC源自16世纪的数学谜团,但是其仍然是现代多通道数据采集系统所青睐的转换器。 3.flash型ADC 早在上世纪60、70年代,商用_ash转换器就开始出现在仪器仪表和模块中,并在80年代期间快速进军集成电路。单芯片8位_ash ADC成为上世纪80年代数字视频应用的行业标准。如今,_ash转换器主要用作分级“流水线式”ADC中的构建模块。流水线架构的功耗和成本更低,并且能够以数百MHz的采样速率实现8至10位分辨率。因此,功耗较高的独立flash转换器主要用于采样速率超过1 GHz的6位或8位ADC。这些转换器通常采用砷化镓工艺设计。

图5 Flash型ADC原理框图 鉴于其作为高分辨率流水线ADC中构建模式的重要性,还需要了解基础flash转换的基本原理。Flash ADC(有时称为“并行”ADC)是速度最快的ADC,其中使用数个比较器。一个N位flash ADC包括2N个电阻和2N – 1个比较器,具体排列方式如图4所示。每个比较器均从电阻串获得基准电压,且每个基准电压要比链中的下一个基准电压大1 LSB。对于给定输入电压,低于某个点的所有比较器都将出现输入电压高于基准电压且逻辑输出为"1",而高于该点的所有比较器则都将出现基准电压高于输入电压且逻辑输出为"0"。因此,2N – 1个比较器输出在行为上类似于水银温度计,而该点的输出码有时称为“温度计”码。由于2N – 1个数据输出并不便于实际应用,因此需要经过解码器处理来产生N位二进制输出。 由于flash转换器采用了大量电阻和比较器且限制在低分辨率,因此如果达到较高速度,每个比较器就必须以相对较高的功耗水平运行。因此flash ADC的问题包括分辨率有限、因使用大量高速比较器(尤其是采样速率超过50 MSPS时)而导致功耗较高和相对较大(因此成本较高)的芯片尺寸。此外,基准电阻链的电阻必须保持在较低水平,以便向快速比较器提供足够的偏置电流,因此基准电压源必须提供较大的源电流(通常大于10 mA)。 4、计数ADC 计数ADC虽然不太适合高速应用,但却是高分辨率低频应用的理想之选,特别是结合使用双斜式积分、三斜式积分、四斜式积分等技术时。

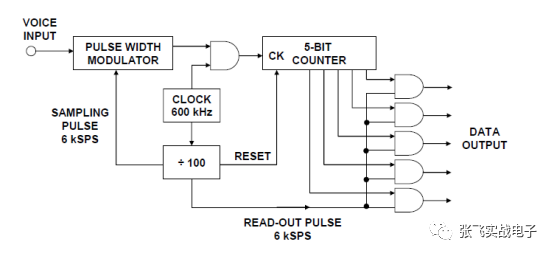

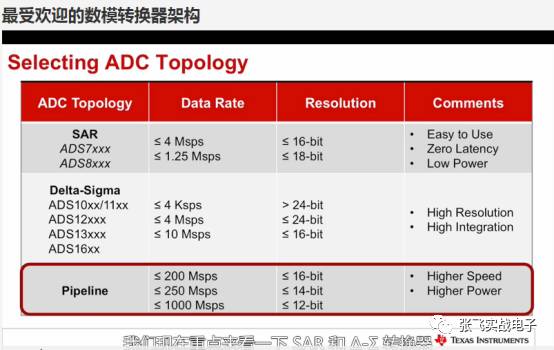

图6 计数ADC技术的基本原理是利用一个采样脉冲对模拟信号进行采样,然后设置一个R/S触发器,同时启动一个受控斜坡电压。该斜坡电压与输入进行比较,当二者相等时,就会产生一个脉冲以复位R/S触发器。触发器的输出是一个脉冲,其宽度与采样时刻的模拟信号成正比。该脉宽调制(PWM)脉冲控制一个选通振荡器,选通振荡器输出的脉冲数量代表模拟信号的量化值,通过一个计数器很容易将该脉冲串转换成一个二进制字。Reeves的系统使用600 kHz的主时钟,100:1分频器产生6 kHz的采样脉冲。该系统采用5位计数器,因而采样脉冲之间的100个脉冲中的31个脉冲代表一个满量程信号。显然,可以将该计数扩展到更高的分辨率。 ADC的重要参数及选型 关键词:分辨率、精度、采样率、功耗、价格 如图6所示为TI官方的一张ADC指标图

图7 小结 简单的对各类ADC做一个概括 SAR:分辨率中等( |

【本文地址】