Quartus实现寄存器:同步复位+异步复位 |

您所在的位置:网站首页 › vhdl同步复位和异步复位的区别 › Quartus实现寄存器:同步复位+异步复位 |

Quartus实现寄存器:同步复位+异步复位

|

文章目录

一、Visio图示二、代码1. rtl代码2.RTL Viewer3.测试文件

三、仿真结果

一、Visio图示

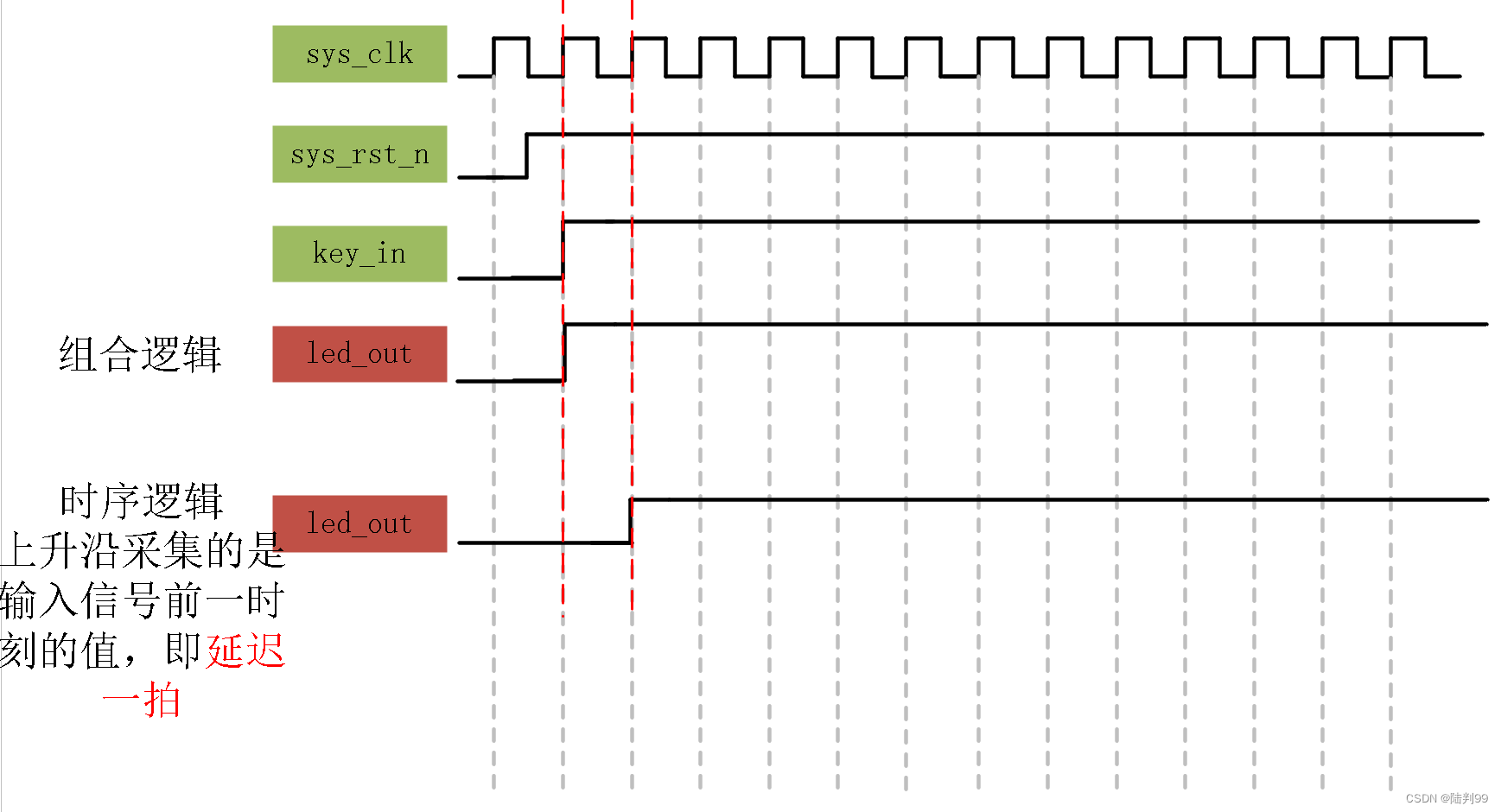

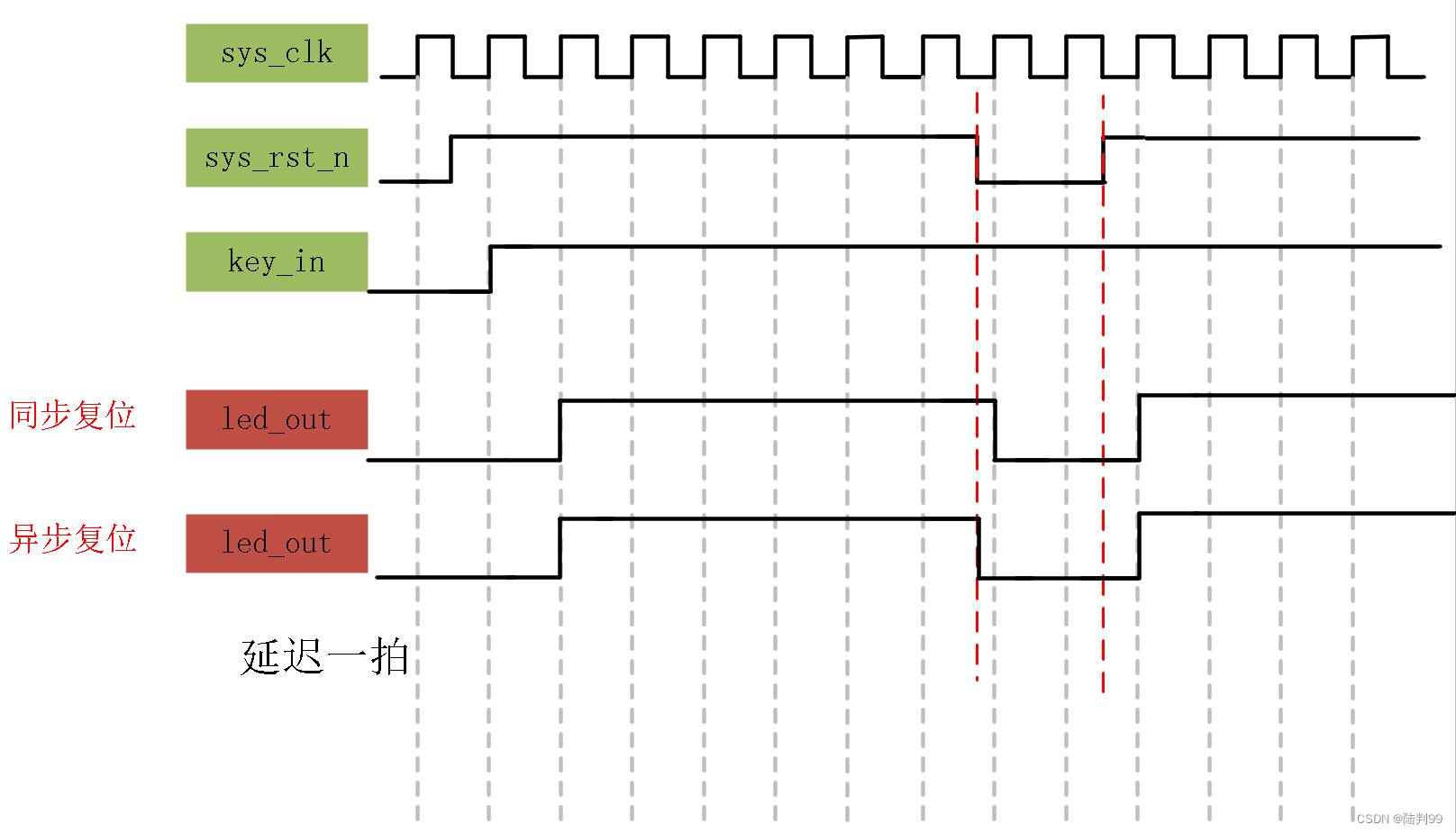

同步复位和异步复位都存在于时序逻辑中,与组合逻辑相比对毛刺有屏蔽作用。 当复位为高电平时,组合逻辑的结果是其输入,时序逻辑的输出需参考上升沿,此时红色虚线处的key_in为高电平,故时序逻辑的输出仍为高电平,这就解释了为什么时序逻辑与组合逻辑相比对毛刺有屏蔽作用。 代码如下(示例): module flip_flop ( input wire sys_clk,//时钟信号频率50MHz input wire sys_rst_n, input wire key_in, output reg led_out ); /* //同步复位 always@(posedge sys_clk) if(sys_rst_n==1'b0)//复位信号低电平有效 led_out |

【本文地址】

公司简介

联系我们

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |

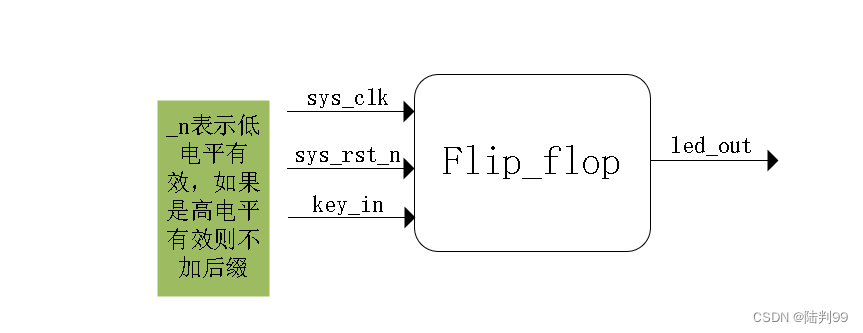

图1 寄存器输入输出引脚

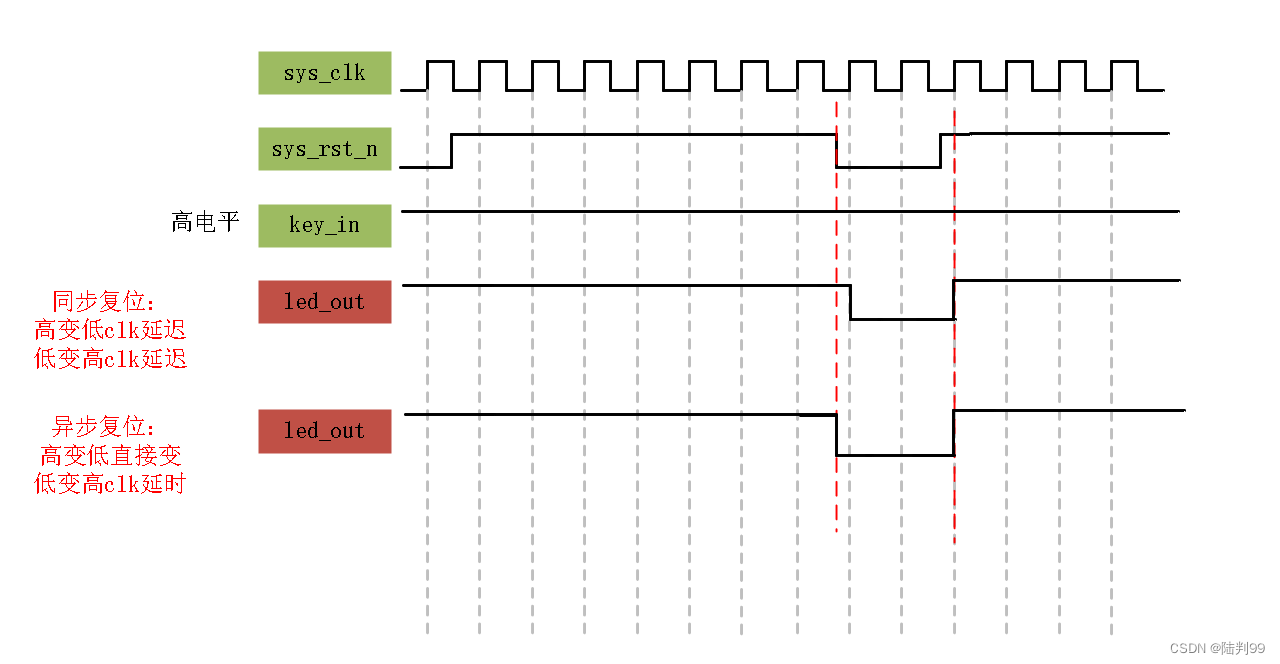

图1 寄存器输入输出引脚  图2 输入为高电平-例1

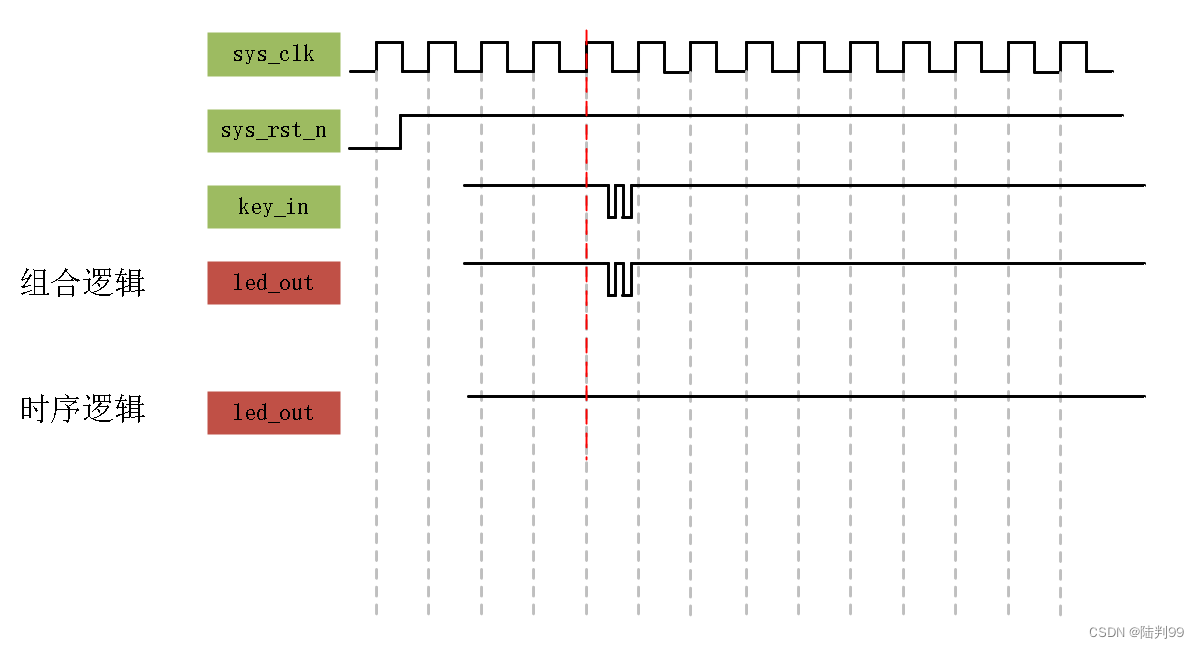

图2 输入为高电平-例1 图3 组合逻辑和时序逻辑的区别

图3 组合逻辑和时序逻辑的区别 图4 时序逻辑延迟一个周期

图4 时序逻辑延迟一个周期  图5 输入为高低电平交错-例2

图5 输入为高低电平交错-例2