| 在Artix7下测试并仿真DDR3模块 | 您所在的位置:网站首页 › artix › 在Artix7下测试并仿真DDR3模块 |

在Artix7下测试并仿真DDR3模块

|

Ref:UG586 框图

时钟说明: DDR3的时钟为400M,来源于DDR3 IP核分配。DDR3 IP核的时钟为200M,来源于晶振通过PLL分频得到。用户时钟(Ctrl)为100M,来源于DDR3 IP核分配。

Ctrl为用户编辑模块,主要功能就是简化MIG_IP核的用户接口以及配置成用户所需要的端口信号。 先介绍下DDR3的接口: ddr_addr DDR3的行列地址 ddr_ba DDR3的bank地址 ddr_cas_n ddr_ras_n ddr_we_n 命令控制 ddr_ck ddr_ck_n 差分时钟 ddr_dm 数据输入屏蔽 ddr_o_dt 片上终端使能,用于使能和禁止片内终端电阻 ddr_reset_n DDR3复位 ddr_dqs ddr_dqs_n 数据同步信号 ddr_dq 传输数据 然后就是用户接口:

注:时钟比例为4:1,突发长度为8. 1 a7_ddr3_wr

A7_ddr3_wr框图 信号说明: 信号 方向 说明 Ui_clk i 100M时钟,由MIG_IP提供。 A7_wr_start i 开始写标志,1个脉冲信号。拉高代表ddr3写开始。 A7_wr_bl i 写0-64个128bit的数据。 A7_wr_init_addr i 写ddr3的初始地址。 App_rdy i 读写请求。 A7_wdf_rdy i 写请求。 A7_wr_data i 写数据。 A7_wr_mark i 写数据过滤。

A7_ddr3_信号时序图 开始写的时候,我们需要给一个A7_wr_start的脉冲信号,告诉FPGA开始写,并同时给出写突发长度a7_wr_bl和写初始地址a7_wr_init_addr。随后拉高写标志wr_flag,表示写正在进行。其他信号可在时序图分析,不在叙述。 2 a7_ddr3_rd

A7_ddr3_rd读 读ddr3和写ddr3类似,都需要一个flag来启动FPGA。 读出来的数据会伴随一个valid信号,我们可以把这个信号当成数据写使能把数据存到fifo中。

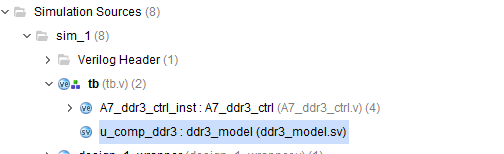

DDR3读时序 1.3 仿真 1.3.1 逻辑仿真逻辑仿真的时候我们需要把DDR3的sv文件添加到tb文件里面。

这样就相当于ddr3控制器和ddr3硬件连接了。

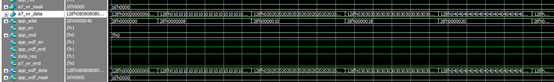

DDR3在工作之前会进行初始化。当信号init_calib_complete信号拉高的时候代表ddr3初始化成功。

在tb文件里面设置往ddr3里写的数为:从0开始,然后每8bit+1.如图所示。然后看读出来的数据对不对。

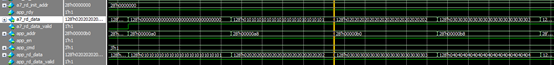

如图,读出来的数据和写进去的数据一样,说明成功。

条件有限,时间有限,硬件就不测试了。

欢迎各位一起学习讨论, 博主QQ:1435197677 |

【本文地址】