| 数字逻辑电路设计例化模块输入输出,何时用reg,何时用wire? | 您所在的位置:网站首页 › 模块实例化子模块 › 数字逻辑电路设计例化模块输入输出,何时用reg,何时用wire? |

数字逻辑电路设计例化模块输入输出,何时用reg,何时用wire?

|

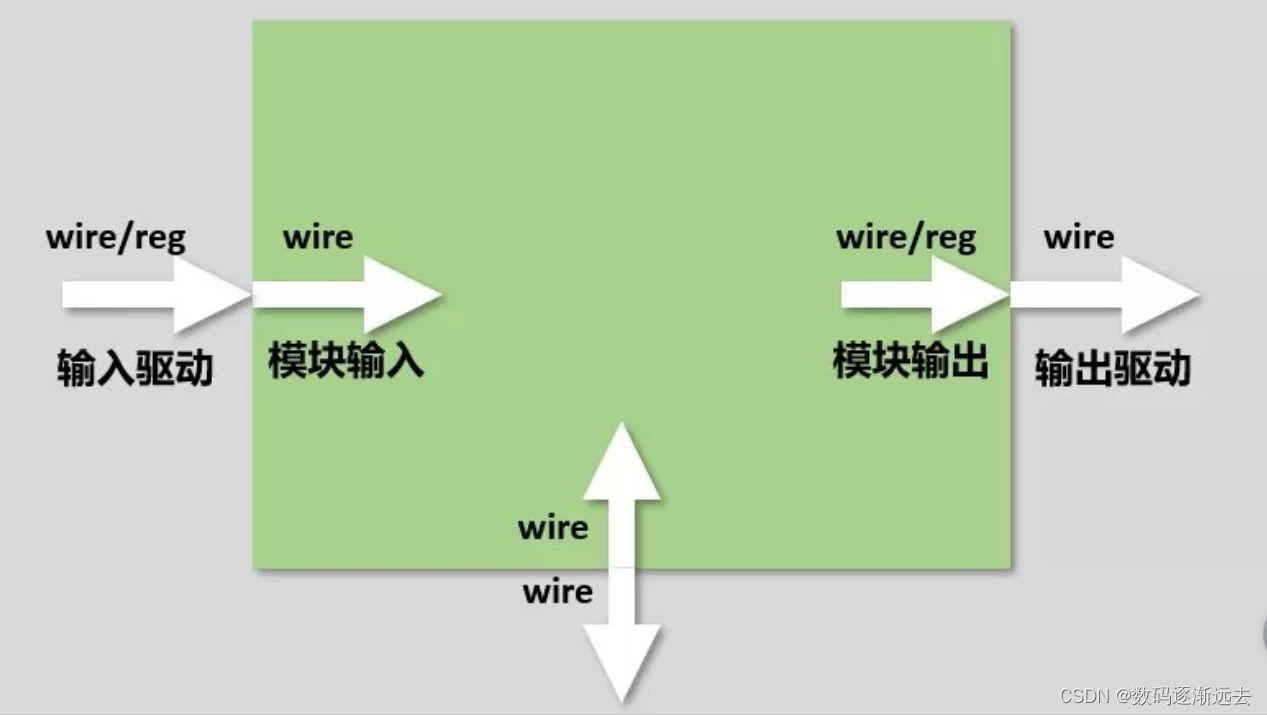

初学者应该总会遇到这个问题,许多资料都介绍的是: reg 寄存器类型可以存储数据,wire 是一根线,不能存储保持数据,是如此,但是在例化模块,或者调用通用的fifo模板,算法模板时候,难免经常连线,用寄存器打拍~~~ 下图中,绿色部分是子模块,灰色部分是顶层的模块,这里的reg和wire使用,体现了verilog语法的设计思想: 工作的子模块,需要立刻感受到外界的输入信号变化,所以需要使用wire 型的数据;如果使用reg型的数据,则外部模块如果给到reg型数据,则必须打拍,显然,子模块的优先级是较低的。 工作的子模块的输出,则可以使用wire和reg,这里和顶层模块输入到子模块是对应的; 同样的,顶层接收子模块的输出信号,也需要wire,需要立刻感受到子模块的输出信号变化; 总之,模块内部进去的信号必须是wire,输出给别的模块的wire和reg类型都可以。

|

【本文地址】

公司简介

联系我们