| FPAG | 您所在的位置:网站首页 › 黑金fpga › FPAG |

FPAG

|

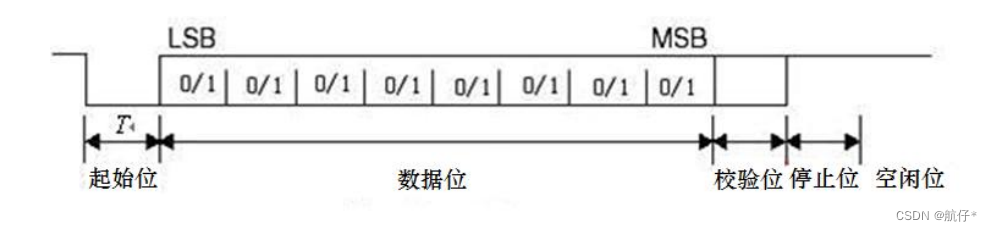

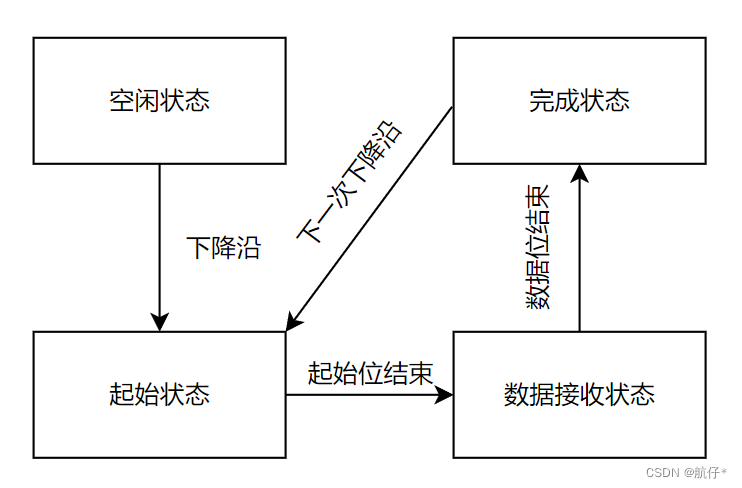

UART实现-黑金fpga开发板案例解析 uart 异步串口通讯 无需时钟线,俩根线一跟复制发数据一根负责收数据。 具体的时序如下图1: 可以看到 当数据线由高位变为地位时,即遇到一个下降沿时刻,表示开始这一次数据开始发送/接受,然后的高低电平表示数据位,一般是7-8个数据位,一般为8个,即一个字节,并可以添加校验位与停止位。 波特率介绍,由于uart通讯,使用单线单独进行数据传输,所有需要保证发送端与接收端能正常通讯,需要对信号进行约束,简单来说,就是对信号的采样频率进行设定。 当设置波特率为 115200 的时候,如果时钟信号时 50Mhz,这里,数据的一个位的高低电平持续时间应该时 50_000_000 / 115200 这么多个时钟,这样就可以约定发送与接收端,相隔一定的时间对信号线进行采样,得到的每位的高低电平表示这位的数据。 程序设计包括收和发的设计,使用状态机的思想进行程序设计 接收模块设计

整体的设计思路保持在一个always语句块里,只对一个reg变量进行赋值。 构造状态机的状态常量 localparam S_IDLE = 1; localparam S_START = 2; //start bit localparam S_REC_BYTE = 3; //data bits localparam S_STOP = 4; //stop bit localparam S_DATA = 5;构造状态机的状态变量进行状态切换 reg[2:0] state; reg[2:0] next_state; always@(posedge clk or negedge rst_n) begin if(rst_n == 1'b0) state |

【本文地址】

公司简介

联系我们

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |