|

一、建立工程

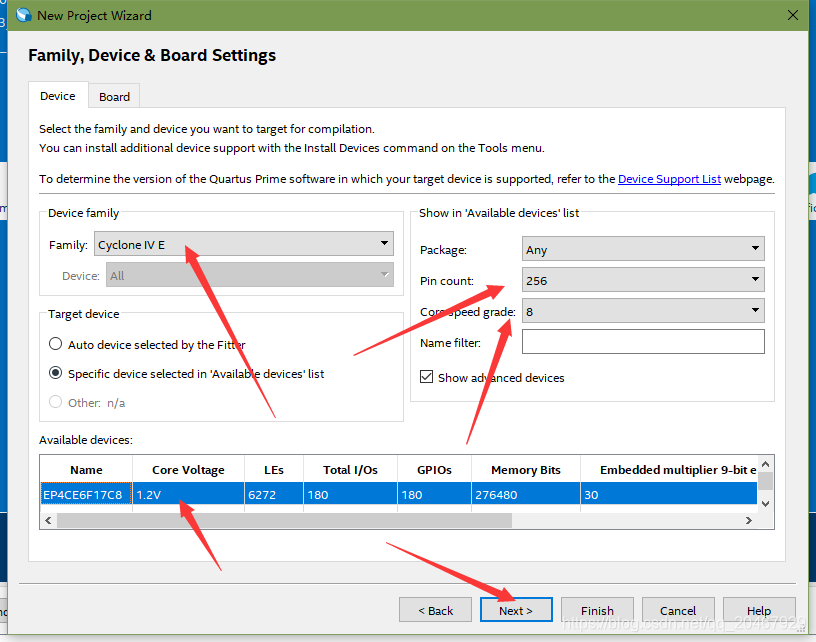

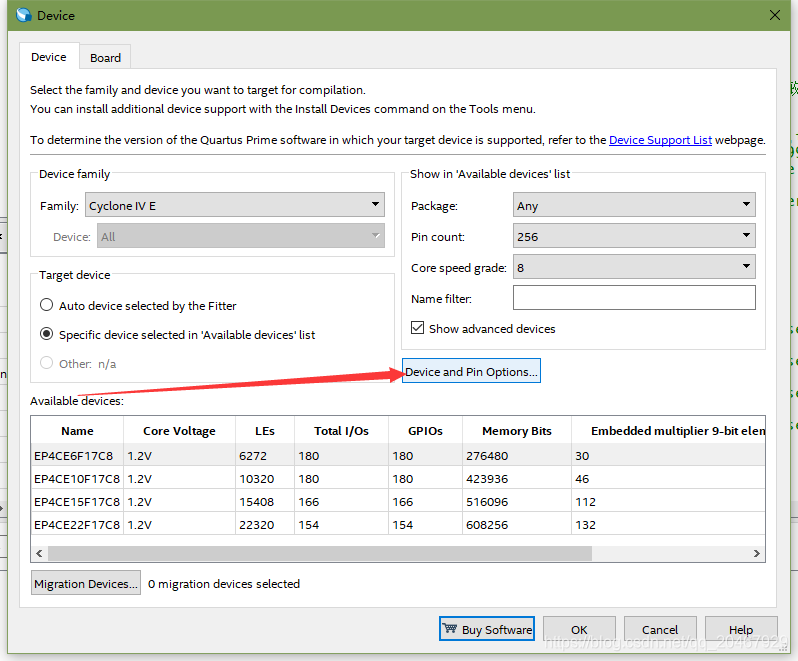

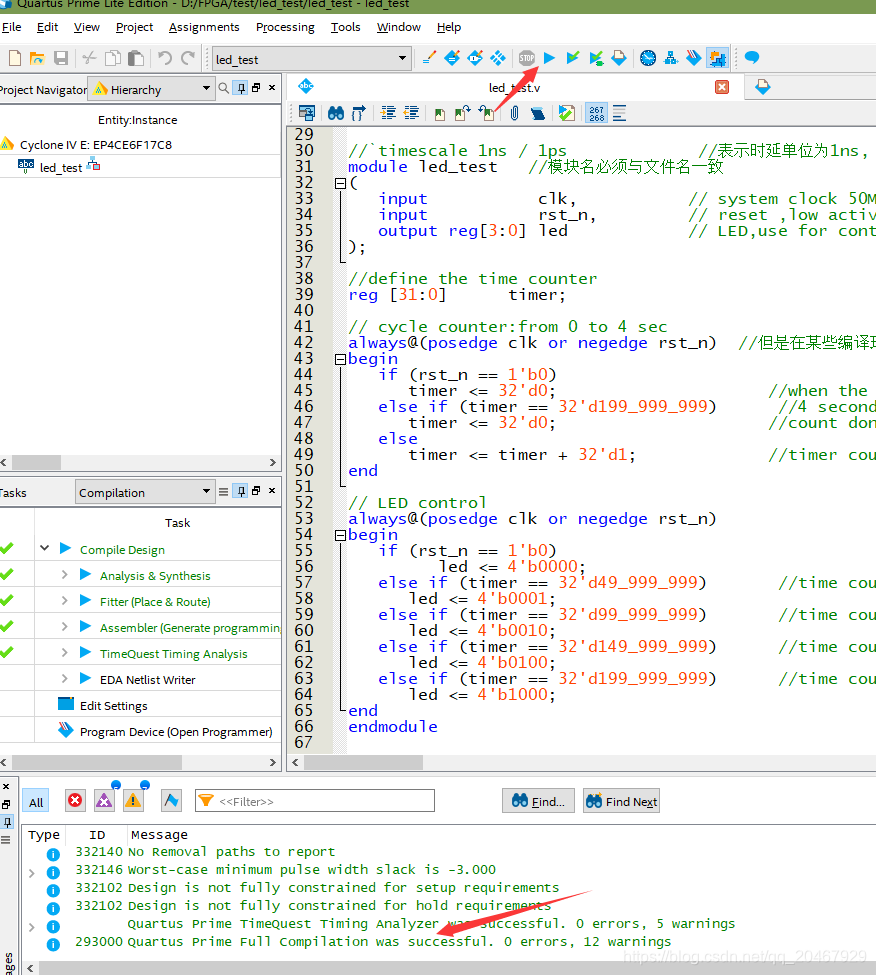

设置工程位置、工程名: 设置工程位置、工程名:   如果已经把写好的HDL放入设置的文件夹则可以添加到工程,否则下一步: 如果已经把写好的HDL放入设置的文件夹则可以添加到工程,否则下一步:  设置对应的FPGA类型、管脚数、速度等级,选择对应的FPGA(根据自己开发板)型号: 设置对应的FPGA类型、管脚数、速度等级,选择对应的FPGA(根据自己开发板)型号:   根据自己的喜好选择对应的HDL编程语言,新建源文件: 根据自己的喜好选择对应的HDL编程语言,新建源文件:  编写源文件后保存,文件名要和module名一致: 编写源文件后保存,文件名要和module名一致:  设置没用到的管脚为三态输入: 设置没用到的管脚为三态输入:  设备界面,若是创建工程时没有设置对应的FPGA类型,型号等,可在此设置,现配置引脚选项: 设备界面,若是创建工程时没有设置对应的FPGA类型,型号等,可在此设置,现配置引脚选项:  未用到的管脚设置为三态输入: 未用到的管脚设置为三态输入:  将多用途的引脚设置为普通I/O: 将多用途的引脚设置为普通I/O:  将电压设置为3.3V,设置之后点OK退出: 将电压设置为3.3V,设置之后点OK退出:  设置引脚映射: 设置引脚映射:  在Location处设置开发板对应的引脚(可手动输入标志尾号,软件会自动补全,比如输入E1,软件会识别为PIN_E1),设置完之后点右上角的×进行关闭即可(自动保存): 在Location处设置开发板对应的引脚(可手动输入标志尾号,软件会自动补全,比如输入E1,软件会识别为PIN_E1),设置完之后点右上角的×进行关闭即可(自动保存):  开始编译,并等待编译通过: 开始编译,并等待编译通过:

二、下载程序

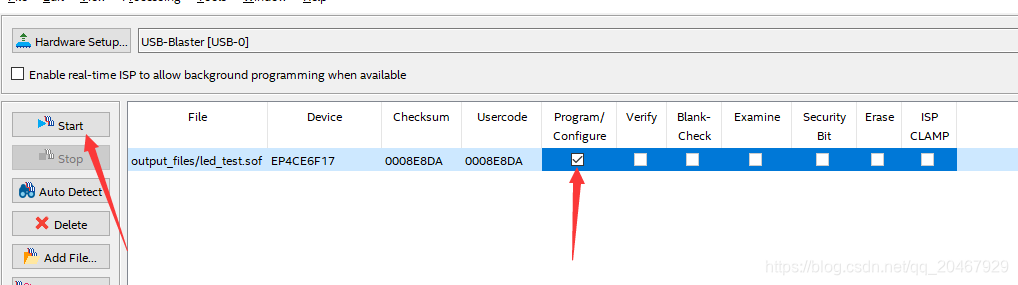

开发板连到电脑上,设置下载器(我用的是USB-Blaster): 开发板连到电脑上,设置下载器(我用的是USB-Blaster):  选择自动识别FPGA型号: 选择自动识别FPGA型号:  双击箭头处添加可执行文件: 双击箭头处添加可执行文件:   下载(sof可执行文件只在当次上电有效,重启开发板程序会丢失,用于调试): 下载(sof可执行文件只在当次上电有效,重启开发板程序会丢失,用于调试):

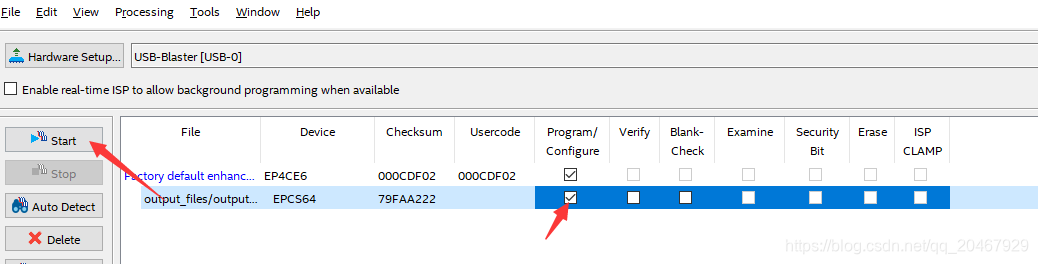

三、下载JIC文件(断电程序不丢失)

选择对应的FPGA对应型号: 选择对应的FPGA对应型号:  JIC文件输出位置、名称,一般不改动: JIC文件输出位置、名称,一般不改动:  添加FPGA设备型号: 添加FPGA设备型号:  根据自己开发板对应型号添加: 根据自己开发板对应型号添加:  添加sof可执行文件以进行转换: 添加sof可执行文件以进行转换:    生成完成后,回到下载界面,将File文件替换为jic可执行文件: 生成完成后,回到下载界面,将File文件替换为jic可执行文件:  首先擦出一下flash: 首先擦出一下flash:  Flash 擦除之后再下载程序,改程序会存储在Flash中以进行断电保存(下载后需要重新上电才能运行程序): Flash 擦除之后再下载程序,改程序会存储在Flash中以进行断电保存(下载后需要重新上电才能运行程序):

|