| AD9361 官方例程 | 您所在的位置:网站首页 › 飞机adc › AD9361 官方例程 |

AD9361 官方例程

|

AD936x 系列快速入口 SW部分在: AD9361 官方例程详解(一) 和 AD9361 官方例程详解(二) MSK通信,物理层:MSK调制,MSK接收 正在进行 OFDM调制(一)… HDL部分详细内容在 AD9361 官方例程详解(未完成) 文章目录 一、ADI官方资料1.1 介绍1.2 下载 和 使用1.3 相关资料 二、HDL 和 sw2.1 构建HDL2.2 sw2.2.1 创建项目2.2.2 项目配置 一、ADI官方资料 1.1 介绍HDL参考设计介绍:AD9361 HDL Reference Designs 无操作系统介绍:AD9361 No-OS Software 1.2 下载 和 使用HDL下载:Download HDL 在Vivado中构建HDL:Building HDL No-OS下载:Download No-OS 1.3 相关资料ADI参考设计HDL用户指南 AD9361 无操作系统文档介绍 (包含驱动程序、头文件、项目等):AD9361 Doxygen Documentation,例如下图为文档中项目部分讲解框图,可以帮助我们加快学习 首先根据HDL发行说明选择Vivado版本,最新的可能bug比较多点,我选用得是hdl_2019_r1,这个版本需要Vivado 2018.3,在Download HDL中选择hdl_2019_r1分支,如下图所示,下载好zip文件  export PATH=$PATH:/cygdrive/E/xilinx2018/Vivado/2018.3/bin

E/xilinx2018/Vivado/2018.3/bin 是vivado的安装路径

export PATH=$PATH:/cygdrive/E/xilinx2018/Vivado/2018.3/bin

E/xilinx2018/Vivado/2018.3/bin 是vivado的安装路径

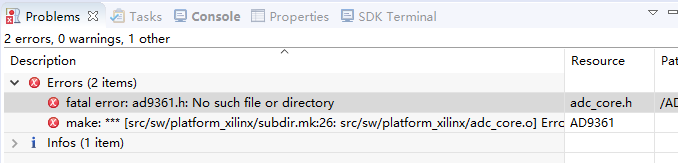

利用which git ,which make,which vivado 进行测试,如果设置正确,这些命令将返回有效路径。 make首先构建所有库,然后构建项目,等10几分钟,如下图所示,构建完成,项目构建成功后,hdf文件应位于“ sdk”文件夹中 大部分情况下仅靠HDL无法做任何有用的事情,需要在处理器上运行软件才能进行设计,ADI提供两种方案,Linux和No-OS,我们用No-OS方法。 2.2.1 创建项目No-OS驱动程序在Download No-OS下载和HDL相匹配的2019_R1分支 在vivado中启动SDK 2018.3,然后创建一个新的应用程序项目:文件→新建→应用程序项目。 No-OS 解压后,将~:\AD9361\no-OS-2019_R1\ad9361 文件夹下的sw文件全部复制到 SDK 中工程中的src 文件中 ~:\AD9361\hdl-hdl_2019_r1\projects\fmcomms2\AD9361\fmcomms2_zc706.sdk\AD9361\src 根据所需设备配置,从config.h头文件中取消注释(没正确取消注释,程序不能正确运行) //#define CONSOLE_COMMANDS #define XILINX_PLATFORM //#define ALTERA_PLATFORM //#define FMCOMMS5 //#define ADI_RF_SOM //#define ADI_RF_SOM_CMOS #define ADC_DMA_EXAMPLE //#define ADC_DMA_IRQ_EXAMPLE #define DAC_DMA_EXAMPLE //#define AXI_ADC_NOT_PRESENT //#define TDD_SWITCH_STATE_EXAMPLE//#define CONSOLE_COMMANDS :可选,使用一些控制命令来配置或获取AD9361器件当前信息,可以通过连接到开发板的UART来传输命令 #define XILINX_PLATFORM: 我使用的是 xilinx 设备 取消注释 //#define ALTERA_PLATFORM :不取消 //#define FMCOMMS5 : 我的是FMCOMMS3,不取消 //#define ADI_RF_SOM 和 //#define ADI_RF_SOM_CMOS :不取消,取消注释时,xo-disable-use-ext-refclk-enable为1,会使用外部refclk #define ADC_DMA_EXAMPLE :取消,可以使用adc_capture函数通过DMA获取IQ数据 //#define ADC_DMA_IRQ_EXAMPLE :不取消,先不涉及中断部分 #define DAC_DMA_EXAMPLE: 取消注释,官方例程的正弦波数据写入DDR,通过DMA将数据传给AD9361,不取消时使用DDS产生数据传给AD9361 //#define AXI_ADC_NOT_PRESENT:不取消,取消后不能对AD9361发数据和取数据 //#define TDD_SWITCH_STATE_EXAMPLE:不取消,例程默认是FDD,取消后是AD9361的TDD模式ensm转移例程 sw文件复制到src文件中 ,sdk会自动编译,可能会报错,如下所示 首先可以在SDK中对Zynq的FPGA部分进行编程,通过单击Xilinx → Program FPGA 来对FPGA进行编程。 Debug Type :Standalone Application Debug Initialization file :ps7_init.tcl Run ps7_init :勾选 Run ps7_post_config options :勾选 Program FPGA :可以勾选,对FPGA部分进行编程 Application部分 定义当前的项目名称和应用程序可执行文件 有需要的话可以在 SDK Terminal 使用UART捕获示例程序AD9361的输出(详见 AD9361 官方例程详解(二)) |

【本文地址】

自定义或修改 AD9361 设备驱动(介绍了No-OS 中主函数的参数含义):AD9361 Device Driver Customization

自定义或修改 AD9361 设备驱动(介绍了No-OS 中主函数的参数含义):AD9361 Device Driver Customization Windows不支持GNU Make,Windows系统最好使用Cygwin来构建,安装Cygwin时,选择“ make”和“ git”软件包,后续要用。不推介手动TCL构建,因为构建项目前,它所需的库也必须构建,太多了,所需的库构建不全会报错,而且特别费时间。

Windows不支持GNU Make,Windows系统最好使用Cygwin来构建,安装Cygwin时,选择“ make”和“ git”软件包,后续要用。不推介手动TCL构建,因为构建项目前,它所需的库也必须构建,太多了,所需的库构建不全会报错,而且特别费时间。 在cygwin里将路径切换到解压的HDL路径下面,再执行make命令

在cygwin里将路径切换到解压的HDL路径下面,再执行make命令 在文件路径中找到xpr文件,在Vivado中打开

在文件路径中找到xpr文件,在Vivado中打开

Project name : 项目名称 use default location : 使用默认地址 OS Platform :单板 还是 Linux Hardware Platform :使用通过Vivado生成的硬件平台规范文件 system_top.hdf processor :两个ARM核中的ARM 0 Language :C语言 Board Support Package : 板级支持包 ,新建 next ,选择“空应用程序模板”,然后单击“完成”,如下图所示,

Project name : 项目名称 use default location : 使用默认地址 OS Platform :单板 还是 Linux Hardware Platform :使用通过Vivado生成的硬件平台规范文件 system_top.hdf processor :两个ARM核中的ARM 0 Language :C语言 Board Support Package : 板级支持包 ,新建 next ,选择“空应用程序模板”,然后单击“完成”,如下图所示,  需要根据自己的需求正确设置 Stack 和 Heap 的大小,如局部变量较多,增大Stack,某些应用程序(例如FMCOMMSx)需要增加HEAP大小才能进行动态内存分配,官方建议使用Microblaze处理器时,确保HEAP大小至少为0x100000。Stack 和 Heap 初始大小都为 0x2000。

需要根据自己的需求正确设置 Stack 和 Heap 的大小,如局部变量较多,增大Stack,某些应用程序(例如FMCOMMSx)需要增加HEAP大小才能进行动态内存分配,官方建议使用Microblaze处理器时,确保HEAP大小至少为0x100000。Stack 和 Heap 初始大小都为 0x2000。 src文件夹中存在多个文件夹,头文件路径包括文件夹的所有路径:工程右击 →在C/C++ Build Settings → Tool Settings →ARM v7 gcc compiler → Directories 部分,然后添加以下文件夹的路径。

src文件夹中存在多个文件夹,头文件路径包括文件夹的所有路径:工程右击 →在C/C++ Build Settings → Tool Settings →ARM v7 gcc compiler → Directories 部分,然后添加以下文件夹的路径。

无错误后sw项目构建完成,可以将软件部分的程序下载到ARM中运行调试 。

无错误后sw项目构建完成,可以将软件部分的程序下载到ARM中运行调试 。 对FPGA进行编程之后,再选择Run → Run Configurations…,创建一个新的Run Configuration,在Run Configuration窗口中,选择Xilinx C / C ++ application (System Debugger),双击或者右击New,详细过程可见 zynq zc706 JTAG调试 部分。

对FPGA进行编程之后,再选择Run → Run Configurations…,创建一个新的Run Configuration,在Run Configuration窗口中,选择Xilinx C / C ++ application (System Debugger),双击或者右击New,详细过程可见 zynq zc706 JTAG调试 部分。  之后Target Setup 配为

之后Target Setup 配为

完成run configuration后,单击Run按钮来启动

完成run configuration后,单击Run按钮来启动 波特率: 115200bps 数据: 8位 奇偶校验:无 停止位: 1位 流量控制:无

波特率: 115200bps 数据: 8位 奇偶校验:无 停止位: 1位 流量控制:无