| 利用FPGA实现UDP网络高速可靠传输 | 您所在的位置:网站首页 › 通信udm › 利用FPGA实现UDP网络高速可靠传输 |

利用FPGA实现UDP网络高速可靠传输

|

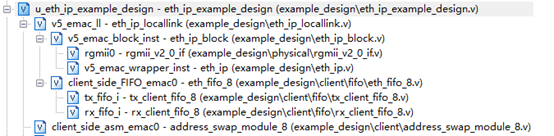

利用FPGA实现UDP网络高速可靠传输 FPGA数据处理中常用的一些IP核有网口ETH核、DDR核、CORDIC核、DDS核、加法器、乘法器、滤波器IP、FFT等IP核,这些IP核熟练使用能减少很多工作量和提高代码的稳定性。这些IP核的配置比较简单,但是如何正确使确是个很大的问题。最近一直在用网口、DDR、DDS、CORDIC这些IP。一下子很难把这些IP的用法全部写完,后续会一个一个的去介绍。 1、网口IP的框架结构和配置验证 我用的是XILINX的Virtex-5系列的芯片,这里就以这个配置为例。这里些的配置方法主要是参考UG340这个官方文档。 首先要对这个Tri-Mode Ethernet MAC IP有个全局的直观把握,这样对理解IP核的层次核代码会有一个很好的指导。 从这个图来看,这是一个网口数据回环例程结构。从外到内可以分为四个层次: 1、外部接口,这里主要是IP核的输入输出以及时钟核复位接口。这里由于是回环传输的一个例程框架图,这个模块还包含Address Swap Module地址交换模块。 2、LocalLink wrapper模块,这部分其实就是把几个单独的模块例化到同一个模块下组成一个相对完备的功能。这里主要由两个大的模块组成,一个是收发的数据缓存FIFO,一个是MAC的数据收发转化的模块。 3、Block Level Wrapper 这层就是把第四层的两个核心模块进行例化。 4、MAC层,这个是网络IP的核心模块,这个主要是实现从PHY芯片接收到的数据IDDR核ODDR的转换和网络链路层(MAC层)协议的转换,这部分是整个IP核的核心。 上面这个结构能清晰的对网络Tri-Mode Ethernet MAC IP进行一个直观的描述,从上面可以看出数据的流向核各个模块的作用。具体到IP核的配置其实很简单。 这里面有三个选项,主要是选择共享接口和主机类型的选择,以及选择一个还是两个网口。 其中DCR设备控制寄存器,这个主要是通过总线桥对不同MAC进行控制。而在无特殊要求的时候一般选用NONE模式。 这部分一般是对输入输出的控制和对一些MAC地址进行过滤。 以上就是Tri-Mode Ethernet MAC IP的基本配置。 完成了基本的配置只是实现网络传输的一小部分,要想灵活的运用这个IP还需要对底层代码进行了解,明白各个模块的功能。 打开仿真源码并结合上面的结构框图可以清晰的看到IP的四层结构框架。 这部分代码需要仔细的去看看,看明白数据的流向,ODDR和IDDR的转化。其中最重要的就是接收和发送时钟的来源以及去向。就不细讲里面的代码了,这部分需要自己看呀,不然讲讲也没啥用。 |

【本文地址】

这部分主要是配置PHY的接口类型和传输速度。这个需要根据硬件情况进行配置。

这部分主要是配置PHY的接口类型和传输速度。这个需要根据硬件情况进行配置。