| FPGA设计编程(二) 8 | 您所在的位置:网站首页 › 译码器的电路原理是什么 › FPGA设计编程(二) 8 |

FPGA设计编程(二) 8

|

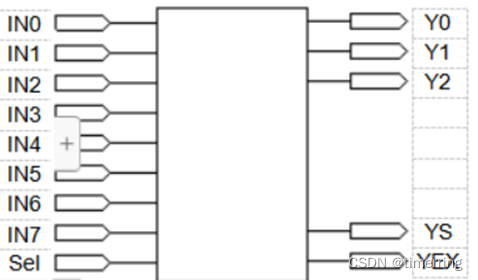

目录 【实验要求】 【实验软件工具】 【实验一】设计一个8-3线优先编码器(74LS148) 1. 实验内容与原理说明 2. 实验模块程序代码和激励代码 (1)设计模块代码 (2)激励模块代码 3. 波形仿真图 4.门级电路图 【实验二】设计一个3-8线译码器(74LS138) 1. 实验内容与原理说明 2. 实验模块程序代码和激励代码 (1)设计模块代码 (2)激励模块代码 3. 波形仿真图 4.门级电路图 【实验结果分析及思考】 【实验要求】 实验内容与原理说明(包括框图、逻辑表达式和真值表)。实验模块程序代码(设计模块Design Block)和激励代码(激励模块Test Bench)。仿真波形图。综合得到的门级电路图。实验结果分析及思考。每一次报告用Word文档提交,文件名:姓名_班级_第几次实验_学号。 【实验软件工具】 QuartusII;ModelSim SE. 【实验一】设计一个8-3线优先编码器(74LS148) 1. 实验内容与原理说明实验一为设计一个8-3线优先编码器,即可以将八个输入的编码,通过对于输入信号的分析,输出第几个信号是低电平。8线-3线优先编码器有8个输入端I0'~I7',低电平为输入有效电平;有3个输出端Y0'~Y2’,低电平为输出有效电平。此外,为了便于电路的扩展和使用的灵活,还设置有使能端S'、选通输出端Ys'和扩展端Yex'. 其所对应的情况如下: IN OUT 01111111 111 10111111 110 11011111 101 11101111 100 11110111 011 11111011 010 11111101 001 11111110 000 Else 000 该设计模块的实验框图如下:

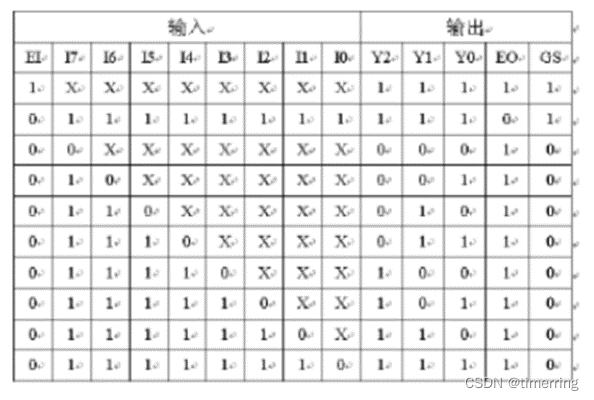

根据8-3线优先编码器可以列出其真值表如下:

|

【本文地址】

公司简介

联系我们