| 数字IC设计流程总结 | 您所在的位置:网站首页 › 芯片设计方案怎么写 › 数字IC设计流程总结 |

数字IC设计流程总结

|

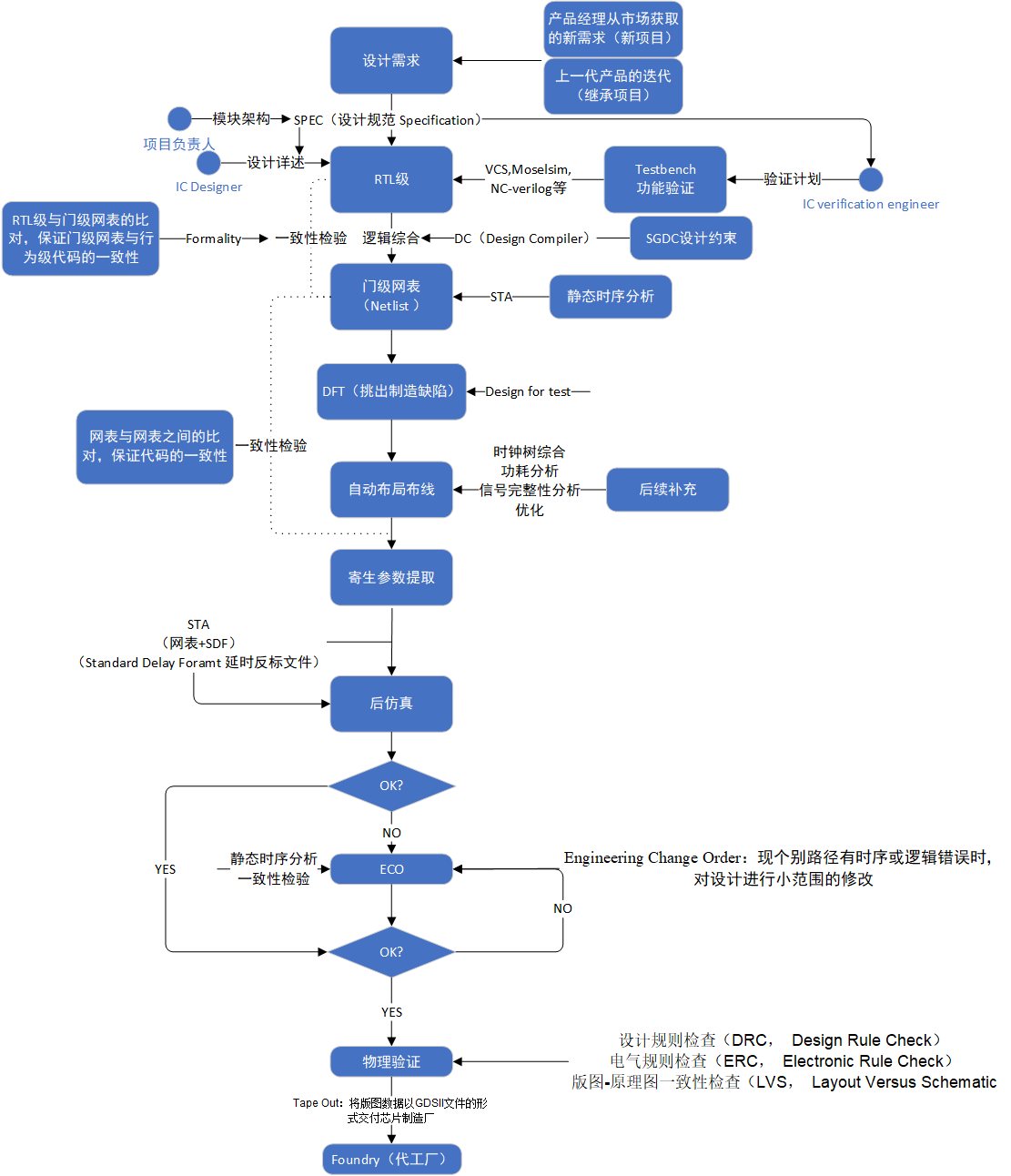

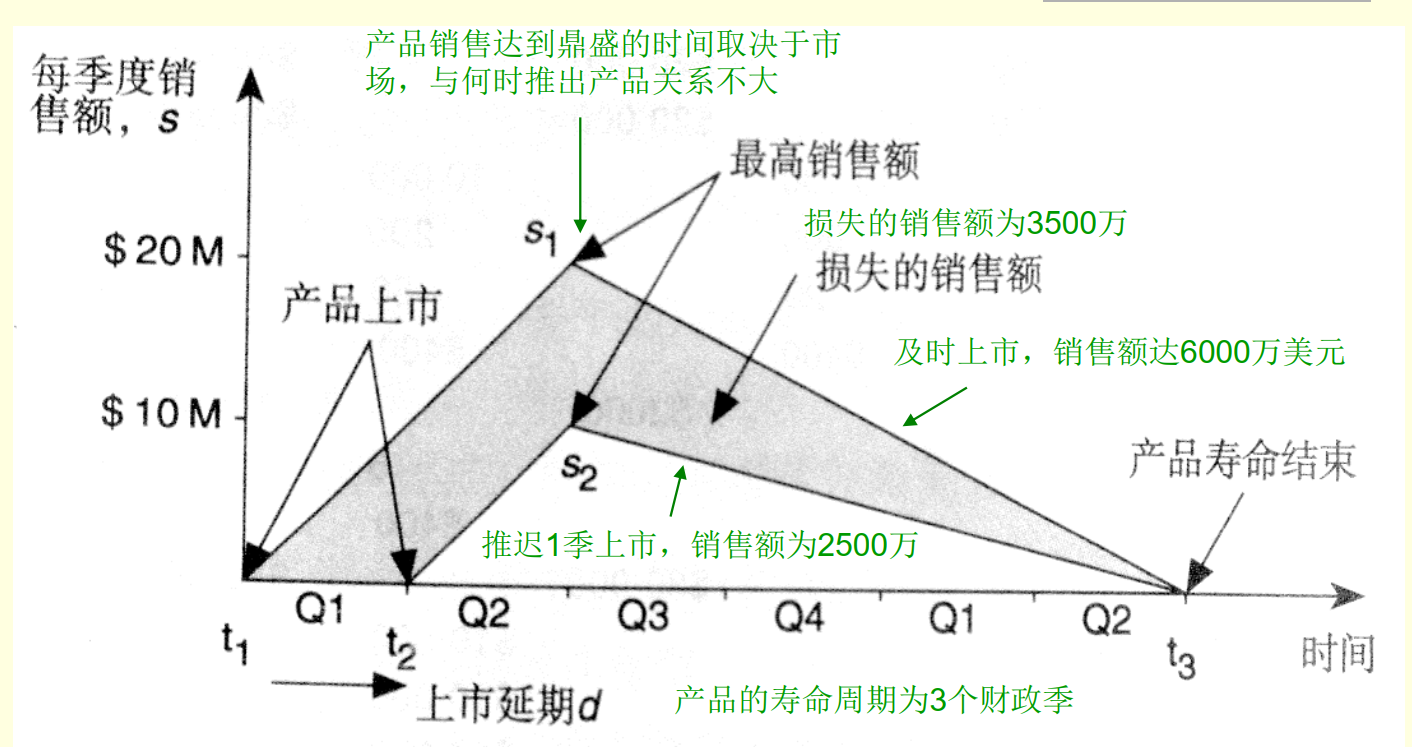

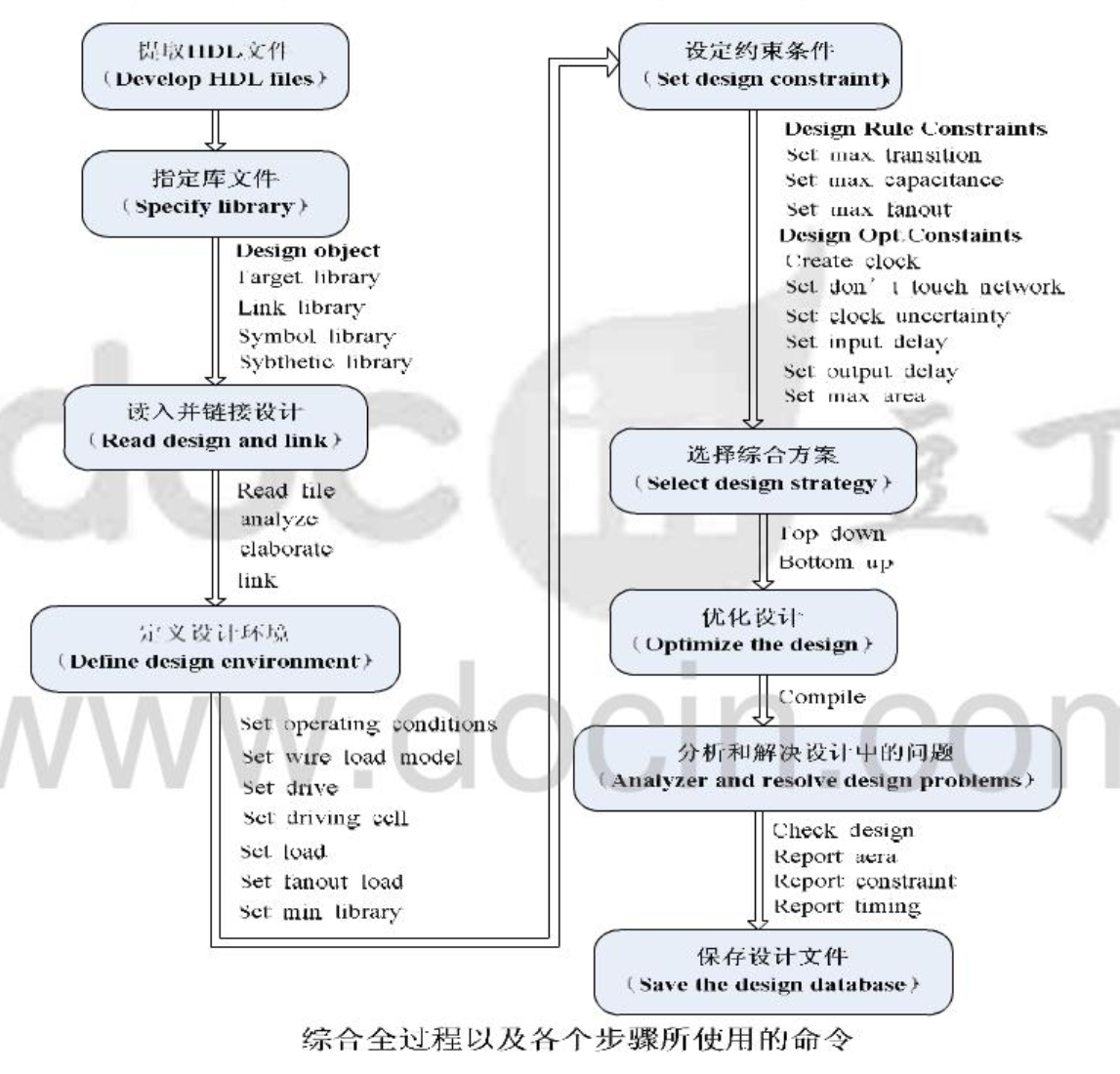

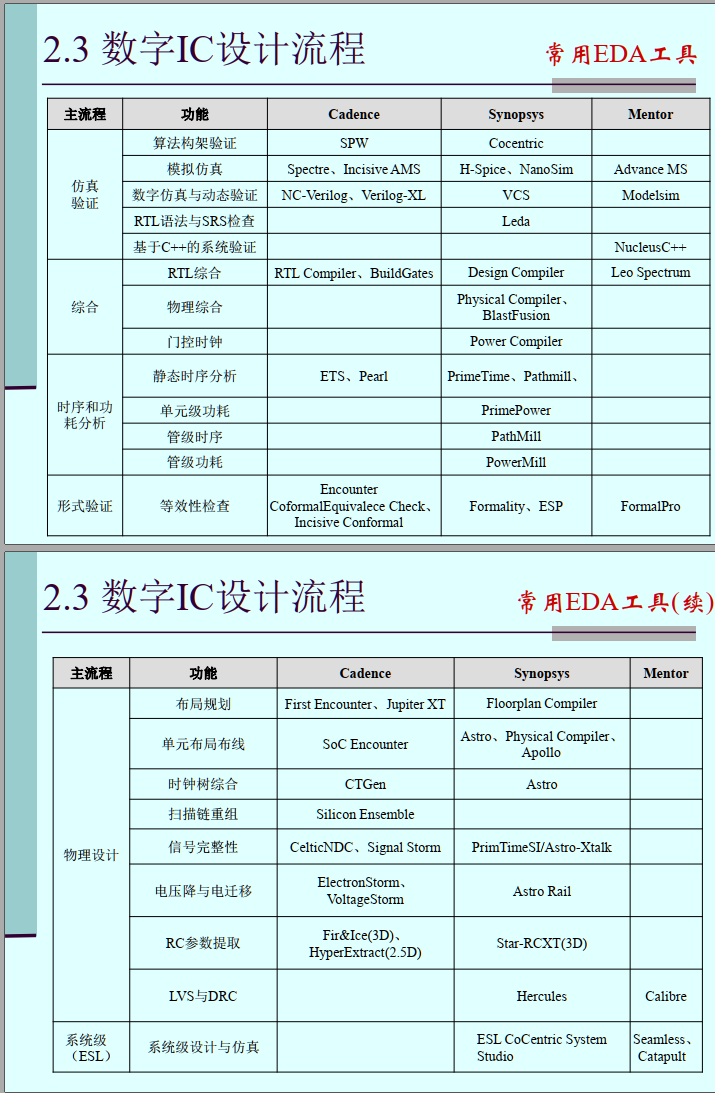

IC设计是一个很复杂漫长的过程,笔者以下图进行总结,其中后端总结的很模糊,后续了解学习后再进行补充。笔者会根据自己的理解,一步步的分享自己理解的设计流程。其中难免有问题错误,望同学老师指出,感谢!哔哩哔哩有对应的视频,视频放到博文结尾处。 文章目录 IC设计流程图设计需求设计规范(Design Specification)IC设计工程师IC验证工程师使用的工具 RTL级逻辑综合一致性检验 门级(STA)DFT布局布线P&RECO物理验证IC设计流程中使用的工具 IC设计流程图首先下面这张图是笔者总结的数字IC设计流程图。从设计需求到Tape-Out。下面会详细说明这张图的内容,后续也会持续修改更正。 首先是需求设计,一般的设计无非就是两个来源,一个是新的项目,需求来自市场,另外一个来自与继承项目的迭代。这两个均有产品经理(IC产品工程师)进行收集汇总,然后以给出设计需求。这里的设计需求只是一些技术指标,整体的功能。不涉及代码方面。其中产品经理需要了解市场未来的一个趋势,同时结合自家设计能力与时间,使得设计出来的芯片是符合市场大趋势的。 下图为庄老师PPT中的一张图,可以结合理解。 这个设计规范一般是由熟悉项目的工程师担任,需要对整体架构有一个很好的理解,模块划分,技术指标,实现细节都需要有一定的理解。同时将一个不规范的设计需求转变为规范的设计规格书。这个规格书同时需要交给设计工程师与验证工程师。这就到了模块级的设计了。 IC设计工程师IC设计工程师需要根据自己需要设计的模块,心里要有一个设计详述,描述自己的设计实现的方式,其实就是一个整理自己思路的一个过程,需要尽可能的详细,直观,尽可能简洁清楚的描述模块设计的方法。同时开始自己的coding,再结束后需要自己写一个简单的testbeach来进行测试,基本上没有及其愚蠢的问题交给验证工程师进行验证。 IC验证工程师IC验证工程师拿到设计规范以后需要进行一个验证周期的规划,同时提取验证点。构思验证方法,搭建验证环境,等设计工程师的代码实现一定的功能就可以开始验证了。这是一个反复迭代的过程。 使用的工具这里使用的工具一般是VSC+Verdi。综合+查看波形。VIM or GVIM文本编辑器。SVN or Git 版本管理工具。 RTL级RTL级别就是寄存器传输级,一般使用的语言是Verilog或者是VHDL,大多数是使用的verilog的。这一步也是很关键的一部分,主要由IC设计工程师来完成,目的是实现设计功能的正确性,同时保证可综合设计,代码可读性,低功耗设计,时序收敛,跨时钟域的处理…在实际工程中需要考虑的更多了。他的正确性由验证工程师保证。由SpyGlass的lint(代码质量)与CDC(跨时钟域)来进一步保证设计的正确性。 简单来说,其实就是两个东西,Timing与function。function我们由验证工程师检验,因此代码质量就体现在了时序上,因此虽然这里不需要做STA,但是后面步骤的STA的结果却是这一步你的代码质量的一种检验。静态时序分析只有在门级才可以进行分析,但是你的RTL就需要考虑到综合后的结果,好的RTL才能综合出好的电路。你不能指望工具帮你把及其差劲的代码综合成优秀的电路,这是不现实的。 逻辑综合DC逻辑综合主要是将RTL翻译成门级,一般这一步也就是后端与前端的分界了。这一步需要做的就是写一个设计约束。需要考虑一个PAP的折中。power Area Performance主要由SDC(约束)来体现。这里的设计约束是没有人来替你保证的。也没有工具来保证,因此这里算是一个比较依靠工程师经验的点。 下面的这张图展示了需要做的一些工作,具体的实现会在后续的DC篇中更完整的给出介绍。这里重点放在流程的梳理上。 一致性检验的目的是检验两次代码的一致性。简单来说哈,就是你前面的步骤保证了你的代码功能的正确性,但是你是如何知道将RTL级的代码转换为门级你的功能依然是正确的呢?这就需要使用Formality来保证你两次代码的一致性。 门级(STA)在门级这里需要进行一次静态时序分析,主要这里主要修的问题的setup的问题,至于hold的问题可以留给后端去修。主要是保证在你需要的时钟下的建立时间裕度是正的。reg-in,reg-out,组合逻辑是否过长等需要注意的地方,以及你的约束的悲观还是乐观,都会影响你的代码综合的结果与STA是否通过。使用的工具是PrimeTime DFT可测试性设计主要是用于量产时候,ATE测试机台的自测试,目的是为了保证在设计正确的前提下,制造过程中的问题以及定位设计的问题。快速定位问题。 布局布线P&R包括布局,时钟树综合,布线,参数提取等,然后进行后仿真。后仿真是加入了真实延时的仿真结果。一般很接近真实情况了。 ECO称之为工程更改指令Engineer Change Order。主要是进行一些小修小补,一般时间不会太长,一个星期以内就可以结束,然后进行物理验证。 物理验证物理验证主要是版图上的检查,检查自己的版图与代工厂要求之间有什么不一致的地方进行修改 IC设计流程中使用的工具下图来自庄奕琪老师的PPT 数字IC设计流程介绍 点击视频链接 |

【本文地址】