| 晶圆材料、钝化层及表面结构 | 您所在的位置:网站首页 › 芯片bump和pad › 晶圆材料、钝化层及表面结构 |

晶圆材料、钝化层及表面结构

|

对于减薄过、有背金或已经带有激光刻印的晶圆,必须采取保护措施,防止在此类区域镍金的沉积。保护材料种类及保护方式的选择,要视具体保护区域的材质和形貌而定,特别是背面带有金属层的硅基晶圆,要综合考虑金属层的成分及粗糙度的影响,其金属层如含有Ag会对某些保护材料有一定的排斥性。

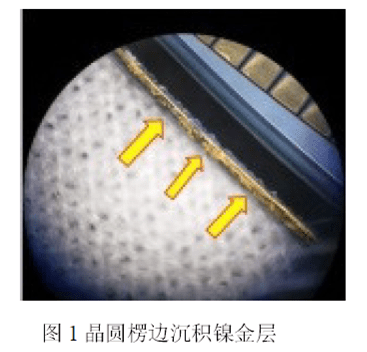

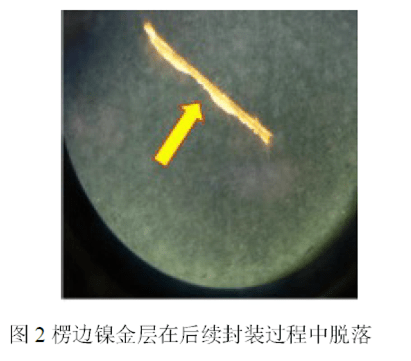

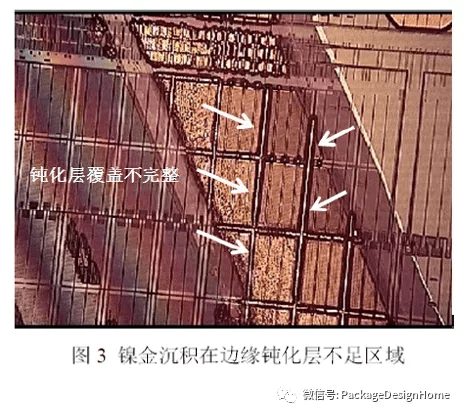

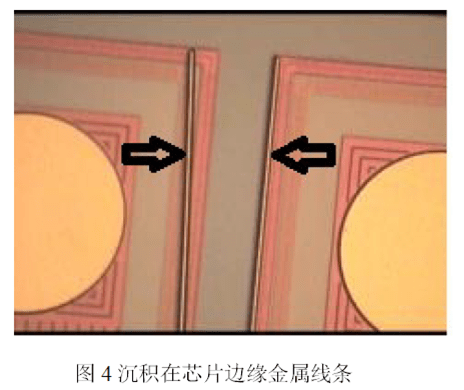

2.1.2其他材质晶圆 除了占比大的硅基晶圆外,其他一些具有特殊性能晶圆材料也可以通过化镀工艺在I/O金属垫上沉积镍金层。比如多用于射频器件的LiTaO3(钽酸锂)、LiNbO3(铌酸锂)和GaAs(砷化镓)晶圆,此类材质可以通过化镀镍金溶液,不需要特殊保护。但此类产品通常正面无钝化层或钝化层非常薄(几纳米到几十纳米左右),化镀前需要增加临时保护层。另外,此类材料的具有硬脆,且晶型取向比较明显,受到外力碰撞时容易产生应力而导致裂片,在薄片晶圆上表现尤为明显,化镀过程中必须采取相应保护措施,防止此类晶圆和治具间的直接碰撞。 其他晶圆材料如:玻璃,AlN,SiC具有比较高的强度和短时间内耐酸碱腐蚀性,通常化镀过程中,不需要特殊保护。 2.2 钝化层材质及覆盖 除少数特殊器件无钝化层覆盖外,多数器件产品晶圆的表面都带有钝化保护层。钝化层的种类大致可分为无机材质和有机材质,无机材质的钝化保护层如:SiO2和Si3N4,有机材质的钝化保护层如: PI(polyimide聚酰亚胺类),BCB (benzocyclobutene)和一些临时性的光阻材料。具体采用什么种类的钝化层及钝化层的厚度,要视具体产品和工艺要求而定。无论任何材质的钝化层,都要求覆盖完整、厚度均匀、无应力、无空洞、附着力好,化镀过程中无分层脱落,钝化保护层覆盖金属层边缘的宽度以4um以上为佳。 2.2.1无机材质钝化层 无机材质的钝化层多为SiO2和Si3N4,若其厚度到达1um 以上,就可以到达化镀镍金工艺的要求。无机材质钝化层的缺陷之一为晶圆边缘区域覆盖不足,如图3所示。在芯片边缘钝化层覆盖不足的地方,会沉积一层镍金层,类似边缘楞边(rim)。此金属线条的附着力通常比较弱,会随机脱落影响工艺控制及后续减薄流程,见图4所示。

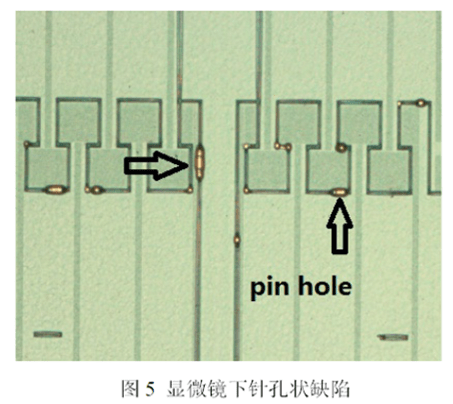

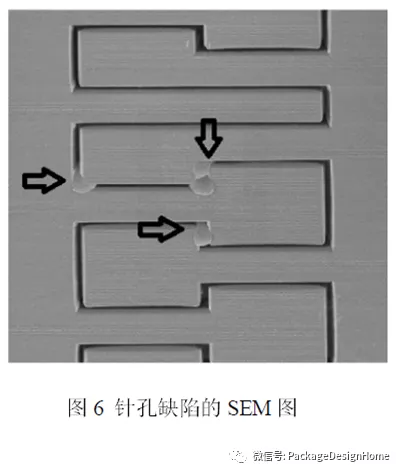

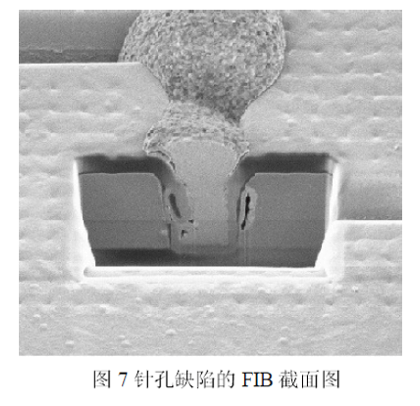

钝化层是沿积体电路的形貌而沉积的,对于某些器件内电路的拐角处,很容易存在空洞或裂纹,这些空洞或裂纹是由于沉积不足或应力造成的。如果缺陷集中在一点,会造成针孔状的缺陷,在此针孔处会发生化学镍金层的沉积,如图5,图6,图7所示。

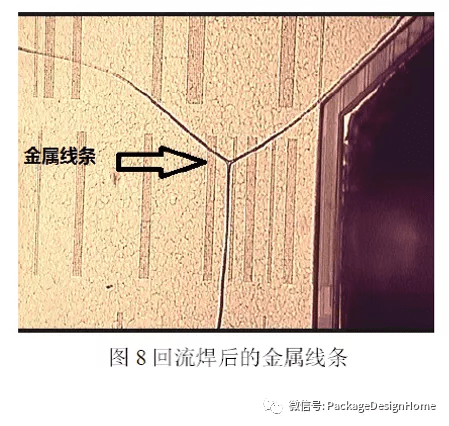

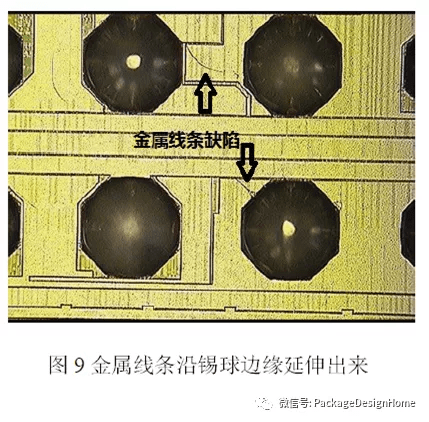

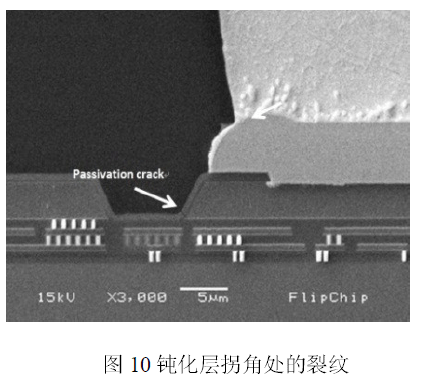

如果此类缺陷连接成一条线,形成裂纹,经过化镀流程此裂纹处会沉积镍金层,成为一金属线条。此金属线条缺陷在晶圆表面其他区域发生,类似针孔缺陷比较容易识别出来,如此缺陷围绕I/O 金属垫周围的凹槽中,则不易识别。 如图8,图9所示,沿I/O 金属垫周围的凹槽中,钝化层的拐角处存在裂纹,化镀后在裂纹处沉积一层镍金而形成金属线条。此金属线条在化镀检查时并未发现,但在后续锡膏印刷回流焊后,由于高低温4的变化而脱落下来,形成沿沿锡球边缘延伸出来的金属线条。图10为缺陷位置的SEM切片横截面图,在钝化层的拐角清晰显示出裂纹的位置。

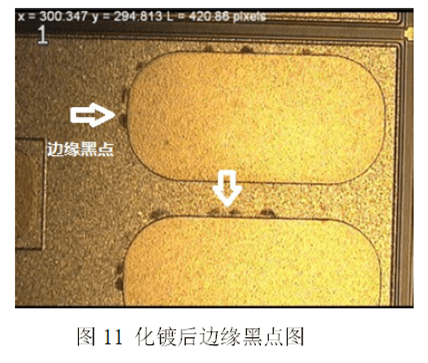

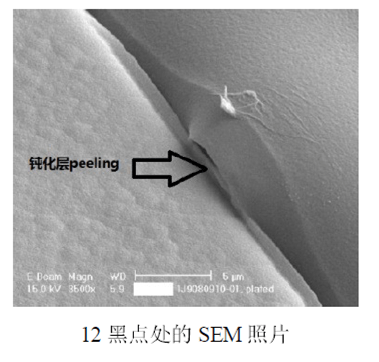

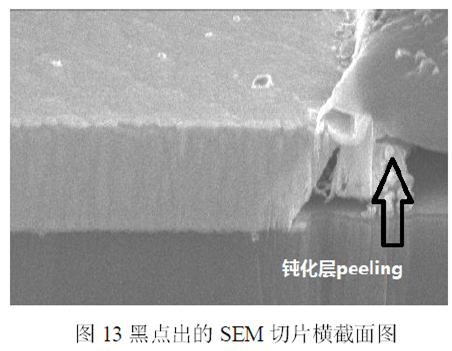

2.2.2 有机材质钝化层 有些器件为了增强其电性能,会在无机材质的钝化层上再增加一层有机材质的钝化层。另外在后段封装中,RDL(redistribution layer)工艺应用的增多,也都会用到有机材质的钝化层,其成分多为PI类。有机材质的钝化层在制作过程中涉及涂覆、曝光、显影、烘烤聚合等工艺,其中容易产出的缺陷为:气泡、空洞、overetching (过蚀刻)、厚度不均、残留、附着力不足等,以上缺陷经过化学镀药水的浸泡和反应后形成与之相相应的缺陷。 图11是表面覆盖有机材质钝化层的晶圆,经过化镀工艺后在I/O 金属垫的边缘出现黑色点状缺陷,此黑色点状在SEM显微镜镜下显示为钝化层浮起鼓包现象,如图12中箭头所示位置。通过对此位置做近一步的切片分析,显示此位置的钝化层从下面的基材上剥离,见图13箭头所示位置。

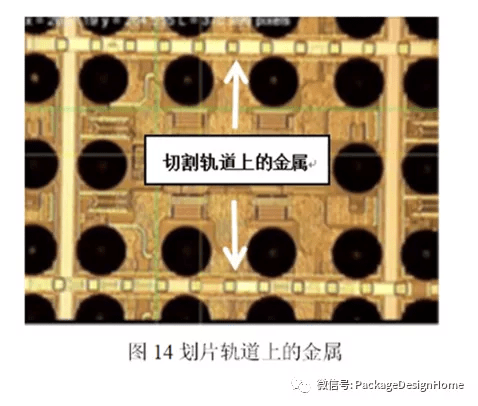

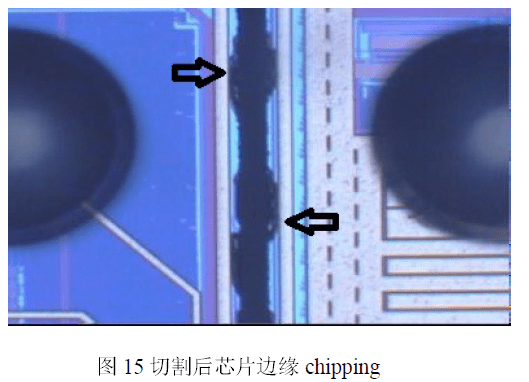

作为永久性的的有机钝化层,是经过高温烘烤固化的,有很好的耐酸碱和高温的能力,而对于工艺过程中所用到光阻类的临时过程胶,需要在化镀完成后去除。此类的光阻通常耐酸不耐碱,在使用过程前,要对其和化学溶液、工艺参数的适配性做必要的性能评估。 2.3 切割轨道形貌要求 在化镀湿制程中,所有金属暴露的位置都会有化学镍金层的沉积,除需要化镀的区域外,其他区域需要有钝化层的覆盖。但在晶圆制作过程中,表面除I/O 位置外,其他一些特位置也会裸露出金属,这些位置主要包括特定测试位置和划片轨道。通常测试位置的裸露金属对后续封测不产生影响,但在划片轨道上的金属垫经过化镍金后,可能会对后续切割工艺造成影响。半导体晶圆上铝层的维氏硬度为100HV左右,而化学镍金层的硬度为550HV,是铝层硬度的5倍多,对于厚度为5um及以下的化学镍金层,对后续切割不会有明显的影响,但如果其在轨道上的占比面积超过50%,且比较靠近芯片的guard ring(保护环)位置,则存在比较大的chipping风险。

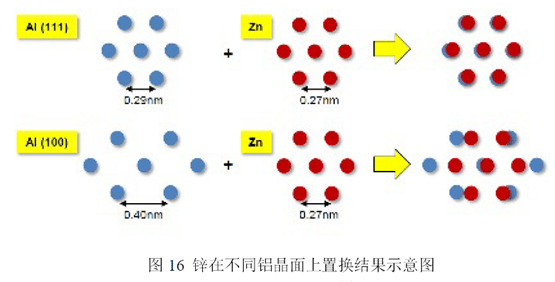

图14所示的划片轨道中,金属垫的位置靠近芯片的guard ring位置,经过划片工序后,存在金属垫的区域产生了比较大chipping,见图15。为减小此类问题的影响,在芯片切割时,应综合考虑划片轨道的宽度及金属层的厚度,优化切割工艺参数工艺,避免较大的chipping损伤到芯片的功能区。 对于要求更厚的化学镍金层,在化镀前需要对划片轨道上的金属进行保护,以避免后续切割时难以解决。 3. I/O 金属垫的成分、结构及厚度 在I/O 金属垫上沉积一层镍金/镍钯金,从而实现特定形式的封装要求,是半导体晶圆上化镀工艺的主要目的。从技术形式上是属于表面处理的范畴,化学沉积发生在表面几微米的区域内,和其他产品表面处理有类似性,但同时由于每个I/O 金属垫下面连接不同的线路,具有不同的电性能输入输出,而表现出不同于一般产品的的技术特点。 3.1 I/O 金属垫的成分 半导体晶圆I/O 金属垫的成分主要有铝基和铜基两类,其中铜基分可为PVD沉积铜和电镀铜,目前化镀工艺中接触最多的是RDL 工艺中的电镀铜。铝基的晶圆相对成分比较复杂,有纯铝,铝铜,铝硅铜,其中铜和硅的含量因不同产品而不同,常见的成分组成为AlSiCu (0-1%Si and 0.25 - 2.5% Cu);AlCu (0.25 - 2.5%Cu);Al/Si(1-2%),在铝层中增加铜和硅是为了防止电迁移(electromigration)及硅在铝层中的穿刺(spike)现象[18]。 根据电极电位理论,铜和铝属于难镀基材,在化学镀镍前一般要通过前处理的活化,铜基材的通常采用活化钯工艺,铝基材则采用锌置换的方式。如图16所示,锌为六方晶体结构,其原子间距为0.27nm,但纯铝层中在不同的晶面其原子间距不同,A(111)晶面其原子间距为0.29nm,和锌原子间距非常接近,容易进行置换反应。但对于A(100)晶面,其原子间距为0.40nm,和锌原子的间距的差距较大,难以发生置换反应。在纯铝的表面层中,两个晶面的分布是随机的,是非常难以沉积镍金层的[19]。铜原子的直径(0.255nm)和铝原子的直径(0.286nm)相近,且同属金属元素,在铝层中添加少量的铜,可以通过晶格畸变,改变铝层中会A(100)晶面中铝原子的空位间隙距离,使铝和锌的置换变得容易。而硅原子的直径为0.117nm 约为铝原子直径的一半,添加到铝层中进入原子间空隙而对于铝原子的间距影响不大,并且硅为非导体,和金属铝性能相差比较大,硅的添加反而产生负面的影响。

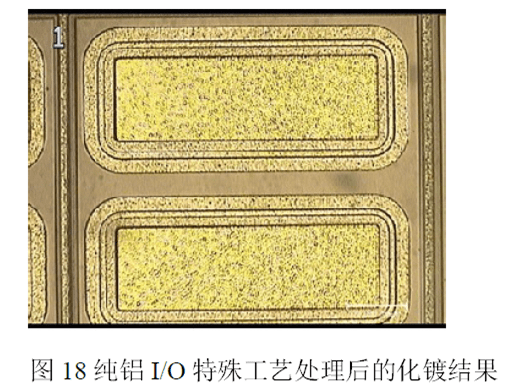

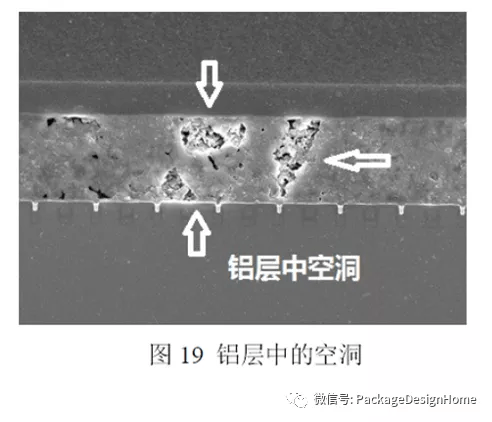

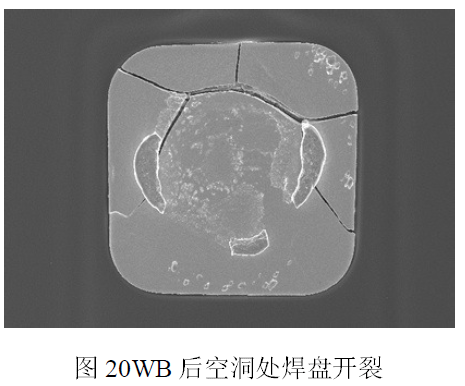

通过一些特定的前处理药水和合适的工艺参数,在纯铝或铝硅产品上可以得到较为理想的镍金沉积层。图17为通用的化镀方式沉积的镍金层,图18为通过特定药水和工艺沉积的镍金层,两者比较可以看出,前者表面粗糙,有空隙存在,测试表明附着力差;后者沉积层表面光亮均匀,通过附着力测试。由于铝的成分复杂,加之不同晶圆厂的工艺控制水平差别比较大,应优先考虑添加铜元素的铝层。 3.2 I/O 金属垫的形貌、结构及厚度 除了I/O 金属垫的金属成分对化镀镍金层有直接影响外,其结构、形貌及厚度的差别也会显示在最终产品上。半导体晶圆化学镀工艺过程中,来料的形貌和结构特征会复制到化镀后产品上,来料晶圆I/O金属垫的形貌最直观的表现是其晶粒大小及粗糙度。粗糙铝面的晶界处,由于其结构和晶粒内部不同,反应活性比较强,其蚀刻速度要较晶粒其他位置要快,会形成许多小的凹坑,在此晶界凹坑,化镀后很容易形成镀瘤[20]。 一般化镀镍金工艺要求I/O金属垫的铝层或铜层的厚度大于1um,厚度低于1um 是风险比较大的。如果铝层沉积过程中,在某些位置形成空洞一类的缺陷,此位置在后续封测过程比如wire bonding中,受到外力的冲击,会导致此处有NSOP 及焊盘开裂发生,见图19,图20。

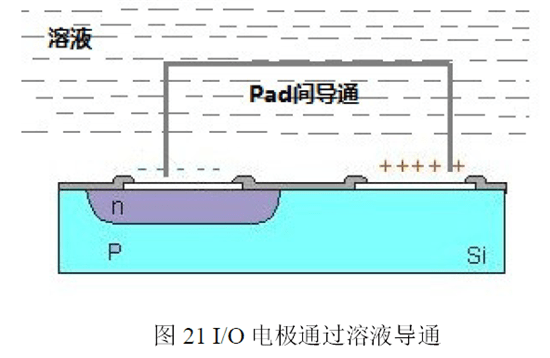

如果铝层薄且不均匀,厚度低于0.8um,加之有空洞现象,化镀后局部的铝层会被蚀刻掉,镍金层的附着力会极差,结果是“致命”的。 3.3 I/O 电势的影响 半导体芯片内部布满电路互联(PN 节及金属导线),内部的不同电路结构表现为外部I/O 电极电势的差异。不同功能的芯片,不同功能的I/O 电极,有着不同的电势[21]。如图21所示,晶圆化镀工艺是湿制程,整个过程中晶圆浸泡在化学溶液中,不同电势的I/O 电极会通过溶液连接导通,加之化学镀镍反应过程比较复杂,各个I/O 电极上化学镍金/化学镍钯金的沉积情况是不同的。

对于I/O 数目少的简单器件,化镀后比较容易检测出各个电极的差别,对于I/O 数目较多的器件,应逐一检测甄别其中的差别。 4. 结论 华林科纳认为采用化学镀的工艺,在半导体I/O pad上沉积镍金/镍钯金过程中,其中产生的问题和缺陷和来料晶圆有着直接的关联。在产品设计及评估时,应对产品本身结构和功能有充分的了解,包括钝化层种类及厚度,I/O pad的成分及结构,切割轨道上金属pad的大小及是否有钝化层的覆盖,不同I/O pad的电势等因素。基于对这些因素的综合考虑和充分了解,一方面可以避免化镀过程中造成的缺陷及问题,另一方面从相类似的缺陷,可以有助查找问题发生的根源,同时也可以指导对问题产品进行后续合理的处置。返回搜狐,查看更多 |

【本文地址】