| 傻白入门芯片设计,典型的2D/2D+/2.5D/3D封装技术(六) | 您所在的位置:网站首页 › 芯片RDL层作用 › 傻白入门芯片设计,典型的2D/2D+/2.5D/3D封装技术(六) |

傻白入门芯片设计,典型的2D/2D+/2.5D/3D封装技术(六)

|

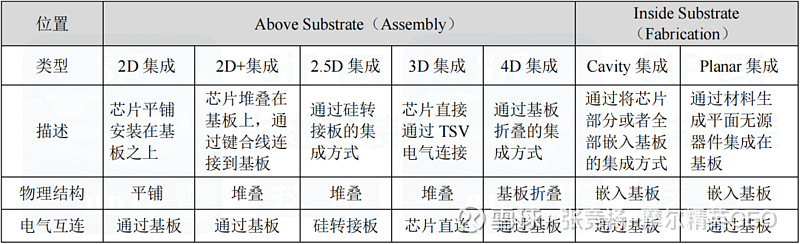

集成电路终于成为了一级学科,对集成电路领域的投入也日益加大,集成电路属于电子集成技术的一种,那么,现在的电子集成技术发展到了什么程度呢? 先进的电子集成技术可以在不到芝麻粒大小的1平方毫米内集成1亿只以上的晶体管,一个指甲盖大小的芯片上集成的晶体管数量可轻松超过100亿甚至更多,而目前地球上的总人口才不到80亿。 本篇文章,侧重于2D封装,2D+封装,2.5D封装,3D封装,当然电子集成技术不止这些,想要更多的了解可以看文末的参考链接。首先我们可以将电子集成技术分为三个层次,芯片上的集成,封装内的集成,PCB板级集成,其代表技术分别为SoC,SiP和PCB(也可以称为SoP或者SoB)。(戳下面的链接了解SoC何SiP的区别):(18条消息) 傻白入门芯片设计,IP, MCM, SiP, SoC 和 Chiplet的区别(二)_好啊啊啊啊的博客-CSDN博客 理解集成的时候,人们通常通过物理结构来判断,今天,我们提出电子集成技术分类的两个重要判据:1.物理结构,2.电气连接(电气互连)。 通过这两个判据,我们将电子集成分为7类:2D集成,2D+集成,2.5D集成,3D集成,4D集成,Cavity集成,Planar集成。其中前面5类是位于基板之上,属于组装(Assembly)范畴,后面2类位于基板之内,属于基板制造(Fabrication)范畴。故此命名为(5+2)分类法。请参看下表:

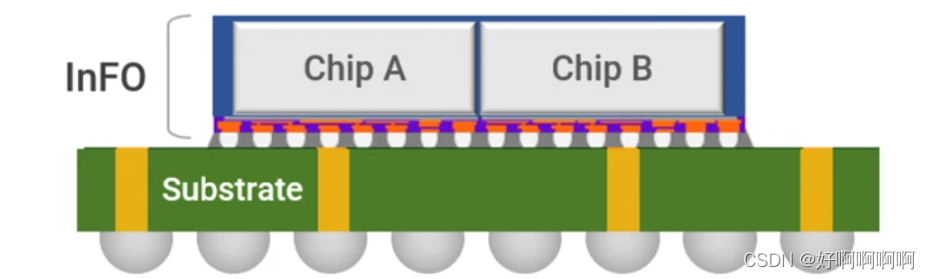

芯片上的集成主要以2D为主,晶体管以平铺的形式集成于晶圆平面;同样,PCB上的集成也是以2D为主,电子元器件平铺安装在PCB表面,因此,二者都属于2D集成。而针对于封装内的集成,情况就要复杂的多,并且业界目前对电子集成的分类还没有形成统一的共识。 目录 一、2D封装 A. 台积电InfO技术: B. 日月光eWLB技术: 二、2D+封装 三、3D封装 A.台积电 SoIC技术: B. 英特尔Foveros技术: C. 三星X-Cube 技术: 四、2.5D封装 A. 英特尔EMIB技术: B. 台积电CoWoS技术: C. 三星I-Cube技术: 一、2D封装2D 封装是指在基板的表面水平安装所有芯片和无源器件的集成方式。以基板 (Substrate) 上表面的左下角为原点,基板上表面所处的平面为XY平面,基板法线为Z轴,创建坐标系。 物理结构:所有芯片和无源器件均安装在基板平面,芯片和无源器件和 XY 平面直接接触,基板上的布线和过孔均位于 XY 平面下方;电气连接:均需要通过基板(除了极少数通过键合线直接连接的键合点) 2D封装上包括FOWLP、FOPLP等技术。在FOWLP领域,各大公司都推出了不同命名方式的封装,例如台积电的InFO(Integrated FanOut technology)、日月光的eWLB(embedded Wafer-level ball grid array)、华天科技的eSiFO、长电科技的ECP。 A. 台积电InfO技术:InFO:集成扇出型封装技术InFO,一个创新的晶圆级系统集成技术平台,具有高密度RDL 和TIV 的特点,可用于高密度互连和各种应用。InFO封装与CoWoS很类似,InFO-R和InFO-L与CoWoS-R和CoWoS-L几乎是一比一对应。实际上,InFO技术与大多数封装厂的Fan-out类似,可以理解为多个芯片Fan-out工艺的集成,主要区别在于去掉了silicon interposer,使用一些RDL层进行串连。苹果2016年推出的iPhone7中的A10处理器,采用台积电16nm FinFET工艺以及InFO技术,成功将AP与LPDDR整合在同一个封装中。

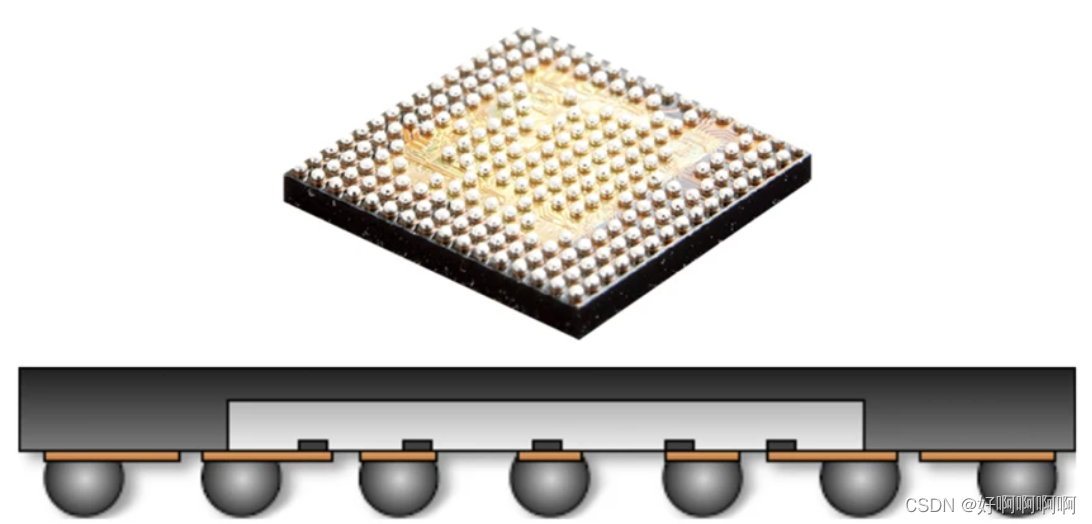

eWLB:嵌入式晶圆级球栅阵列eWLB,是一种扇出型晶圆级封装(Fan-out Wafer-Level Package 缩写FO-WLP)技术,将芯片重新布置到一块人工晶圆上,然后向芯片四周扇出重布线、植球、然后进行封装。值得注意的是,国内长电科技旗下星科金朋新加坡厂同样拥有eWLB封装,如下图:(来自于日月光)

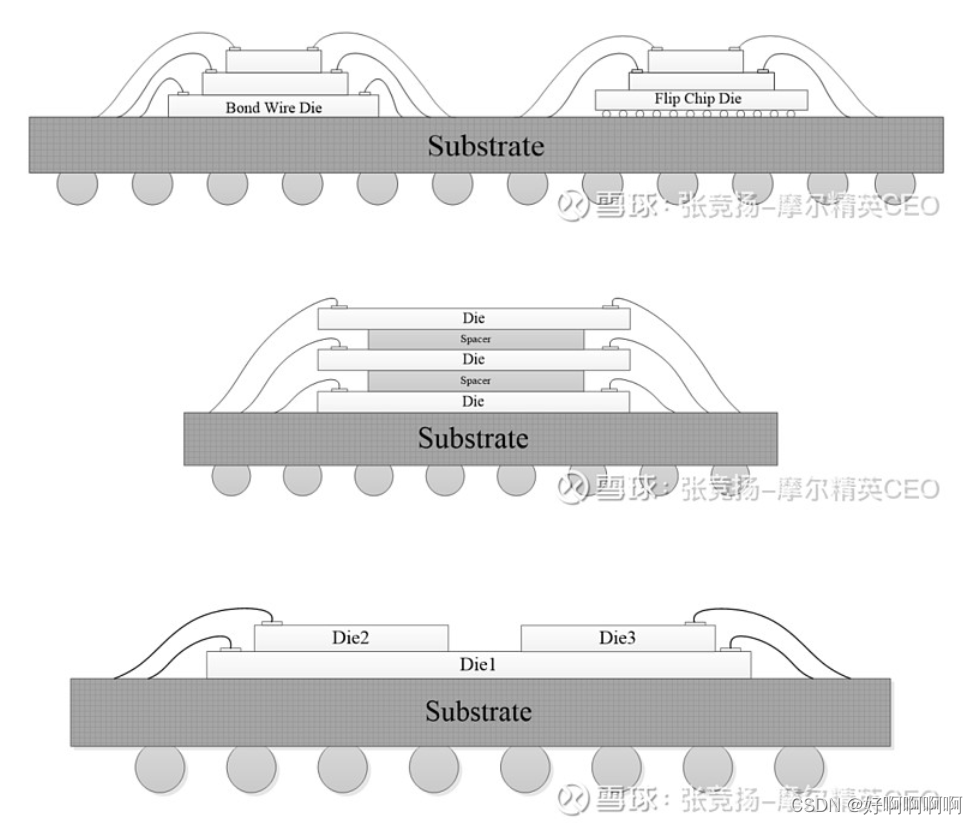

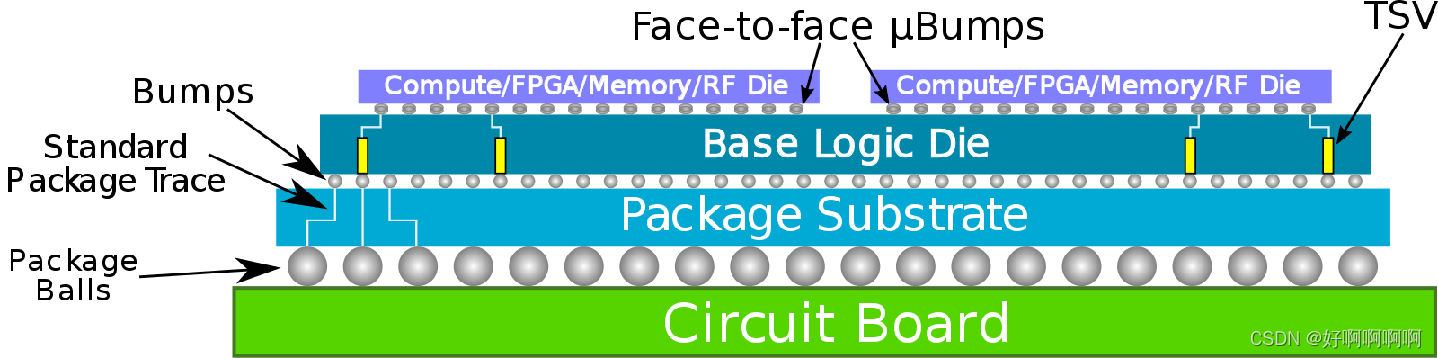

2D+封装是指的传统的通过键合线连接的芯片堆叠集成。也许会有人问,芯片堆叠不就是3D吗,为什么要定义为2D+封装呢? 主要基于以下两点原因:1)3D封装目前在很大程度上特指通过3D TSV的集成,为了避免概念混淆,我们定义这种传统的芯片堆叠为2D+封装;2)虽然物理结构上是3D的,但其电气互连上均需要通过基板,即先通过键合线键合到基板,然后在基板上进行电气互连。这一点和2D封装相同,比2D封装改进的是结构上的堆叠,能够节省封装的空间,因此称之为2D+封装。 物理结构:所有芯片和无源器件均地位于XY平面上方,部分芯片不直接接触基板,基板上的布线和过孔均位于XY平面下方;电气连接:均需要通过基板(除了极少数通过键合线直接连接的键合点)。 下图所示几种集成均属于2D+封装:

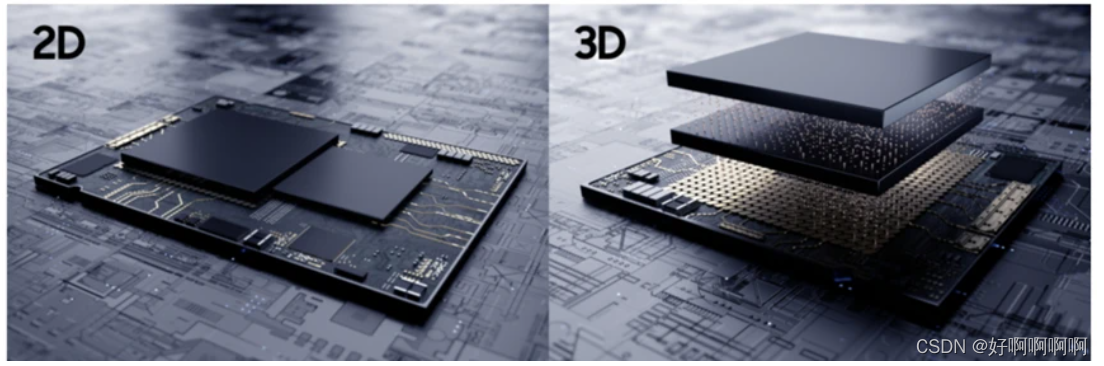

随着工艺技术不断缩放,设计复杂性不断增加,传统的二维集成芯片设计可能不再赶上摩尔定律的缩放趋势。此外,二维集成电路设计难以满足市场快速增长的高性能需求。于是从三维的概念寻找解决方案。它通过垂直堆叠芯片,用更短的互连和高带宽连接起来,弥补了二维集成电路设计的缺点。2D封装中需要大量长程互连,导致电路RC延迟的增加。为了提高信号传输速度,必须降低RC延迟,那么用3D封装的短程垂直互连来替代2D封装的长程互连是封装工艺技术向更高阶发展的必然趋势。整个半导体市场走向3D的明显例子——内存。存储器向3D结构的推进是对未来发展的一个很好的说明。这种技术可以提供更高的带宽、更低的功率、更低的成本和更灵活的形状因子: 更高的带宽,因为它允许多个IC片之间的直接连接,而不必经过传统的平面布线。这可以提高IC的处理能力和性能。更低的功率消耗,因为它允许更紧凑的布线设计,从而减少了信号传输的阻力。这可以降低IC的功率消耗,并使其在使用过程中更加节能。更低的成本,因为它可以使用更少的封装材料,并使用更少的工艺步骤将多个IC片封装在一起。这可以降低生产成本,并提高生产效率。更灵活的形状因子,因为它可以使用更小的封装空间,并且可以适应不同的应用需求。

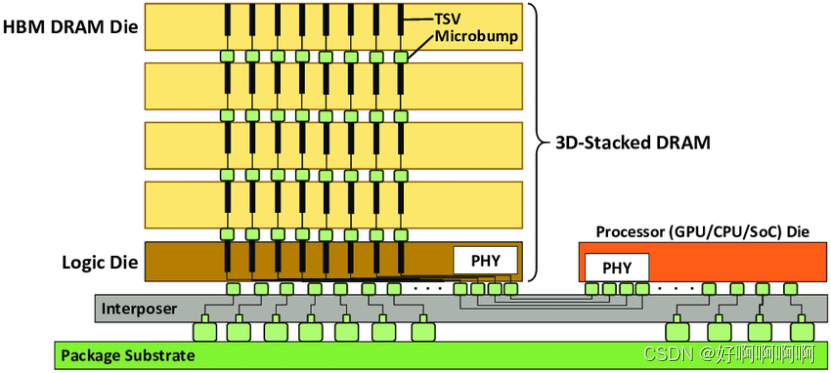

SiP进一步将多个芯片层叠放置并且互相连接,使用在三维方向的堆叠技术,也就是3D芯片封装技术。和2.5D的区别是后者通过中介层进行高密度互连不同,3D是指芯片通过TSV直接进行高密度互连。3D封装将CPU/GPU/SoC与DRAM堆叠并在垂直方向上连接整合,封装的面积比2.5D封装工艺更小,并且在2.5D封装的基础上还去掉了TSV的 interposer的部分。 3D领域主要有台积电的SoIC(System of Integrated Chips)技术、英特尔的Foveros技术、三星的X-Cube(eXtended-Cube)技术。物理结构:所有芯片和无源器件均XY平面上方,至少有部分芯片和无源器件安装在中介层上(Interposer),在XY平面的上方有中介层的布线和过孔,在XY平面的下方有基板的布线和过孔。电气连接:中介层(Interposer)可提供位于中介层上的芯片的电气连接 A.台积电 SoIC技术:SoIC技术:属于3D封装,是一种晶圆对晶圆(Wafer-on-wafer)的键合技术。SoIC技术是采用TSV技术,可以达到无凸起的键合结构,把很多不同性质的临近芯片整合在一起,而且当中最关键、最神秘之处,就在于接合的材料,号称是价值高达十亿美元的机密材料。SoIC技术将同质和异质小芯片集成到单个类似SoC的芯片中,具有更小尺寸和更薄的外形,可以整体集成到先进的WLSI(又名CoWoS和InFO)中。从外观上看,新集成的芯片就像一个通用的SoC芯片,但嵌入了所需的异构集成功能。 B. 英特尔Foveros技术:Foveros技术:同样也是3D封装的一种。封装基底之上安放一个底层芯片,起到主动中介层的作用。在中介层里有大量的TSV 3D硅穿孔,负责联通上下的凸块,让上层芯片和模块与系统其他部分通信。相较于EMIB的凸点间距为55-36um,Foveros将凸点间距进一步降低为50-25um。从3D Foveros的结构上看,最下边是封装基底,之上安放一个底层芯片,起到主动中介层的作用。在中介层里有大量的TSV 3D硅穿孔,负责联通上下的焊料凸起,让上层芯片和模块与系统其他部分通信.

X-Cube :3D封装技术,使用TSV工艺,目前三星的X-Cube测试芯片已经能够做到将SRAM层堆叠在逻辑层之上,通过TSV进行互联,制程是他们自家的7nm EUV工艺。

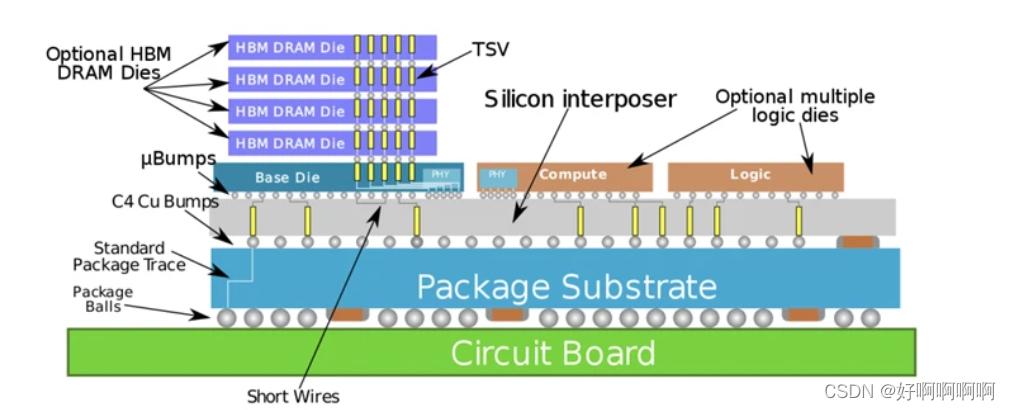

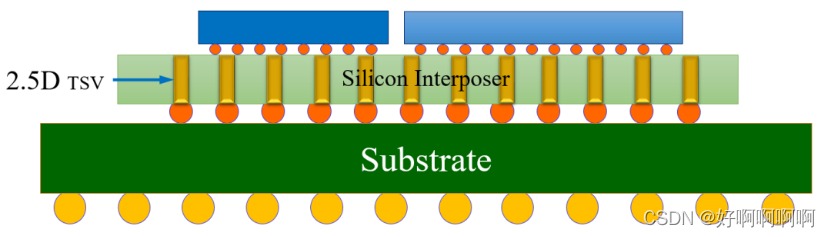

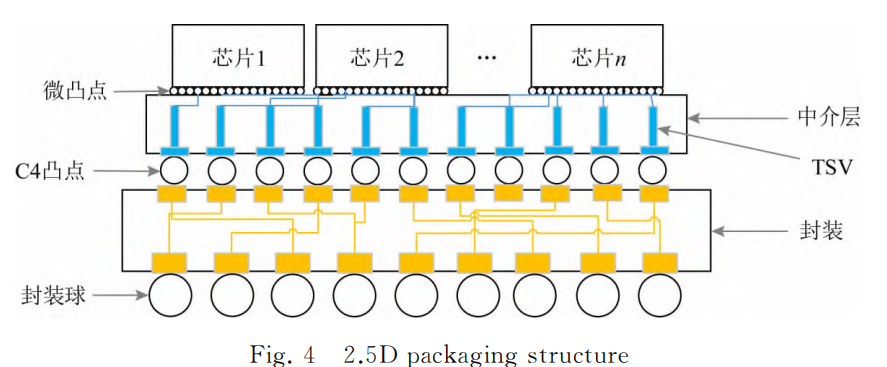

然而,三维集成电路设计暴露了一些弱点,如通过硅通孔(TSV)的大开销和高温问题。随后,提出了基于interposer的2.5D 的封装设计,以克服3D集成存在的问题,并保持其优势。2.5D本身是一种在客观世界并不存在的维度,因为其集成密度超越了2D,但又达不到3D的集成密度,取其折中,因此被称为2.5D。 在先进封装领域,2.5D是特指采用了中介层进行高密度I/O互连的封装,其特点是多Die集成和高密度性。中介层目前多采用硅材料,利用其成熟的工艺和高密度互连的特性。根据目前的工艺水平,2.5D 封装又主要分为重布线层(RDL)Interposer和Si Interposer。 裸片和基底之间的连接是通过硅孔(TSVs)和Micro-Bumps实现的。由于Micro-Bumps和TSV具有较小的bump间距和trace距离,基于硅中介层的封装技术提供了更高的I/O密度和更低的传输延迟和功耗。理论上讲,中介层中可以有TSV也可以没有TSV,但在进行高密度互联时,TSV几乎是不可缺少的。

2.5D封装结构通常将芯片面朝下安装在具有一系列微型凸点(micro-bumps,ubmps)的中介层上.目前的ubmps间距为40~40um,正在开发20um和10um的间距技术.ubmps提供从上层堆叠的芯片到中介层里金属布线层的连接.金属布线层采用与常规2D独立芯片上金属互连相同的后端工艺制造.中介层上还使用了1个超薄芯片,用于TSV将输入输出路由到C4凸点.数据从芯片出发,通过1个微凸点,穿过中介层的金属布线层,在通过另一个C4凸点,最后达到目标芯片的顶层金属。

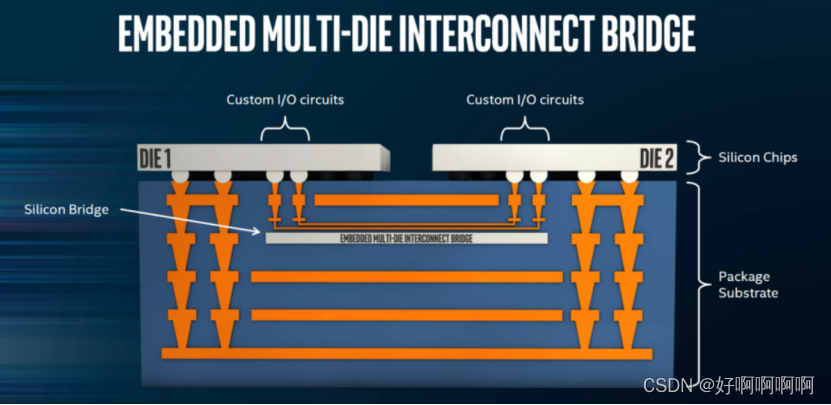

EMIB:嵌入式硅桥(Embedded Multi-die Interconnect Bridge),将基底技术和硅中介层技术结合起来。它在基板上集成了小的薄层——硅桥( Silicon Bridge ),用于芯片间的互连,并将硅桥嵌入封装基板中。英特尔的EMIB的概念与2.5D封装类似,但与传统2.5D封装的区别在于没有TSV。也正是这个原因,EMIB技术具有正常的封装良率、无需额外工艺和设计简单等优点。 EMIB如图所示:(来自于英特尔)

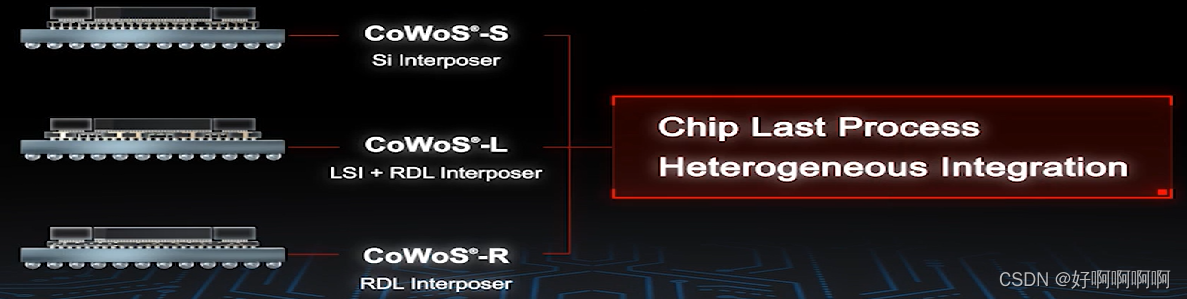

CoWoS技术:片上晶圆基板(Chip on Wafer on Substrate), 一种基于硅中介层的2.5D集成封装技术。将芯片通过Chip on Wafer的封装制程连接至Wafer,再把CoW芯片与Substrate(基板)连接,整合成CoWoS。并使用硅载片上的高密度走线进行互联。CoWoS封装如下图所示:(来自于台积电)

CoWoS基于不同的中介层拓展了三种技术。根据中介层的不同可以分为三类,一种是CoWoS_S使用Si衬底作为中介层,另一种是CoWoS_R使用RDL作为中介层,第三种是CoWoS_L使用小芯片(Chiplet)和RDL作为中介层。

台积电InFO与CoWoS之间的区别在于,CoWoS针对高端市场,连线数量和封装尺寸都比较大;InFO针对性价比市场,封装尺寸较小,连线数量也比较少。 C. 三星I-Cube技术:I-Cube:具有的先进封装包括I-Cube、X-Cube、R-Cube和H-Cube四种方案。其中,三星的I-Cube同样也属于2.5D封装。2018年,三星发布了I-Cube2,可以集成一个逻辑裸片和两个HBM裸片的技术。目前,三星推出下一代2.5D封装技术是I-Cube4。I-Cube4包含四个HBM和一个逻辑芯片,是I-Cube2的进一步升级。I-Cube封装如下图:(来自于三星)

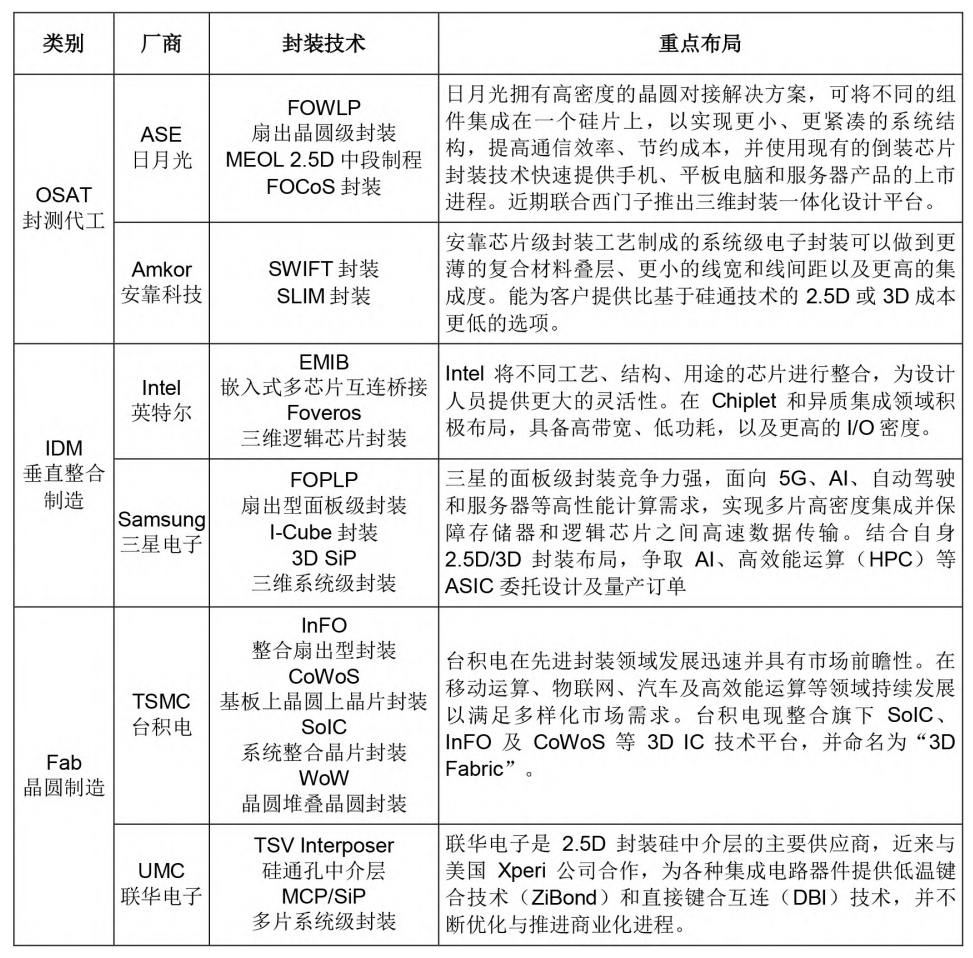

在数据带宽方面,3D集成架构更好,这需要更好的热设计。该体系结构更适合于高性能计算,如数据中心、网络、服务器等。在成本方面,2.5D集成架构不需要具有高密度TSV的多层交互器;因此,这个过程不那么困难。该架构更适合于移动设备、笔记本电脑、可穿戴电子设备等应用。在芯片材料方面,由于热膨胀系数相同,多个均匀芯片采用3D集成结构,有利于提高机械可靠性;异质芯片更适合2.5D集成结构(如EMIB集成技术),具有较高的系统散热性能,同时其面积会增大。国际领先厂商先进封装领域布局如下:

参考资料: 先进封装,风暴袭来_腾讯新闻 (qq.com) 先进封装之盖楼大法——2.5D、3D封装 - 知乎 (zhihu.com) 这是我目前见过最好的先进封装技术讲解文章 - 知乎 (zhihu.com) 2.5D和3D集成有何不同?看完这篇你就懂了 来源:内容由半导体行业观察(ID:icbank)转载自公众号「SiP与先进封装技术」,谢谢。 导 读 当今,如果要评选国... - 雪球 (xueqiu.com) |

【本文地址】

3D封装和2.5D封装的主要区别在于:2.5D封装是在Interposer上进行布线和打孔,而3D封装是直接在芯片上打孔和布线,电气连接上下层芯片。2.5D封装通常是指既有2D的特点,又有部分3D的特点,其中的代表技术包括英特尔的EMIB(Embedded Multi-Die Interconnect Bridge)、台积电的CoWoS( Chip-on-Wafer-on-Substrate)、三星的I-Cube(Interposer-Cube)。

3D封装和2.5D封装的主要区别在于:2.5D封装是在Interposer上进行布线和打孔,而3D封装是直接在芯片上打孔和布线,电气连接上下层芯片。2.5D封装通常是指既有2D的特点,又有部分3D的特点,其中的代表技术包括英特尔的EMIB(Embedded Multi-Die Interconnect Bridge)、台积电的CoWoS( Chip-on-Wafer-on-Substrate)、三星的I-Cube(Interposer-Cube)。