| 212卷积码的译码设计0Word下载.docx | 您所在的位置:网站首页 › 编码器和译码器应用电路的设计与调试 › 212卷积码的译码设计0Word下载.docx |

212卷积码的译码设计0Word下载.docx

|

212卷积码的译码设计0Word下载.docx 《212卷积码的译码设计0Word下载.docx》由会员分享,可在线阅读,更多相关《212卷积码的译码设计0Word下载.docx(26页珍藏版)》请在冰豆网上搜索。

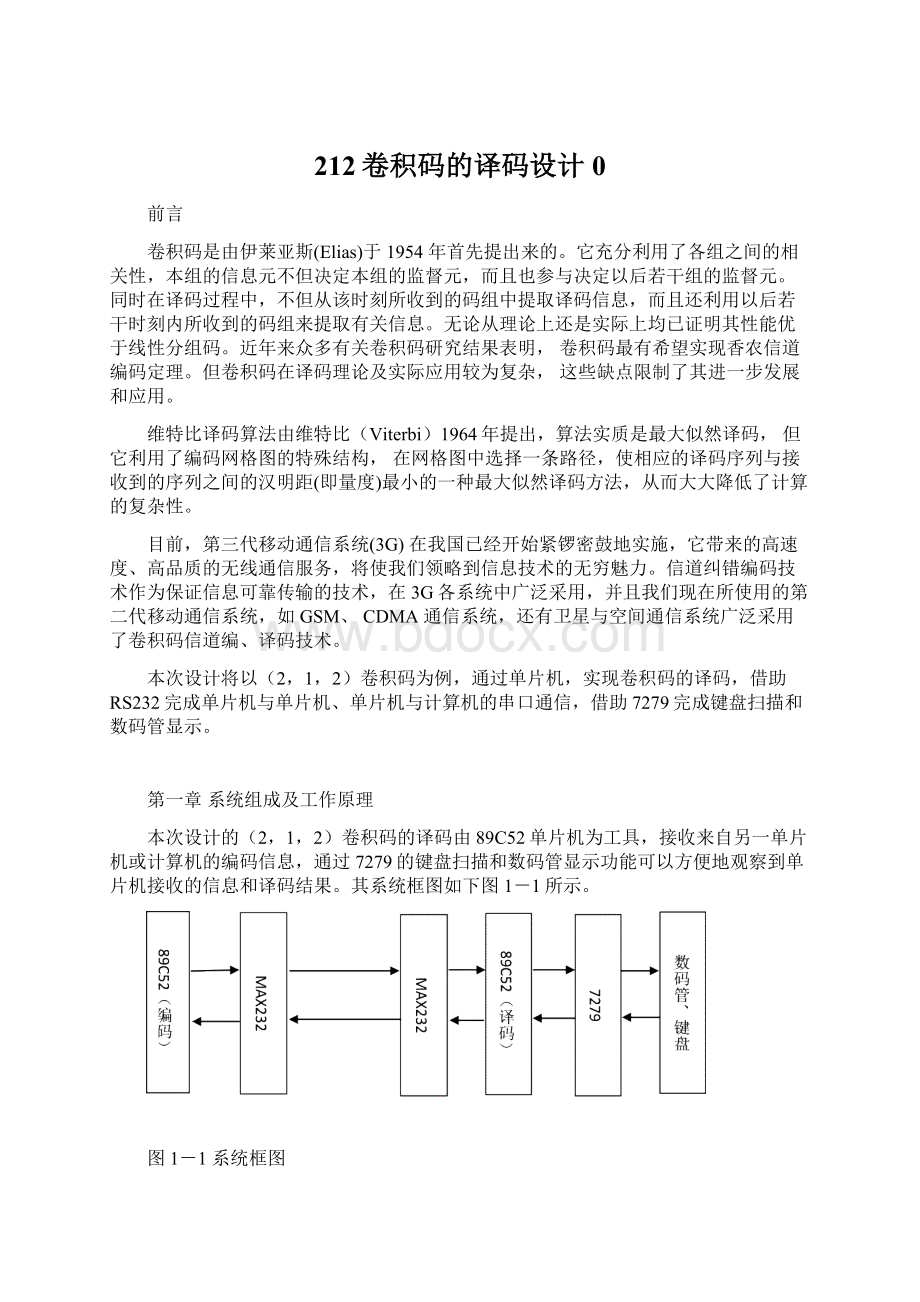

1.系统初始化堆栈指针SP设为67H,清10H-7FH内存单元,7279初始化,设置定时器1工作于方式2,波特率为1200,启动定时器,串行口工作于方式2并允许串口接收数据。 2.数据接收当译码器接收到有效数据时,将接收到的12字节的数据存于存贮器16H-21H中,并将其转换为适合维特比译码的6字节数据,存于存贮器10H-15H单元中。 图2-5系统总流程图3.读数据当有键按下时,读取键值,并存于Acc寄存器中。 4.数据判断判断按键号,并根据键号转向相应的处理程序。 5.显示MOVR6,#18HLI0: DJNZR6,LI0MOVA,#0A4HACALLSTFSMOVR6,#02HLI1: DJNZR6,LI1DISP1: MOVR5,#08H;图2-1(2,1,2)卷积码编码器设寄存器m1、m2的起始状态为全零,则编码器的输入输出时序关系可用图2-2表示。 图2-2(2,1,2)卷积码编码器的输入输出时序要使最后1位输入同样影响3对输出,并且使编码器回到全零状态,还需使编码器多输出2对信息,为了做到这一点,需要增加2个时钟循环,并且在此期间保持输入为0,这一过程叫做“点亮”编码器。 如果不执行“点亮”操作,最后2位输入信息的纠错能力就会下降。 2.1.3卷积码的图解表示根据卷积码的特点,常采用图解表示法对其进行研究。 主要的图解表示法有两种,即状态转移图、网格图。 因为卷积码的编码器的记忆性是有限的,所以可以使用状态转移图来表示其转移过程。 在状态转移图中,卷积编码器的每一个状态对应于一个椭圆,状态的转移用两个椭圆间的有向线段表示,在线上标出状态转移的输入和对应的输出。 上述调试过程并不是一帆风顺的,调试过程中会遇到许多故障,有些故障很容易找到原因,但有一些故障,其原因难以发现。 例如程序中有一句“DJNZR7,LW0”,由于LWO太远(离“DJNZR7,LW0”超过128字节),所以程序找不到,需要将其拆分为“DJNZR7,LP0”和“LP0: LJMPLW0”两句。 还有在用两块单片机进行通信时,只要编码单片机一发送数据,译码单片机就会死机,开始怎么也找不到错误,后面将编码单片机与微机(串口调试助手波特率设为1200)进行通信,发现单片机每发送12个数据,串口调试助手则接收到18个数据,所以怀疑是由波特率不一致导致的错误,后来检查发现编码单片机的晶振频率为6MHz,与译码单片机的11.0592MHz不同,所以两者波特率不同,导致接收单片机接收到18个数据,陷入死循环,改变编码单片机的TH1、TL1,使编码单片机与译码单片机的波特率都为1200,两块单片机能够正常通信。 第四章总结4.1方案的缺点和改进卷积码的纠错性能虽然优于分组码,但是卷积码的译码存在一些缺点: 译码器只有在收到全部序列(卷积码可能非常长)之后,才能开始译码,并且需要记录下所有的幸存路径。 可见维特比算法的时延很大,同时还需要大量的存储空间来保存历史状态记录。 在实际中可以采用路径存储截断法,具体过程是: 1.单片机译码部分;2.RS232串口通信部分;3.数据显示部分。 第二章软件设计2.1相关理论说明2.1.1卷积码的描述卷积码是把k个信息比特的序列编成n个比特的码组,每个码组的n-k个校验位与本码组的k个信息位有关,而与其他码组无关。 为了达到一定的纠错能力和编码效率,分组码的长度一般都比较大。 编译码时必须把整个信息码组存储起来,由此产生的译码延时随n的增加而增加。 卷积码是一个有限记忆系统,它也将信息序列分割成长度k的一个个分组,然后将k个信息比特编成n个比特,但k和n通常很小,特别适合以串行形式进行传输,时延小。 7279的CS引角恢复高电平图2-8读键值流程图图2-7接收串口数据流程图2.5读数据部分主程序循环中每次都要判断是否有键按下,当有键按下时,调用读键值子程序,读出此按键的键号,并将键号存于Acc寄存器中,为后面的判断键号作准备。 读键值流程图如图2-8所示。 2.6数据判断部分当有键按下时,判断按键号,并根据键号转向相应的处理: 如果键号为“1”,数码管显示接收数据的前8位;如果键号为“2”,数码管显示接收数据的后4位;LCALLINITIAL;键4按下,7279初始化子程序LJMPM0M2: CLR10HM3: MOVA,#0FFHLJMPM0;主程序循环,等待接收和按键RECE: JB10H,M3;按键没有弹起,跳至M3LCALLKEY;有按键按下且上次按键已弹起,调用读键盘子程序SETB10HCJNEA,#1FH,M4LCALLDISP1;键1按下,调用显示1子程序LJMPM0M4: INCR1DJNZR7,MM1LCALLINITIALMOVTMOD,#20H;定时器1工作于方式2MOVTH1,#0E8H;设置波特率为1200MOVTL1,#0E8HSETBTR1;定时器开始工作求译码结果流程图如图2-16所示。 第三章实验调试与分析3.1使用的主要仪器和工具1.带有串行接口的微机一台2.5V稳压电源一个3.单片机最小系统板两块4.串口线一根5Keil仿真软件6.串口调试助手3.2调试方法CJNEA,#1EH,M5LCALLDISP2;键2按下,调用显示2子程序M5: CJNEA,#1DH,M6LCALLYM;键3按下,调用维特比译码子程序LCALLDISP3M6: CJNEA,#1CH,M3译码过程中,译码器在每一级不必搜索到起始状态,而只向后搜索x级,这样在第x+1级状态上,译码器将输出对应于第一级的输入,而以后收到的序列不会对这个判决结果产生影响。 4.2收获和体会通过本次设计,在理论与实践上都有很大的提高,学会了卷积码的原理和维特比译码方法,并且熟悉了Keil和串口调试助手两个软件的使用方法,以下是我的在这次设计中的心得体会。 查阅资料的能力很重要。 当你接到一个课题时,你不可能对其牵涉到的原理都清楚,这就需要你又快、又准地找到相关资料来做参考或是把原理搞懂,这样才能在较短的时间里设计出好的东西来。 在设计中一定要心细,尤其是在是在编程和软件调试时,忽略任何细节都可能导致严重的错误。 在出现故障时,要从故障出现的现象,分析导致可能故障的原因、故障的位置以及故障的排除方法。 要理论联系实际,用理论知识解决实际问题,并能够通过实际现象,验证理论的正确性并帮助更好的理解理论知识。 参考文献[1]朱小龙.数字通信技术.北京: MOVR7,#08H;给7279发送一字节程序FS0: RLCAMOVP1.2,CSETBP1.1CLRP1.1DJNZR7,FS0STJS: 从7279接收一字节程序北京邮电大学出版社,2004附录程序清单ORG0000HMAIN: MOVSP,#67HMOVR1,#10HMOVR7,#70HMM1: MOV@R1,#00H;清内存单元化学工业出版社,2004年[2]张立科.单片机典型模块设计实例导航.北京: 人民邮电出版社,2004年[3]JohnG.Proakis.通信系统原理.北京: 电子工业出版社,2006年[4]周荫清.信息理论基础.北京: 北京航空航天大学出版社,2006年[5]张友德.单片微型机原理、应用与实验.上海: 复旦大学出版社,2008年[6]马海武.通信原理.北京: MOVR0,#16H;接收12字节程序MOVR7,#0CHWAIT: JBCRI,RR0AJMPWAITRR0: MOVA,SBUFMOV@R0,AINCR0DJNZR7,WAITLCALLCHANGRETKEY: CLRP1.0;读键值程序MOVR6,18HK1: DJNZR6,K1MOVA,#15HMOV30H,AMOVR3,#11HMOV32H,AINCR0ADDA,30HMOV34H,AMOV@R1,#00HINCR1MOVR3,#10HADDA,32H将接收到的数据或译码结果直观的在数码管上显示出来。 6.维特比译码对接收到的数据进行维特比译码,并将译码结果存于存贮器58H-5DH单元中。 2.3初始化部分系统初始化是为以后串口接收数据,7279显示作好准备,其的主要工作是将堆栈指针SP设为67H,清10H-7FH内存单元,7279初始化,设置定时器1工作于方式2(自动恢复初始的8位计数器),波特率为1200(不一定要1200,但波特率过高,数据传输过程中可能出错),启动定时器,串行口工作于方式2(9位异步串行通信,一帧信息为11位: 1位起始位,8位数据位,1位附加数据位,1位停止位)并允许串口接收数据。 图2-6系统初始化流程图2.4数据接收部分在主程序的循环中,每次都要判断是否从串中接收到有效数据(RI是否为1),当串中接收到有效数据时,将接收到的12字节的数据存于16H-21H中,并将其转换为适合维特比译码的6字节数据,存于10H-15H单元中。 串口数据接收流程如下图2-7所示。 56000102031011求状态历史记录和误差流程图如图2-11所示,其流程图又可以分为三个部分,分别如图2-12、2-13、2-14所示。 图2-11求状态历史记录和误差流程图另一类是概率译码,这种译码建立在最大准则的基础上,由于计算时用到了信道的统计特性,因而提高了译码性能,但这是以增加硬件复杂度为代价的,常用的概率译码方法是维特比译码。 维特比译码是基于最大似然准则的概率译码,它的基本思想是比较接收序列与所有可能的发送序列,从中选择与接收序列汉明距离最小的发送序列作为译码输出。 可能的发送序列与接收序列的汉明距离称为量度。 维特比译码使用网格图描述卷积码,每个可能的发送序列都与网格图中的一条路径相对应,如果在某个节点上发现某条路径已不可能与接收序列具有最小距离,那么就放弃这条路径,这样一直进行到倒数第二级。 由于这种方法较早地丢弃了那些不可能的路径,因而减轻了译码的工作量。 2.2系统总流程本系统的总流程图如图2-5所示。 其主要功能模块有: 系统初始化、数据接收、读数据、数据判断、显示、维特比译码。 下面对各个部分进行说明。 LCALLSTFSMOVR6,#0CHK2: DJNZR6,K2LCALLSTJSSETBP1.0INITIAL: ;7279初始化程序CLRP1.0D0: MOVR1,#87HD1: DJNZR6,$MOVA,R1MOVA,@R0MOVR6,#04HDECR1DJNZR5,D1STFS: READ: RETWTBYM: MOVR0,#10H;维特比译码主体程序(求状态历史记录和累计误差)MOVR1,#44HMOVA,@R0MOVR2,AMOVR3,#00HLCALLCMPSETBP1.2JS1: SETBP1.1MOVC,P1.2RLCADJNZR7,JS1CHANG: MOVR7,#06H;串口收到的12字节,转换为6字节程序C0: 如果键号为“3”,则对接收到的数据进行译码并显示译码结果;如果键号为“4”,对7279进行初始化;如果是其它键号,则不做任何处理。 其程序流程在主程序流程图2-5中已经体现出来。 2.7显示部分显示子程序能够将接收到的数据或译码结果直观的在数码管上显示出来。 显示子程序有3个,分别为DISP1、DISP2、DISP3,它们分别用于显示接收数据的前8位、接收数据的后4位、维特比译码结果。 现以DISP3为例说明显示部分,其流程图如图2-9所示。 图2-9显示子程序流程图图3-1中(2,1,2)卷积码的状态转移图如图2-3所示。 图2-3状态转移图另一种更为常用的描述卷积码的方法是网格图。 该图根据时间的推进来反映状态的转移。 网格图上纵坐标表示状态,横坐标表示时间,每一次状态转移利用连接相邻时间点上两个状态的有向线段来表示。 图2-4是图2-3中编码器所对应的网格图,其中实线表示“0”,虚线表示“1”。 图2-4网格图2.1.4卷积码的译码卷积码的译码方法可分为两大类。 一类是代数译码,利用编码本身的代数结构进行译码,不考虑信道的统计特性;SWAPAXCHDA,@R0MOV@R1,ADJNZR7,C0YM: LCALLREADLCALLWTBYM;维特比译码程序LCALLZTSXLCALLOUTPUT采用7279芯片能够节省单片机资源,降低编程复杂度。 1.1总体系统分析本系统的具体设计要求为: 系统框图1.用汇编语音进行(2,1,2)卷积码的译码,并要求在数码管上显示输入的信息;2.用RS232串行芯片实现单片机与计算机的信息传输;3.用RS232串行芯片实现单片机与单片机的信息传输;4.在上位机上显示所传输的译码结果。 1.2系统单元功能模块本系统具有以下单元功能模块: 2.8维特比译码部分维特比译码又可分为维特比译码主程序、求状态历史记录和累计误差子程序、求状态顺序子程序、求译码结果子程序。 1.维特比译码主程序当按键“3”按下时,对接收到的数据进行维特比译码,并将译码结果存于58H-5DH单元中。 维特比译码程序流程图如图2-10所示。 图2-10维特比译码流程图2.求状态历史记录和累计误差子程序状态历史记录表能够记录下维特比译码过程中每一步译码后,状态的变化过程,其所占内存空间为40H-57H。 累计误差记录表能够记录上一次译码结束时的累计误差(可能的发送序列与接收序列的汉明距离)和本次译码结束后的累计误差,其中上一次的累计误差存于30H-33H单元中,本次结束后的累计误差存于34H-37H单元中。 本次设计所接收到的数据总共有6组,所以要将译码分为6步实现。 与分组码不同的是在某一分组编码时,不仅参看本时刻的分组而且参看以前的N-1个分组,编码过程中互相关联的码元个数为nN。 N称为约束长度。 常把卷积码写成(n,k,N-1)卷积码。 正因为卷积码在编码过程中,充分利用了各级之间的相关性,无论是从理论上还是实际上均已证明其性能要优于分组码。 2.1.2卷积码的编码本次设计以(2,1,2)卷积码为例。 图2-1为这种卷积编码器的结构,它的编码方法是: 序列依次移入一个两级移位寄存器,编码器每输入一位信息bi,输出端的开关就在c1和c2之间来回切换一次,输出为c1,i和c2,i,其中c1,i=bi+bi-1+bi-2c2,i=bi+bi-2在设计过程中,要先编写好软件,软件又可分为多个模块,需要对每个模块分别进行调试。 维特比译码是此次设计的核心部分。 先编写好维特比译码程序,在Keil中对其进行编译,检查是否存在语法错误,如有语法错误,先要排除所有语法错误;为了进行仿真,需要在仿真前先假定已接收到编码数据001110001011,在维特比译码程序中已经预留了READ子程序,可用来在仿真前将以上6组数据分别写入10H-15H内存单元中;然后可以进行仿真,观察40H-57H单元中的状态历史记录表、60H-66H单元中的状态顺序记录表、58H-5DH中的译码结果是否与理论值一致,如不一致,察看问题出在哪里,对其进行修改,在此过程中可以使用Keil的断点执行、单步执行功能,并随时关注寄存器、关键内存单元中内容的变化,这样可以方便地逐步对维特比译码程序进行完善,最后能够实现正确译码功能。 其它如键盘扫描、数码管显示、数据接收等模块,其程序执行过程与外部输入有关,所以不能使用Keil进行仿真(但可使用Keil对语法错误进行检查),要把这些程序连同维特比译码程序一起烧入单片机中,使单片机与微机进行串口通信,观察实验现象,根据实验现象逐步定位并排除程序或硬件错误,最后要能实现所有功能。 在串口调试助手的发送框中输入001110001011,点击发送按钮(之前波特率要设为1200),查看单片机是不是接收到001110001011,是否译码结果为010100,如果是说明所有模块工作正常。 再将发送框中的001110001011改为000110001011(只要改动不大,其它数据也可以),再次发送,看是否单片机还能够译码为010100,如果是说明所编写的维特比译码程序具有纠错能力。 把另一块编码单片机与此单片机通过MAX232进行连接,重复使用串口调试助手完成的功能,验证两块单片机之间是否能够正常通信。 3.3调试中出现的故障及解决方案MOV35H,AMOV@R1,#02HI图2-12求第1步译码状态历史记录和误差流程图图2-13求第2步译码状态历史记录和误差流程图图2-14求第3,4,5,6步译码状态历史记录和误差流程图3.求状态顺序子程序根据上面求出的状态历史记录表,可以求出状态顺序表,将状态顺序存于60H-66H单元中。 求状态顺序流程图如图2-15所示。 图2-16求译码结果流程图图2-15求状态顺序流程图4.求译码结果子程序根据上一步的状态顺序表,可以查TRANS_TAB表得出维特比译码结果,将译码结果保存在58H-5DH单元中。 MOVSCON,#50H;串行口工作于方式二并开串口接收M0: JNBRI,M1LCALLRECE;如果接收到数据,调用接收子程序M1: MOVC,P1.3JCM2;没有键按下,跳到M2显示程序MOVR0,#16HAJMPD0DISP2: LCALLINITIALMOVR5,#04HMOVR0,#1EHDISP3: MOVR5,#06HMOVR0,#58H已知起始状态为“0”(00),则下一个状态只可能是“0”(00)或“2”(10)(参考图2-4),所以第一步译码只需计算两个累计误差,并将其存于30H、32H单元中即可,第二步译码需根据第一次译码的累计误差求出本次译码完后的累计误差,存于34H-37H单元中,用34H-37H中的内容覆盖30H-33H中的内容,作为下一步的起始累计误差,并将各个状态的前导状态分别存于44H-47H单元中,第三步的译码过程较第二步只需加一个累计误差的比较,淘汰较大的累计误差,以后的译码都是第三步译码的重复,所以从第三步开始可以用循环完成。 假如输入的序列为010100,则接收到的序列(译码后的序列)为001110001011,根据上述过程,可以得到状态历史记录表2.1,其中带阴影的为幸存路径所经历的状态。 表2.1状态历史记录表态状t1234 |

【本文地址】