| 三种编码器协议(Endat\BISS\SSI) | 您所在的位置:网站首页 › 编码器4096是什么意思 › 三种编码器协议(Endat\BISS\SSI) |

三种编码器协议(Endat\BISS\SSI)

|

三种编码器协议(Endat\BISS\SSI) 文章目录 文章目录 前言 一、Endat协议 1.1概述 1.2.功能介绍 1.3.数据传输 1.3.1 补偿延时 1.3.2 确定传输时间 1.3.3 选择传输类型 1.3.4 位置值 1.4 参数存储区 1.5 传输参数 1.6 诊断 1.7 接口 1.7.1 编码器启动特性 1.7.2 初始化过程结束后,必须有一个确定的开机程序。只允许使用EnDat 2.1模式指令。 1.8 设备输入电路 二、BISS协议 2.1.BISS协议概述 2.2. BISS帧结构和数据通信 2.3.BISS通信协议实现方法 2.3.1 硬件解码 2.3.2 软件解码 三、SSI协议 SSI、Endat、HIPEFACE DSL和BISS-C对比 前言 之前写的word分享出来! 一、Endat协议 1.1概述 EnDat信号的前身是SSI信号,SSI信号过高的频率会引起来不及响应。HEIDENHAIN公司,为了提高光栅尺、旋转编码器、角度编码器、伺服传感器等产品的响应速度,EnDat被开发出来。EnDat接口是HEIDENHAIN专为编码器设计的数字式、全双工同步串行的数据传输协议,具有传输速度快、功能强大、连线简单、抗干扰能力强等优点,是编码器、光栅尺数据传输的通用接口。EnDat数据接口用确定的时序传输位置值或附加物理量和读取或写入编码器的存储器。 1.2.功能介绍1. 位置值的传输——可带也可不带附加信息。附加信息类型可通过“存储区选择” (MRS)码选择。其它功能,例如读写参数也可在选择存储区后执行。通过同步传输位置值,还能请求发送反馈环中轴的附加信息并用其执行功能。 2. 参数的读写操作——可以单独执行,也可以与位置值一起执行。选择存储区后,可以读或写参数。 3. 复位功能——用于发生故障时对编码器进行复位。复位可以在位置值传输期间或非 传输期间执行。 4. 测试指令和值——用于高安全性控制系统的强制动态采样。对出错信息进行反相处 理以便监测是否生成出错信息。 1.3.数据传输 1.3.1 补偿延时进行补偿可以提高,时钟频率和传输距离。如图为时钟频率和有无补偿以及传输距离的关系图。图中所示的允许时钟频率为时钟占空比为1:1的情况。

图3.1 时钟频率、有无补偿和传输距离的关系图 1.3.2 确定传输时间每次更换传输线硬件设备后,必须重新确定传输时间参数,最好每次开机后自动确定。 确定方法:后续电子设备给编码器发送模式指令“ 编码器传输无附加信息的位置值 ”。当编码器切换为传输状态后,即正好10个时钟周期后,后续电子设备中的计数器开始数每一个上升沿。后续电子设备测量最后一个时钟脉冲上升沿与起始位沿之间的差,将时钟频率时钟频率 [kHz]无延迟补偿有延迟补偿时钟占空比时钟其作为传输时间。消除计算传输时间过程中的不稳定因素,必须执行这个测量过程三次以上并测试测量值的一致性。用较低时钟频率测量信号传输时间(100 kHz至200 kHz)。为达到足够高精度,位置值采样的内部频率必须是数据传输时钟频率的八倍以上。 1.3.3 选择传输类型传输的数据类型分为位置值,位置值及附加信息或参数。发送的信息类型由模式指令选择。模式指令决定被传输信息的类型。每个模式指令包括三个Bit。为确保信息发送可靠,每个Bit均采用冗余发送(反相或冗余)。如果编码器检测到不正确的模式传输,将发送一个出错信息。EnDat2.2能在传输位置值的同时在附加信息中传输参数值。因此它能保证当前位置值始终提供给控制环,甚至包括请求参数时。

图3.2 指令模式 1.3.4 位置值

图3.3 不带附加信息时序图 ①数据包发送与数据传输同步。传输周期从第一个时钟下降沿开始。编码器保存测量值并计算位置值。 ②两个时钟脉冲(2T)后,设备发送模式指令 ③编码器成功计算绝对位置值(tcal)后,从起始位开始由编码器向设备传输数据。后续“错误位”,“错误1”和“错误2”(只适用于EnDat 2.2指令)是所有监测功能的信号,用于监测故障。这两个信号相互独立地生成,它表示编码器发生可导致不正确位置值的故障。发生故障的确切原因保存在“工作状态”存储器中,并可被详细地查询。 ④然后编码器从最低有效位(LSB)开始发送绝对位置值。其长度取决于所用编码器。发送一个位置值所需的时钟脉冲数保存在编码器制造商参数中。 ⑤位置值的数据发送以循环冗余校验(CRC)结束。EnDat 2.2在循环冗余检查后发送附加信息1和2,每个都以CRC结束。附加信息内容由存储区选择决定,并在下个采样周期中发送附加信息。然后每个采样周期都发送该信息直到选择新存储区改变内容为止。 ⑥数据字结尾处,时钟信号必须置为高电平。10至30 µs后或1.25至3.75 µs(EnDat2.2可用参数调整的恢复时间tm)后,数据线返回低电平。然后,时钟信号启动新的数据传输。 表3.1 参数值取值范围

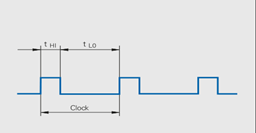

无延迟补偿 有延迟补偿 时钟频率(Fc) 100KHz—2MHz 100KHz—16MHz 计算位置时间(Tcal) EnDat 2.2编码器的典型值:≤ 5 µs,最长12 ms 恢复时间 tm EnDat 2.1:10至30 µs EnDat 2.2:10至30 µs或1.25至3.75 µs(fc ≥ 1 MHz) (可用参数调整) tR 最大500 ns tST / 2-10us 数据延迟时间(tD) (0.2 + 0.01 x 电缆长度,单位为m) µs 脉冲宽度 tHI 0.2-10 µs

TLO 0.2-50 ms 0.2-30 µs(LC) 电平由高转为低的脉冲宽度 变化最大10%

1.3.5 附加信息 根据发送类型,可以随位置值发送一个或两个附加信息(用MRS码选择)。每条附加信息长度为30 bit并以低电平位开始。每条附加信息均以CRC结束,这个CRC由相应无第一个Bit或CRC的附加信息构成附加信息内容由模式指令选择的存储区决定。每个时钟脉冲将发送更新的内容,直到有新请求时。

图3.6 附加信息内容 WRN–警告:这个集合位用于表示编码器是否达到或超过某公差范围,报警的原因保存在编码器存储器中。相应编码器支持的报警和警告信号保存在“编码器制造商参数”存储区中。 RM–参考点:RM位表示是否已执行参考点回零操作。绝对式编码器的RM位始终保持高电平。 Busy–参数请求:低电平时,Busy位表示可以请求发送参数(读取/写入)。如果正在处理一项请求(高电平),将不允许访问编码器存储器。

图3.7 选择附加信息的MRS码 1.4 参数存储区编码器提供多个保存参数的存储区。后续电子设备可以读取存储区中的信息,其中有些信息还允许编码器制造商、OEM厂商甚至最终用户写入。也有些存储区是只读的。其中包括:编码器制造商参数、OEM厂商参数、工作参数、工作状态。

版本:EnDat 2.1

图4.1 传输参数

图4.3 EnDat 2.2传输一个位置值和附加信息中参数值的典型指令顺序 注:查询内置EEPROM的最长访问时间为12 ms 1.6 诊断诊断数据的信息组成和查询: • 必须激活所需有效数字。 • 通过附加信息1发送值(8 bit)。 • 周期性地输出值;地址和值。 • 支持的有效数字信息保存在EnDat 2.2参数中。 • 诊断信息可在闭环工作模式下发送。 • 显示时应忽略“边界区”(需要定义预留区)。 • 后续电子电路必须忽略“未知地址”(系统数据)。 1.7 接口 1.7.1 编码器启动特性内置电路大约需1.3 s的初始化时间,应考虑这个初始化过程。

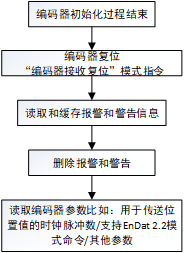

图7.1 内置电路初始化过程约1.3S 1.7.2 初始化过程结束后,必须有一个确定的开机程序。只允许使用EnDat 2.1模式指令。

图7.2 开机程序 1.8 设备输入电路

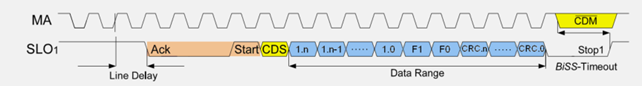

数据(测量值或参数)可以在位置编码器和设备之间进行双向传输,设备的收发单元支持RS-485(差分信号),数据传输与后续电子设备生成的时钟脉冲同步。IC1:RS 485差动线路接收器和驱动器、C 3 = 330 pF、Z 0 = 120 Ω。 二、BISS协议 2.1.BISS协议概述BiSS 通信协议是一种全双工同步串行总线通信协议,专门为满足实时、双向、高速的传感器通信而设计,在硬件上兼容工业标准 SSI(同步串行接口协议)总线协议。其典型应用是在运动控制领域实现伺服驱动器与编码器通信。BiSS 由德国 IC-HAUS 公司开发,现已成为传感器通信协议的国际化标准。 2.2. BISS帧结构和数据通信图9.1描述了 point-to-point 组网时的 BiSS 通信帧。MA 由 Master 发出用于驱动通信,SL 是 Slave 发出的数据信号。完成 1 个 BiSS 通信帧表示 Master 收到 1 帧数据。

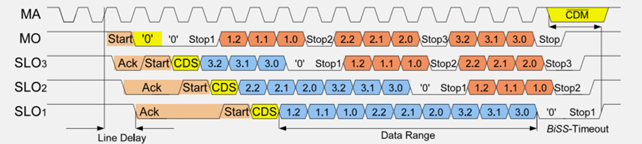

图9.1 point-to-point 组网的BiSS帧结构 图9.2 描述了 Multi-slave Networking 组网的 BiSS 通信帧,对于每一个 Slave 而言,不但要发送自己的数据,而且要接收并转发前一个 Slave 发过来的数据。

图9.2 Multi-slave Networking 组网的 BiSS 帧结构 BiSS 通信过程可以描述为如下几个状态的切换:IDLE(空闲),Start Frame(帧开始),Tranmission(发送),Timeout(超时)。BiSS 通信空闲,MA,SL 保持常高。 ①Start Frame,开始帧通信MA 发送时钟,在 MA 第一个上升沿,Slave 锁存传感器状态。在 MA 第二个上升沿,编码器将 SL 拉低,用于应答 Master 的通信请求。 理想状态下,SL 拉低与 MA 第二上升沿的时延很小,在实际系统中,由于长线延迟、信号整形、滤波以及信号传递通过多级门电路等因素的综合作用,SL 相对 MA 信号存在一定的相移,造成 SL 拉低滞后 MA 第二上升沿一段时间,这个时间被称为 line-delay 线路延迟,如果 SL 信号采样电路不能修正这个延迟,那么总线的通信距离和通信速率都要降低,以保证 SL 信号被可靠地采样。BiSS 规定每个通信帧发起时都要检测一次 line-delay,并加以修正。从而确保 BiSS 通信波特率可以达到 10Mbit/s。在 line-delay 期间,MA 持续输出脉冲。 ②Tranmission,(发送)当 SL 信号从常高拉低后维持一段时间。这段时间叫 ACK,表示 Slave 响应了 MA 信号,正在进行数据准备。通常 ACK 维持 0.1us 到 8us 之间,这与 Slave数据是否准备就绪有关,对于特定的 Slave,其 ACK 的长度是基本上是固定的。ACK 期间MA 持续输出脉冲。当 SL 发送 1 个 BIT 的 START 位(常‘1’),表示 Slave 数据准备就绪。开始数据发送。 数据包括: (1) 1 个 BIT 的 CDS 信号 (2) 1 个SCD(长度要大于 4 个 BIT,小于 64 个 BIT) 字段长度由 Slave 厂商规定(例如:禹衡公司多圈编码器的单周期位域包括 16 个 BIT 的多圈计数、17 个 BIT 的单圈位置,2 个BIT 的错误告警和 6 个 BIT 的 CRC 校验)。这个期间,MA 持续输出脉冲。 其中两个BIT的错误告警如图9.1中F0位和F1位,紧跟其后的6个BIT的CRC校验。 ③Timeout,(超时)当 SCD 发出完成后,SL 维持 0.5~40us 的低电平,这个时间段被称为 Timeout,对于特定的应用,Timeout 由 Slave 厂商规定。MA 在 Timeout 期间发送 CDM信号,该信号一直维持到 SL 被拉高,SL 被拉高后,本次通信完全结束。 2.3.BISS通信协议实现方法2.3.1 硬件解码 对于采用硬件解码的用户,可以根据需要选择 IC-HAUS 提供的解码芯片,或者采用 IC-HAUS 提供的 IP 核进行解码。如果想利用 IC-HAUS 提供的 IP 核实现数据通信和寄存器两种功能,需采用 FPGA 解码。FPGA 资源数需大于 1300 个 LE 或等效资源数。如果仅想实现数据通信,可以采用 CPLD 解码。CPLD 资源数需大于 180 个 LE 或等效资源数。自行设计的难点是线延迟的处理,对于外引线很短或无外引线的应用,线延迟的变化很小,这时可以设计延迟固定的采样时钟,否则每个周期要进行一次线延迟补偿。直接购买解码芯片或使用验证过的 IP 核能够快速实现 BiSS 通信。 2.3.2 软件解码用户可以通过 IO 模拟的 BiSS 时序,但这种方法不推荐使用。推荐使用 MCU 的硬件外设解码,这样将 BiSS 通信速度设定很高。而且节约了外部逻辑电路的成本,对于很多应用,节约的本十分可观。SPI 的 SCK 可以用来模拟 MA,MISO 可以模拟 SL。这样用需考虑三个问题: 1、 MCU 硬件模块的 FIFO 深度。有些 MCU,外设的 SPI 寄存器长度是固定的(STM32SPI读取固定8位或者16位),完成一帧 BiSS 通信需通信多次,中断多次。结果造成 MA 的波形不连续。这可能带来问题,造成通信出错。 2、 MCU 硬件模块是否具备线延迟补偿的能力。具有线延迟补偿能力的外设,可以应对实际应用环境的变化带来的影响,可以是需求的变化,环境的变化,老线路化等等。具有线延迟的系统,其可靠性和适应性比没有线延迟补偿的系统高得多。 3、 CRC 解码能力,CRC 校验对 MCU 的处理能力提出了要求。使用 MCU 进行解码要充分考察不同 MCU 外设的特点和处理能力,以及芯片厂家技术支持的力度,是否有成熟的设计等等。 三、SSI协议

图2 SSI数据读取时序 1.时钟信号的第一个下降沿,单稳态电路被激活,并行/串行转换器上的数据存储到转换器。 2.第一个时钟上升沿传送存储器数据最高位MSB至数据信号线上。 3.时钟信号处于下降沿(信号处于稳定状态),控制器从数据信号线上获得所需要的电平,单稳态电路再次被激活。 4.随着上升沿的到来数据一个个被读出,直到最后一位传输完毕,数据线跳至低电平持续Tm时长,单稳态电路恢复。 5.一旦单稳态电路恢复数据信号转为高电平,并且单稳态电路不工作。 Tm:编码器识别数据传输完成的时间间隔(20us—+∞) Tp:两个连续时钟之间的延迟(应该大于21us) Twmax : 19us,Tw小于此时间可以连续进行数据采集,数据一致

图3 SSI两次数据读取时序 Tw器件器件数据一直为低电平。如果Tw < 19us,相当于读取两次,两次读取到的数据一样,大多数SSI设备实现多重传输,可以通过重复读取相同的数据字来提高传输安全性,编码器在SSI超时发生之前不会更新数数据。通常两次传输就足以保证安全传输。SSI协议当中规定时钟频率应该在80KHZ—2MHZ之间。

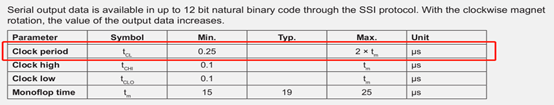

图4 RM08时钟规定 不同的器件时钟频率有不同的规定,RM08器件数据手册当中规定:时钟频率在20KHZ—4MHZ之间,对于Tm也有规定在15-25us之间。

时间要求 SSI协议 RM08 Tm 20us—+∞ (15-25us)—+∞ fTclk 80KHZ—2MHZ 20KHZ—4MHZ Tw

max19us 注:SSI协议最主要的就这三个时间限制。 STM32例:模拟方式实现 uint16_t SSI_CLOCK(uint8_t ssi_bits) { volatile uint16_t data = 0; uint8_t s=0; HAL_GPIO_WritePin(CLOCK_GPIO_Port,CLOCK_Pin,GPIO_PIN_SET); //GPIOx->BSRR = (uint32_t)GPIO_Pin BSRR = GPIO_Pin; delay_uss(1); HAL_GPIO_WritePin(CLOCK_GPIO_Port,CLOCK_Pin,GPIO_PIN_SET); //GPIOx->BSRR = (uint32_t)GPIO_Pin |

【本文地址】

图3.4 时钟频率tHI和tLO

图3.4 时钟频率tHI和tLO 图3.5 包括位置值和附件信息1和2的数据包

图3.5 包括位置值和附件信息1和2的数据包

图4.2 Endat读写时序

图4.2 Endat读写时序