| Zebu基本使用说明 | 您所在的位置:网站首页 › 结构胶多久可以粘牢 › Zebu基本使用说明 |

Zebu基本使用说明

|

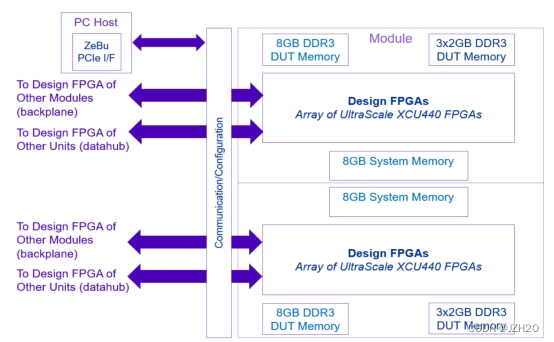

1. ZS4一块module共有12块VU440,其基本架构如下:

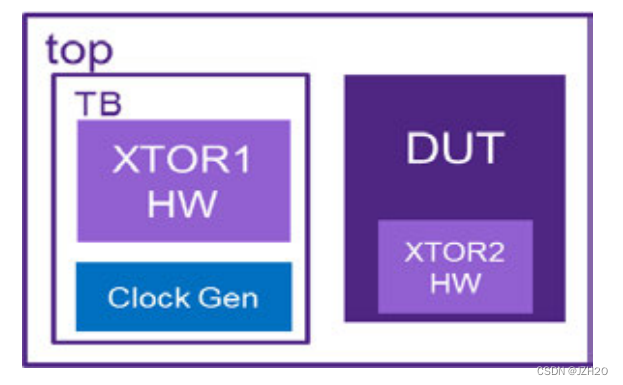

2. 主要特性 ZeBu Server 支持多种软硬件调试模式: 支持原型验证支持验证加速,及带宽分析支持低功耗仿真 服务器每个module都通过PCIE与runtime机器互连, 可以支持多用户同时使用。3. 仿真设计过程 要将设计和测试环境映射到模拟,必须根据设计和测试平台执行以下操作之一: 当模拟环境可用于您的设计时,您可以保留与现有顶级模块相同的体系结构。当DUT和testbench作为单独的元素可用时,您需要创建一个额外的顶级包装器。3.1.1 从模拟环境中导入设计 要从模拟环境中导入DUT及其测试环境,请保留现有的顶层模块,并执行以下步骤: 实例化时钟生成原语以连接到DUT时钟。实例化与DUT交互的事务器。下图显示了在顶级模块中实例化的时钟生成器和事务器

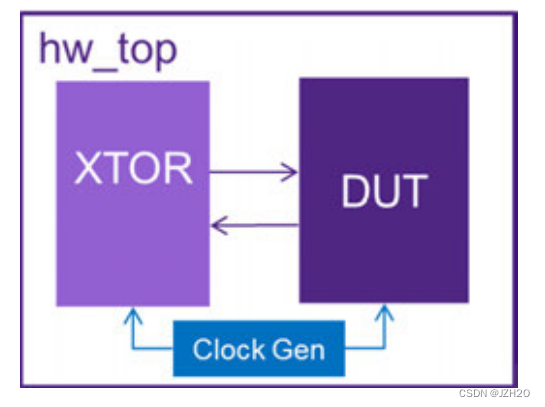

3.1.2 单独创建DUT测试环境 当DUT和测试平台(testbench)作为单独的元素可用时,您需要创建一个附加的Verilog顶级包装器,它将设计与验证环境(testbench or transactors)连接起来。然后,在这个包装器中实例化时钟。

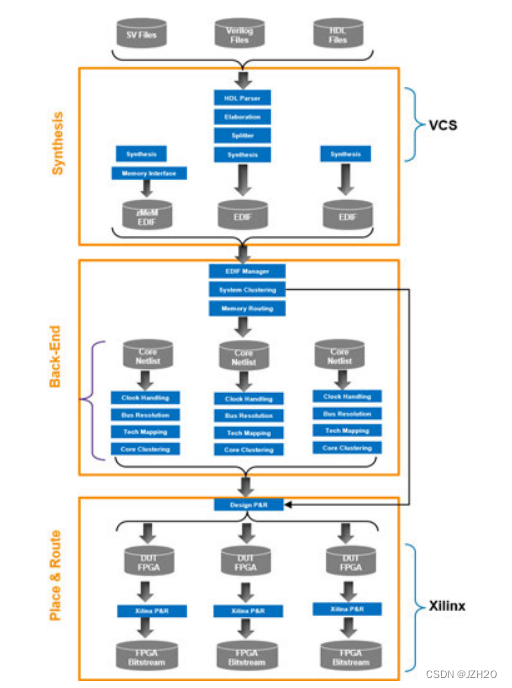

单独创建DUT测试环境 3.2 时钟模块 主时钟用专用的时钟,该时钟可以在HDL中的任何地方实例化。您必须实例化至少一个时钟,并且可以使用最多16个时钟。 可以通过 zceiClockPort 来实例化一个时钟,例如 zceiClockPort ClockPort (.cclock(clk)); 这里的 cclock 是一个连接在 cclock 引脚的控制时钟信号 3.3 复位模块 复位信号也可以在测试平台环境中直接编程,通过声明信号由软件控制或在运行时强制接受用户定义的值。有关强制重置的更多信息,请参见 Forcing and Injecting Values 。 根据您的测试台,可以提供如下复位信号: 如果使用zRci来控制您的测试平台,则zRci应该控制复位信号。如果有一个基于周期的测试台,测试台应该提供DUT复位信号。如果有一个基于事务(transaction)的测试平台,事务处理(transaction)程序应该提供DUT复位信号。请注意:不要使用zceiClockPort作为复位输出 3.4 存储模块 ZeBu Server实例化由ZeBu编译器的内存生成器生成的sram类型的内存模型。这些模型适用于设计和测试平台的内存。 你可以用以下方法为内存建模: 描述HDL中的内存数组声明和进程块中的内存访问。实例化可用的内存模型Intellectual Property (IP)。本节由以下各小节组成: 设计接口 存储模块IP4. 编译说明 4.1 基本编译流程 通过统一编译流程,设计和测试环境都是由VCS编译器编译,该编译器由一个以统一Tcl格式(UTF)文件。 UTF项目文件(例如project.utf)是ZeBu编译器的主要输入文件。它包含成功编译所需的所有信息,包括VCS编译命令和ZeBu后端编译。在编译项目文件时,VCS解析HDL并详细说明设计。可以从现有的模拟环境中重用VCS编译脚本,以减少设计启动时间。整个编译流程由zCui控制,这是一个图形用户界面(GUI),用于ZeBu编译。zCui启动VCS进行前端合成,然后是后端编译,以及Xilinx FPGA Place和Route。 下图说明了ZeBu编译流程。

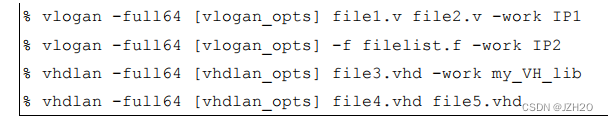

4.1.1 UTF基本说明 UTF相关帮助命令命令 描述 vcs -help utf+all 显示所有帮助指令 vcs -help utf+ 显示命令的详细帮助信息 vcs -help utf+\* 显示所有命令的详细信息 UTF基本命令architecture_file -filename { } 指定硬件结构文件 grid_task_association –task {} –queue {} grid_cmd queue {} –submit {} –njobs 建立工作队列系统 vcs_exec_command{} 指定vcs脚本文件 vcs_exec_command {./vcs.csh} set_hwtop –module 指定设计顶层 set_hwtop -module {project_tb} 4.2 VCS编译脚本 4.2.1 VCS创建 设置VCS的步骤如下: 将环境变量$VCS_HOME指向VCS的安装路径。另外,$PATH环境变量应该包含PATH环境变量应该包含 $VCS_HOME/bin4.2.2 synopsys_sim.setup文件设置 在多重设计或VHDL/VHDL- mx设计的情况下,必须使用synopsys_sim.setup文件,synopsys_sim.setup 文件将逻辑库名称(使用analyze命令中的-work选项)映射到物理库目录(对应逻辑库分析内容的UNIX目录)。VCS从以下位置寻找synopsys_sim.setup文件(从最高优先级到最低优先级): 命令设置路径 % setenv SYNOPSYS_SIM_SETUP 当前目录下的synopsys_sim.setuphome目录下synopsys_sim.setup安装目录下($VCS_HOME/bin/synopsys_sim.setup)4.2.3 用utf创建编译命令 必须向UTF命令 vcs_exec_command 提供编译脚本(或命令行),以便解析和细化设计,该脚本应该包含以下两个命令: 解析HDL文件的命令(Verilog/System Verilog为vlogan, VHDL为vhdlan),例如:

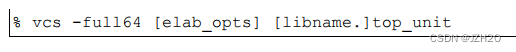

其中: top_unit :顶级模块名或顶级v2k配置。 libname :指定顶层模块和配置的库名(可选,如果没有指定,顶层模块和配置将在synopsys_sim.setup中搜索)。 4.2.4 Designware 编译设置 要设置DesignWare构建块(DWBB)的编译设置,请执行以下步骤: 1. 将$SYNOPSYS环境变量设置为SYNOPSYS编译(DesignCompiler)的安装路径。 2. 将逻辑库映射到synopsys_sim.setup中的适当文件。 3.在VCS脚本中,添加如下命令: a.为每个库创建工作目录,示例如下: mkdir dware b.增加DWBB组件源文件(加密的VHDL和Verilog文件)的分析命令(vhdlan/vlogan),示例如下: vhdlan –full64 -work dware $SYNOPSYS/dw/fpga_ip/fv/dw_foundation/dware_comp.vhd.e vhdlan –full64 -work dware $SYNOPSYS/dw/fpga_ip/fv/dw_foundation/dware.vhd.e 如果设计目标是低功耗,请使用特定的最小功耗库。有关示例的详细信息,请参阅关于SolvNetPlus的文章。 4.3 指定编译硬件架构 硬件架构文件zse_configuration.tcl,在ZeBu安装过程生成。这个文件标识ZeBu硬件架构,可以在$ZEBU_SYSTEM_DIR/config/目录中找到。 例如: architecure_file -filename {/u/tools/ZEBU_SYSTEM/zs3_config/zse_configuration.tcl} 4.4 编译过程中的流程选择 为了提供稳定和高性能的编译,可以使用以下命令启用duri编译: set_perf_flow 其中值:base ,flow1,flow2 注意如果您正在使用HAPS,则必须按照以下方式设置目标: set_perf_flow HAPS |

【本文地址】