| fpga[1]计数器(附源码) | 您所在的位置:网站首页 › 扫码计数器软件 › fpga[1]计数器(附源码) |

fpga[1]计数器(附源码)

|

计数器

介绍1.创建项目文件夹2.绘制波形图3.编写rtl代码4.编写testbench代码5.上板验证6.总结

介绍

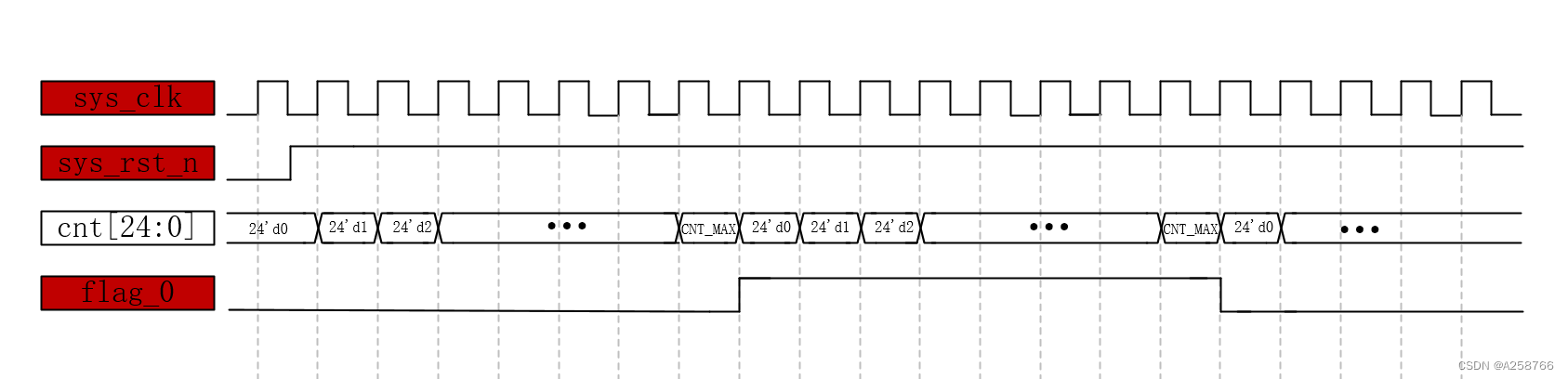

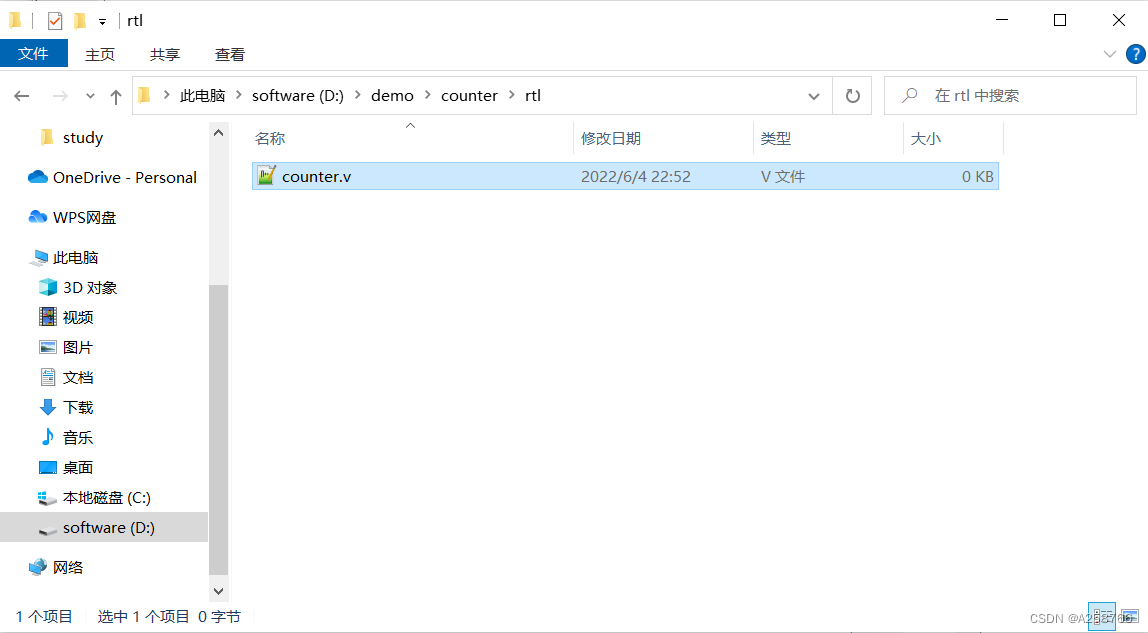

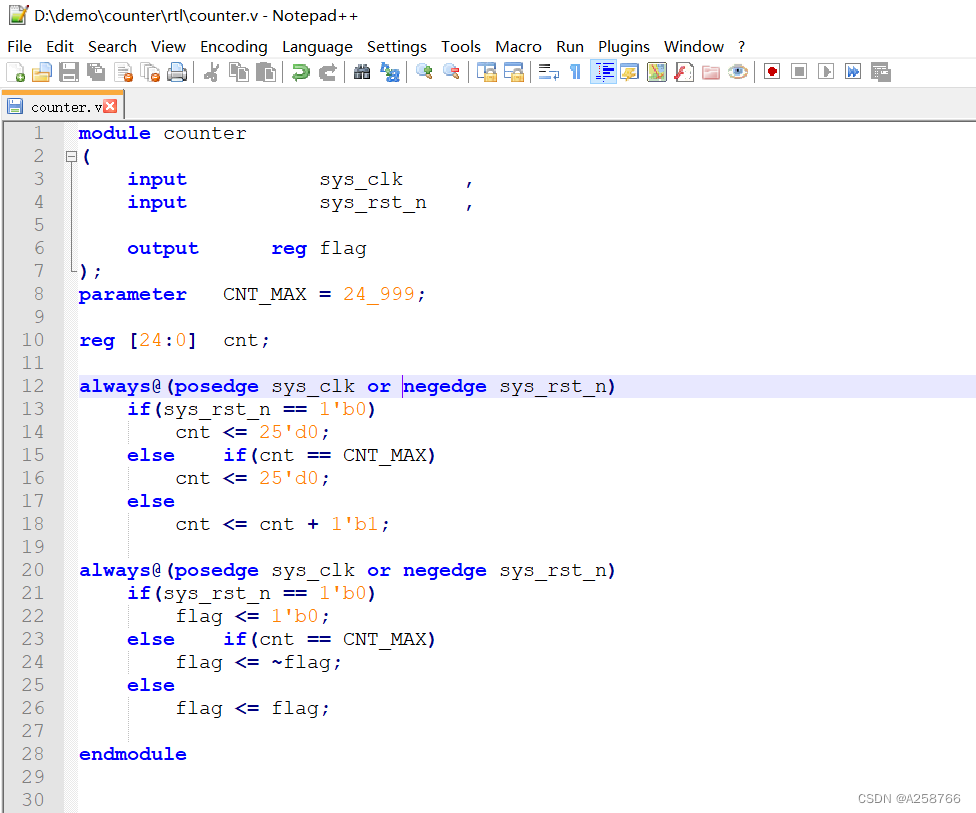

计数器电路是在数字电子技术中应用的最多的时序逻辑电路。计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。 在许多大型电路中必然有计数器电路的身影,可以说了解并掌握计数器的设计方法是学习fpga的第一步。 本文使用的软件是Quartus II 13.1、modelsim和notepad++,开发板是黑金的AX301。 下图是计数器的基本设计流程。 Created with Raphaël 2.3.0 绘制波形图 依照波形图编写rtl代码 仿真验证功能是否正确 上板验证 yes no 1.创建项目文件夹首先我们先创建一个存放项目的文件夹: 对于计数器这个时序逻辑电路来说,需要时钟的驱动,复位方式选择异步复位。 同时,需要定义一个变量cnt来对时钟进行计数(后续需要利用LED来验证代码,此处先将cnt的位宽设置为25),计数值满时将flag进行取反。 最后将文件存放在visio文件夹中 我们在rtl文件夹下建立名为counter的.v文件 |

【本文地址】

公司简介

联系我们

再分别在counter内创建用来存放工程文件、rtl代码和波形图的文件夹:

再分别在counter内创建用来存放工程文件、rtl代码和波形图的文件夹:  然后,打开Quartus II软件,新建一个工程文件并存放在我们刚刚建立好的prj文件夹中,命名为counter

然后,打开Quartus II软件,新建一个工程文件并存放在我们刚刚建立好的prj文件夹中,命名为counter  我们使用的开发板是黑金AX301搭载的是Cyclone IV E系列的EP4CE6F17C8,选择对应的型号。

我们使用的开发板是黑金AX301搭载的是Cyclone IV E系列的EP4CE6F17C8,选择对应的型号。  为了方便后续的仿真,我们先将仿真软件设置为Modelsim语言为Verilog HDL

为了方便后续的仿真,我们先将仿真软件设置为Modelsim语言为Verilog HDL

notepad++ 是一款小巧且好用的代码编辑软件,我们在language选项中勾选Verilog语言。 可以看到,notepad++ 对 Verilog语言有了关键字提示。

notepad++ 是一款小巧且好用的代码编辑软件,我们在language选项中勾选Verilog语言。 可以看到,notepad++ 对 Verilog语言有了关键字提示。  编写代码如下:

编写代码如下: