| 输入延时(Input Delay)与输出延时(Output Delay) | 您所在的位置:网站首页 › 延时器的作用是什么呢视频 › 输入延时(Input Delay)与输出延时(Output Delay) |

输入延时(Input Delay)与输出延时(Output Delay)

|

一、设置输入延时(Input Delay)

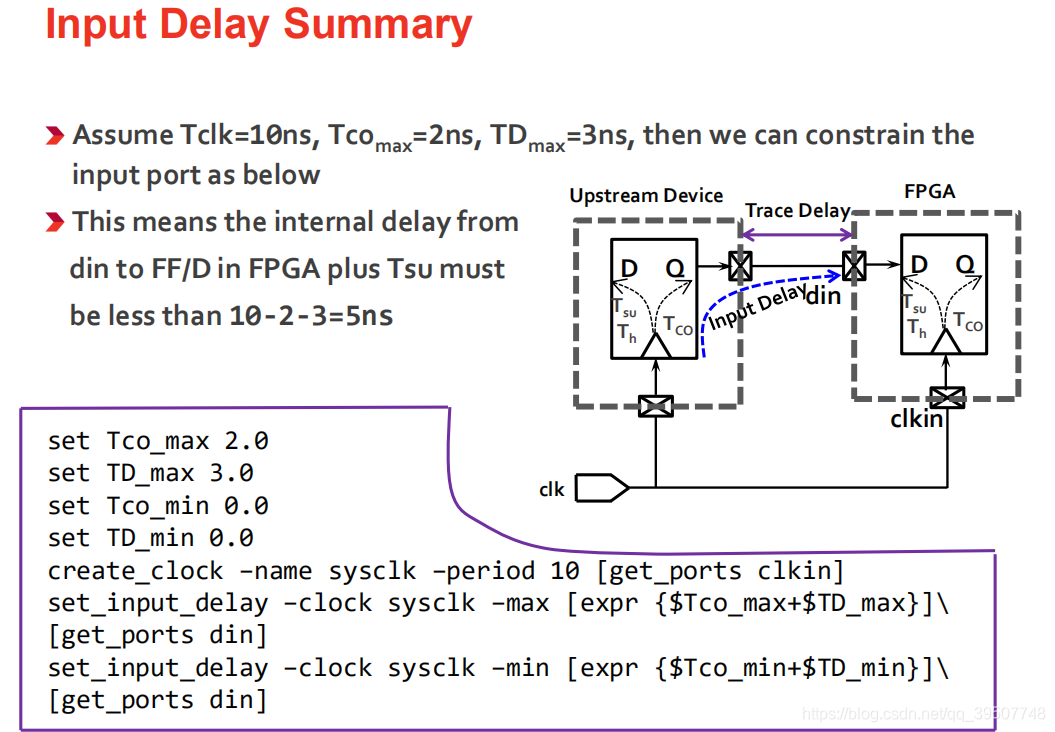

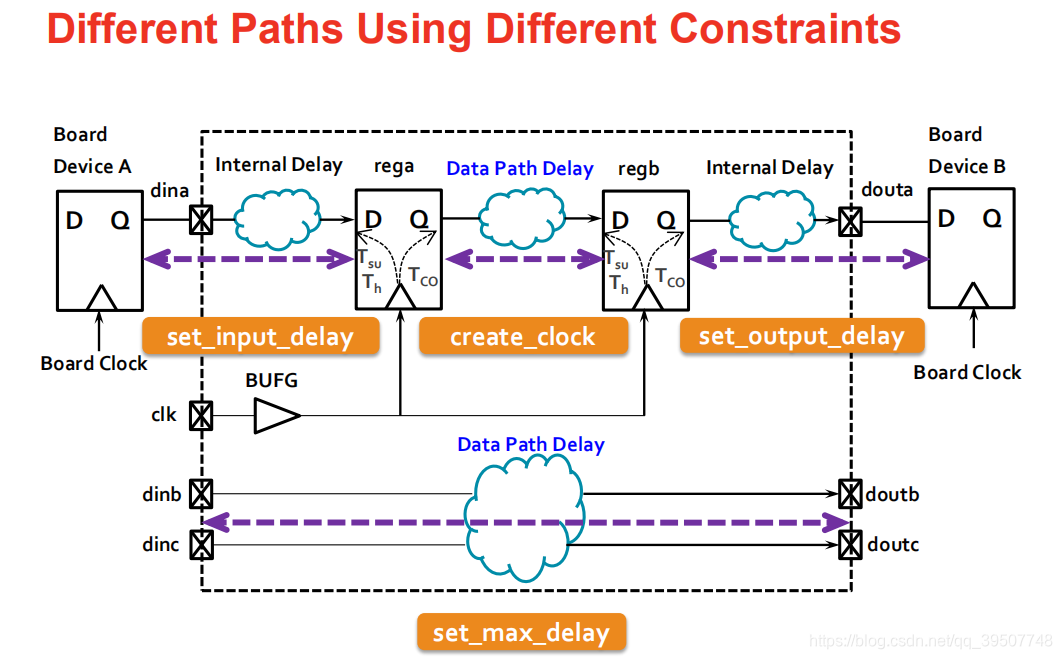

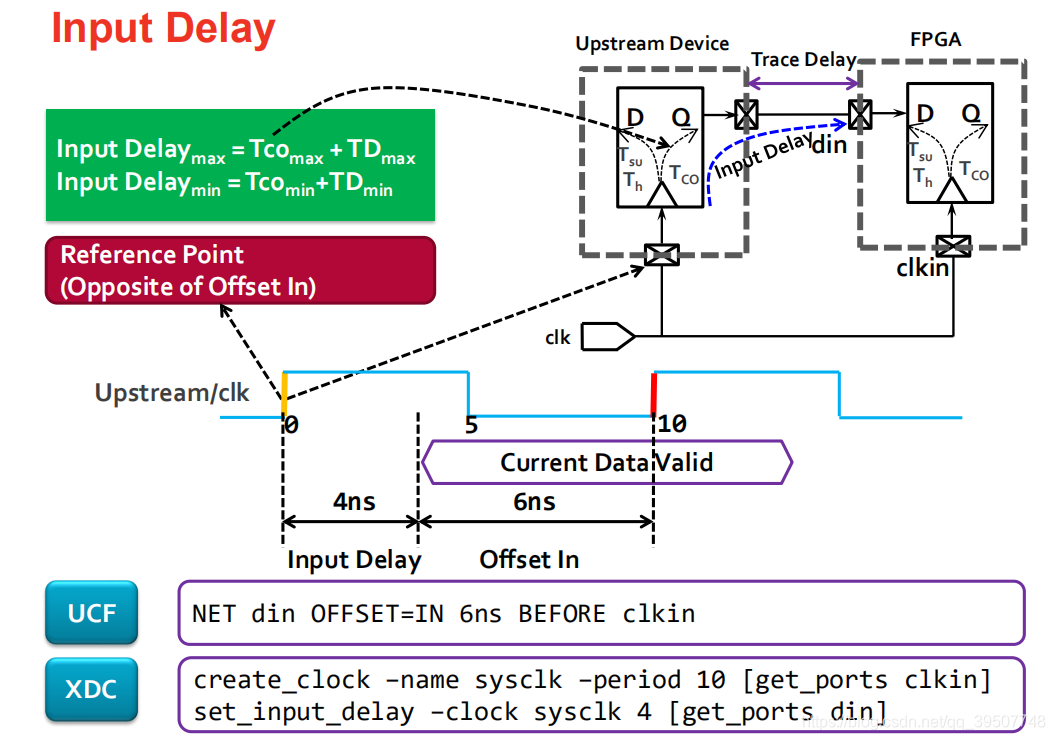

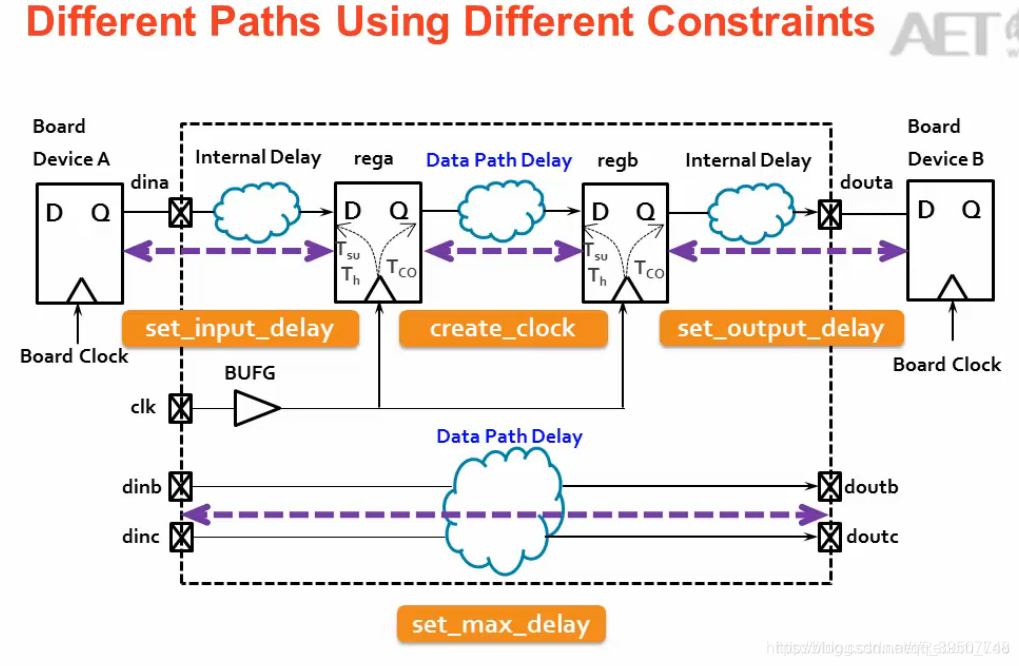

1、不同的路径需要使用不同的约束 由下图可以看出Input Delay是以上游芯片的时钟发送沿为参考,上游的输出数据到达FPGA的外部输入端口之间的延迟。 输入延迟(input delay)包括Tco和Trace Delay(板间延迟),其中Trace delay又叫Board delay。 可以看出它主要把时序路径分为三部分,然后分别计算各部分的延时,最后计算出裕量slack,根据slack的值来判断时序是否正确。 5、设置输入延时 6、DDR输入延时举例 7、静态时序路径 默认情况下,主I/O和内部时钟元件之间的任何逻辑都不是完整静态时序路径的一部分 如果没有其他命令,就不会对与I/O相关的逻辑进行设置/保持检查

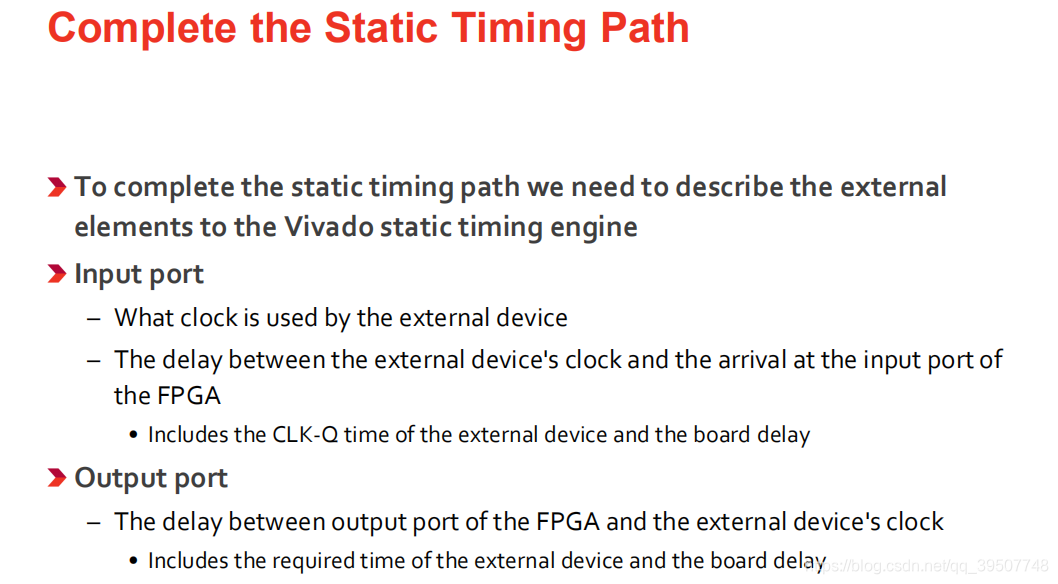

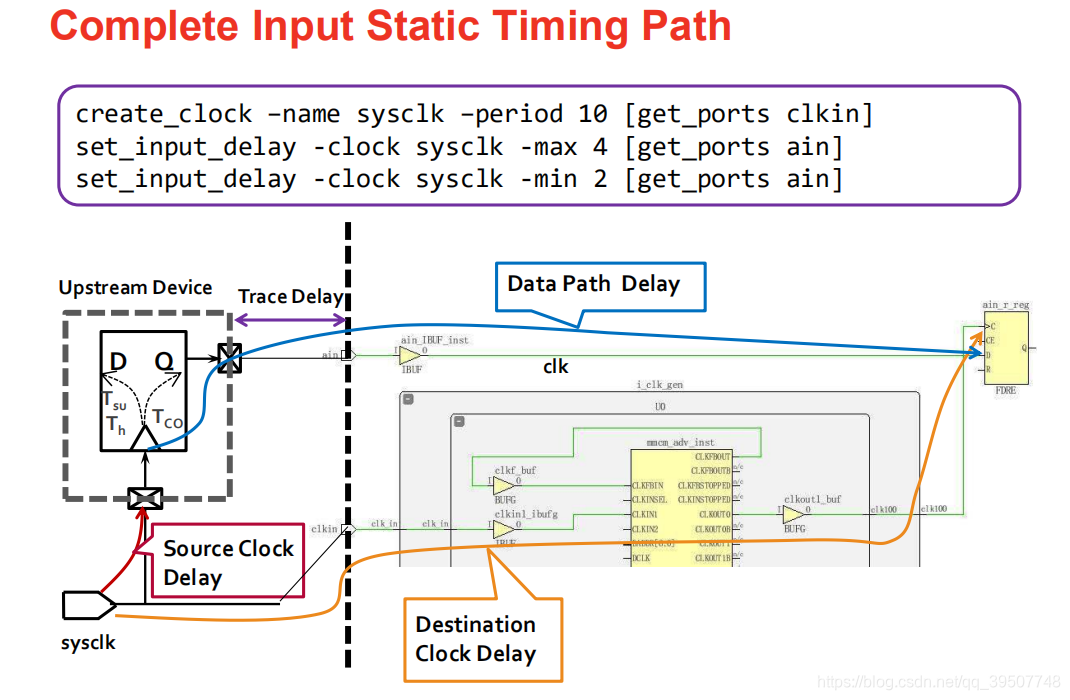

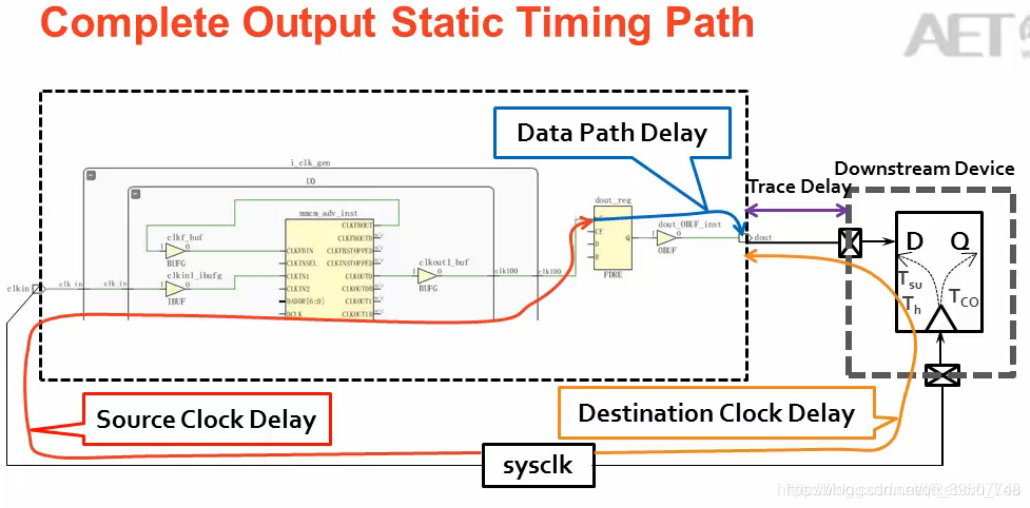

为了获取完整的静态时序路径,我们需要向Vivado静态时序引擎描述外部元素 输入端口: 外部设备使用的时钟外部设备时钟与到达FPGA输入端口之间的延迟;包括外部设备的CLK->Q的时间和板延迟输出端口: FPGA的输出端口与外部设备时钟之间的延迟;包括外部设备需求时间和板延迟 二、设置输出延时(Output Delay)

二、设置输出延时(Output Delay)

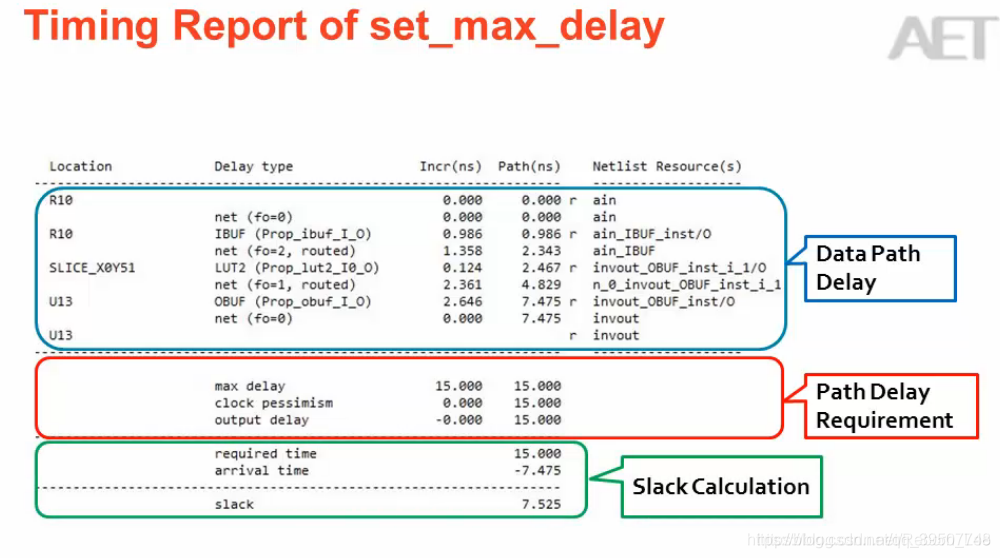

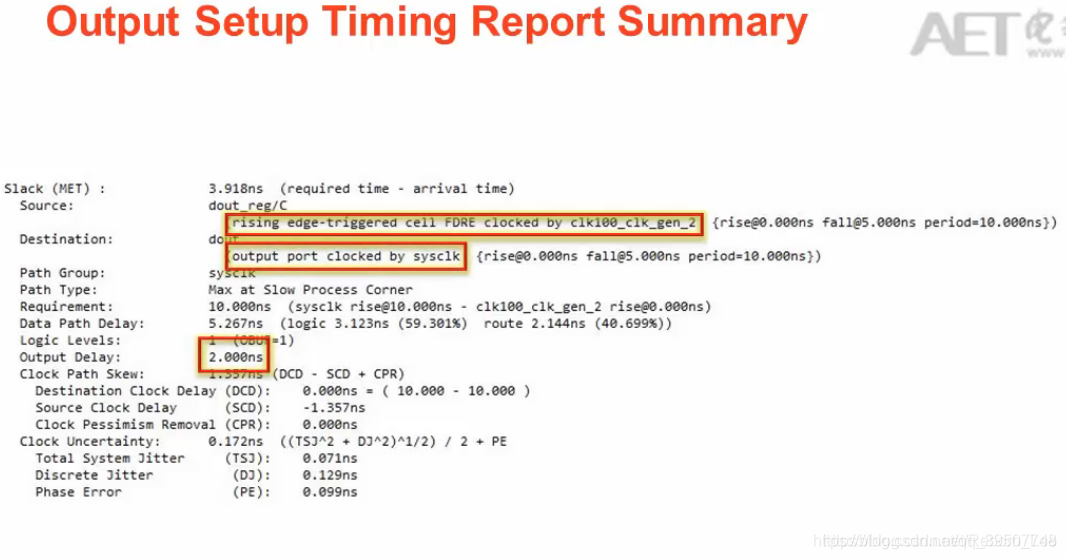

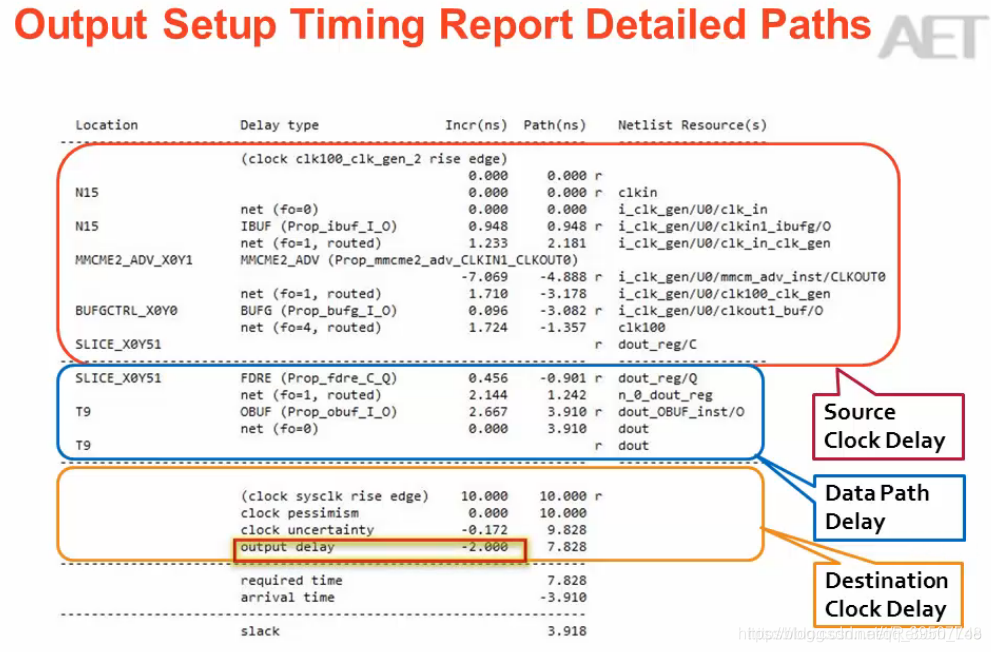

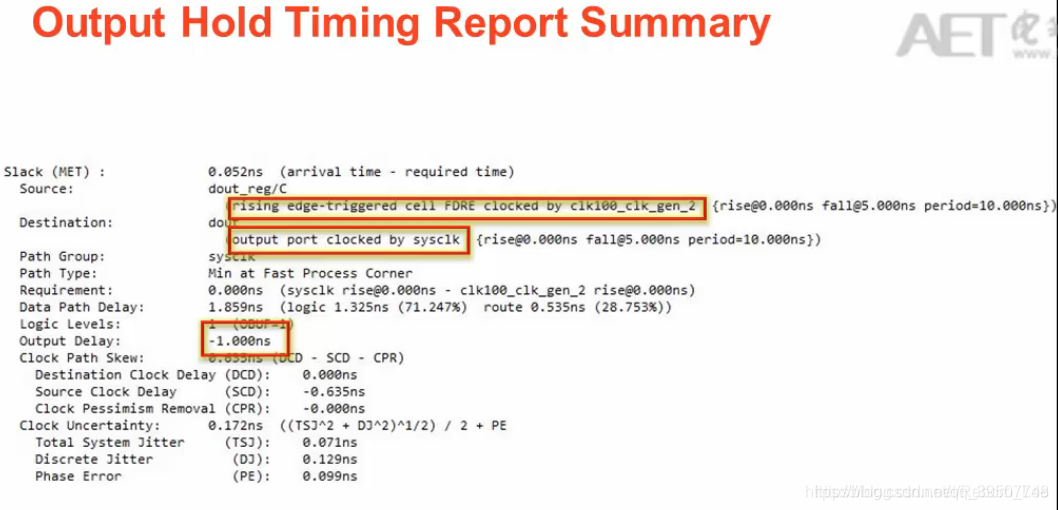

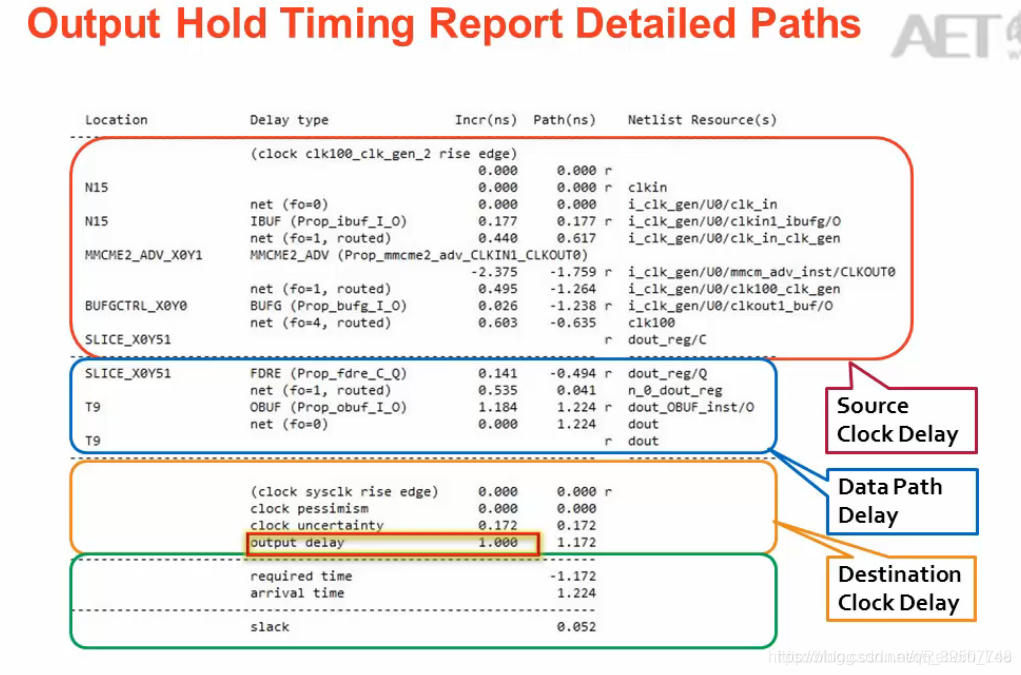

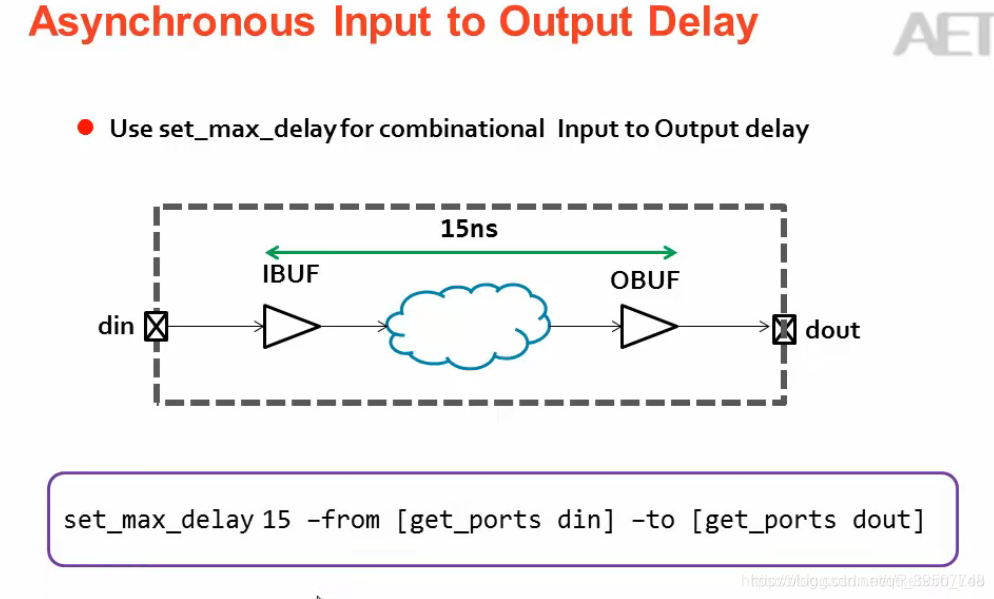

1、不同的路径需要使用不同的约束 3、外部建立和输出时间要求 4、完整的输出静态时序路径 5、输出静态时序分析报告 6、DDR输出延时举例 1、异步输入到输出的延时 最后总结一下,在阅读时序报告时可以发现,时序路径中的三部分在计算延时的时候,基本公式都是: T(source clock path) + T(data path) = 实际的数据到达时间; T(destination clock path) - Ts(或者+Th) = 数据需求时间; 但是: 如果设置了input delay,那input delay应该加到data path delay中;如果设置了output delay,那应该用output delay替换数据需求时间中的Ts或者Th;并且,如果input delay和output delay设置了max和min,那么: 如果是对建立时间进行时序分析,则使用max;并且在T(destination clock path) - Ts中,destination clock path的初始时间是一个clock周期; 如果对保持时间进行时序分析,则使用min;并且在T(destination clock path) +Th中,destination clock path的初始时间为0。 |

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |

2、输入延时的定义

2、输入延时的定义 3、完整的输入静态时序路径

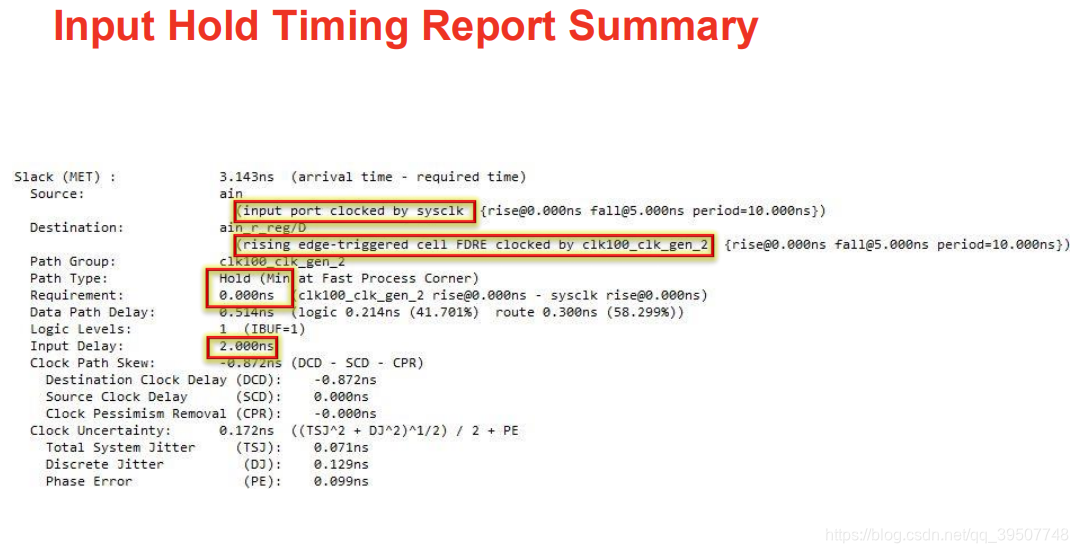

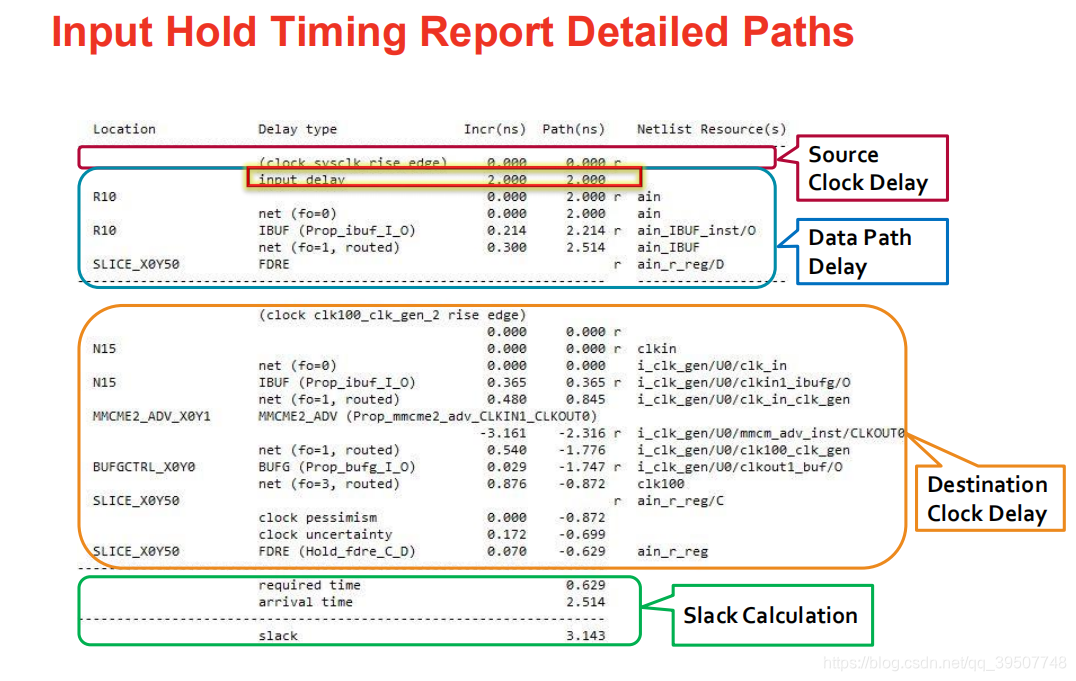

3、完整的输入静态时序路径  4、输入静态时序路径分析报告

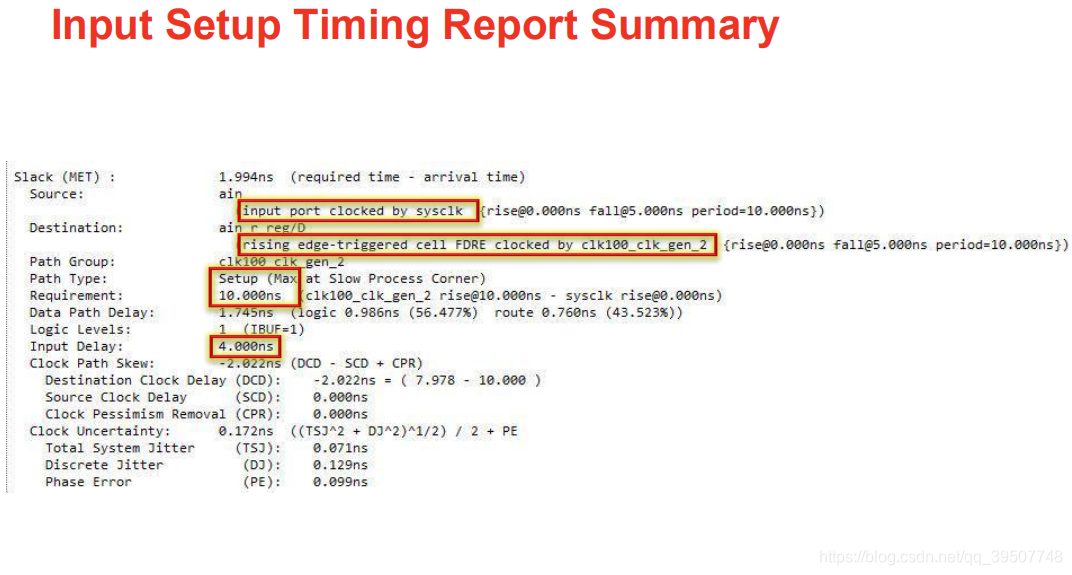

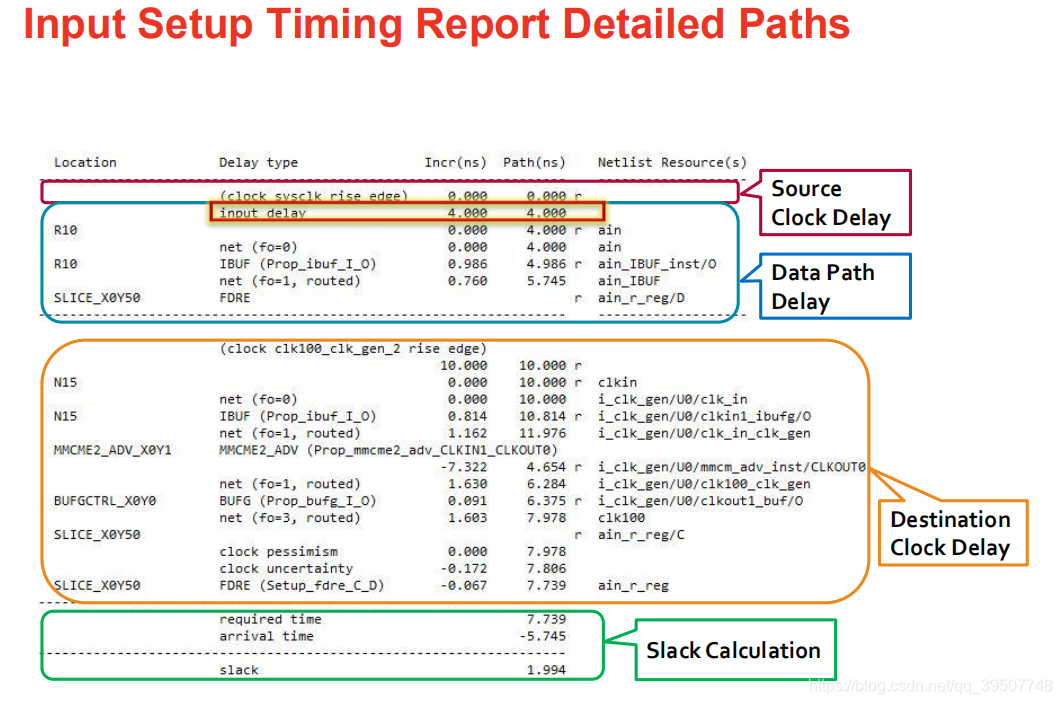

4、输入静态时序路径分析报告

关于时序报告中这几部分的延时为啥要这么算,可以参考这篇文章 传送门 最后的附录部分加以理解。

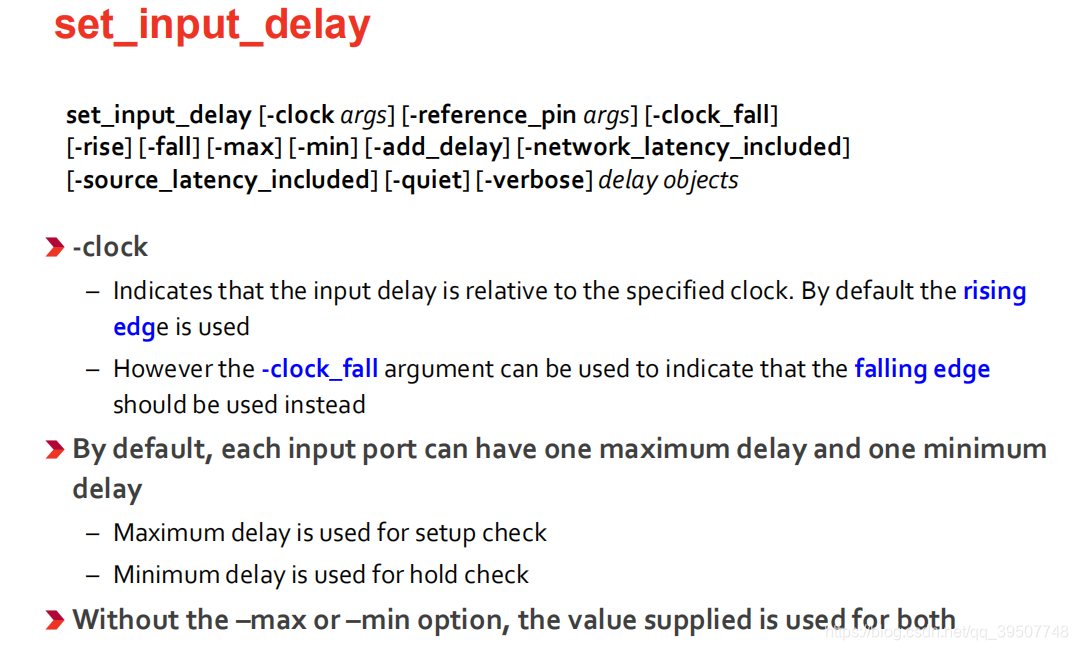

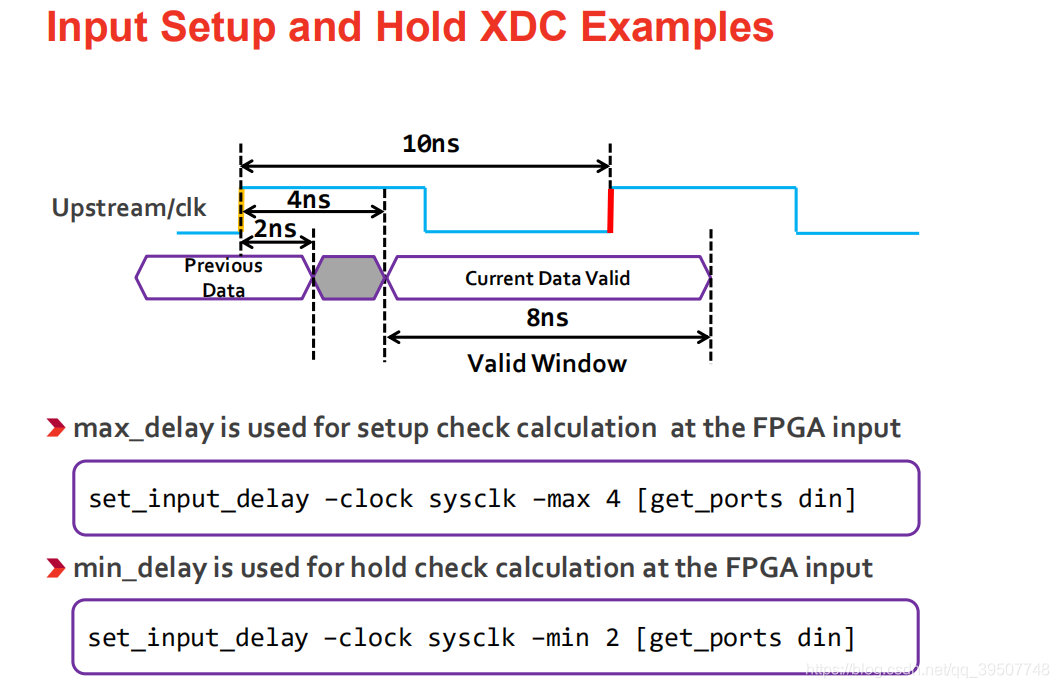

关于时序报告中这几部分的延时为啥要这么算,可以参考这篇文章 传送门 最后的附录部分加以理解。 需要注意的是,如果同时设置了max和min delay,那么max值是用在对Input Setup Timing的分析中的,而min值用在对Input hold Timing的分析中。如果只设置了一个值,那么同时供两者使用!!!

需要注意的是,如果同时设置了max和min delay,那么max值是用在对Input Setup Timing的分析中的,而min值用在对Input hold Timing的分析中。如果只设置了一个值,那么同时供两者使用!!!

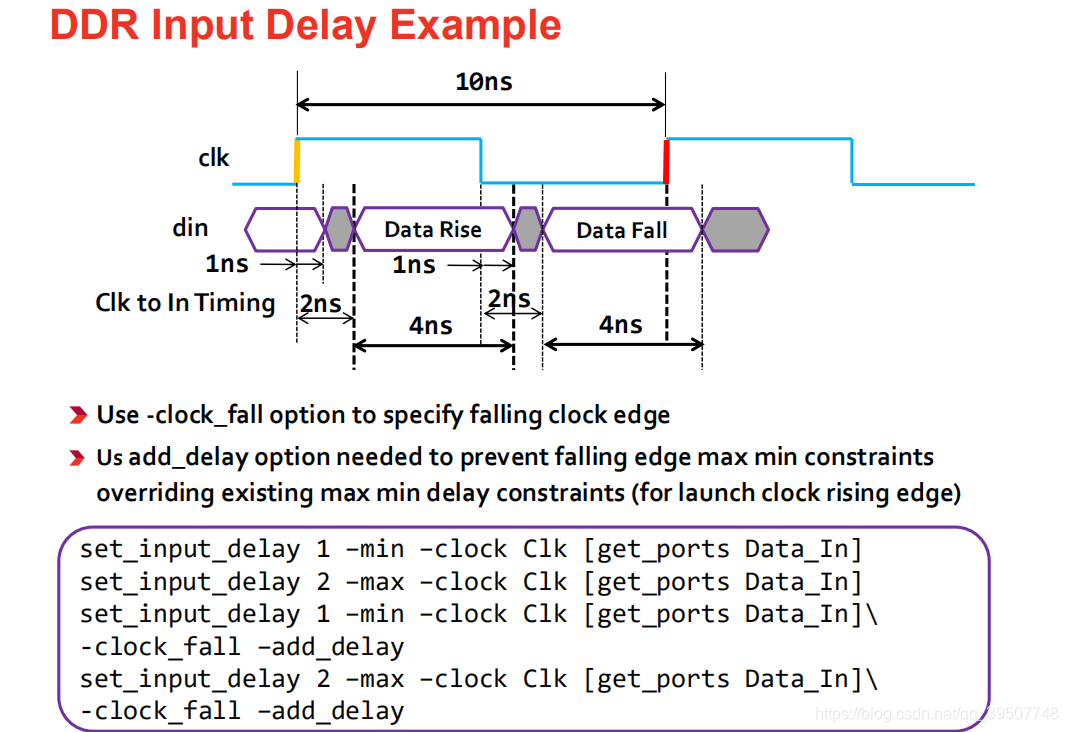

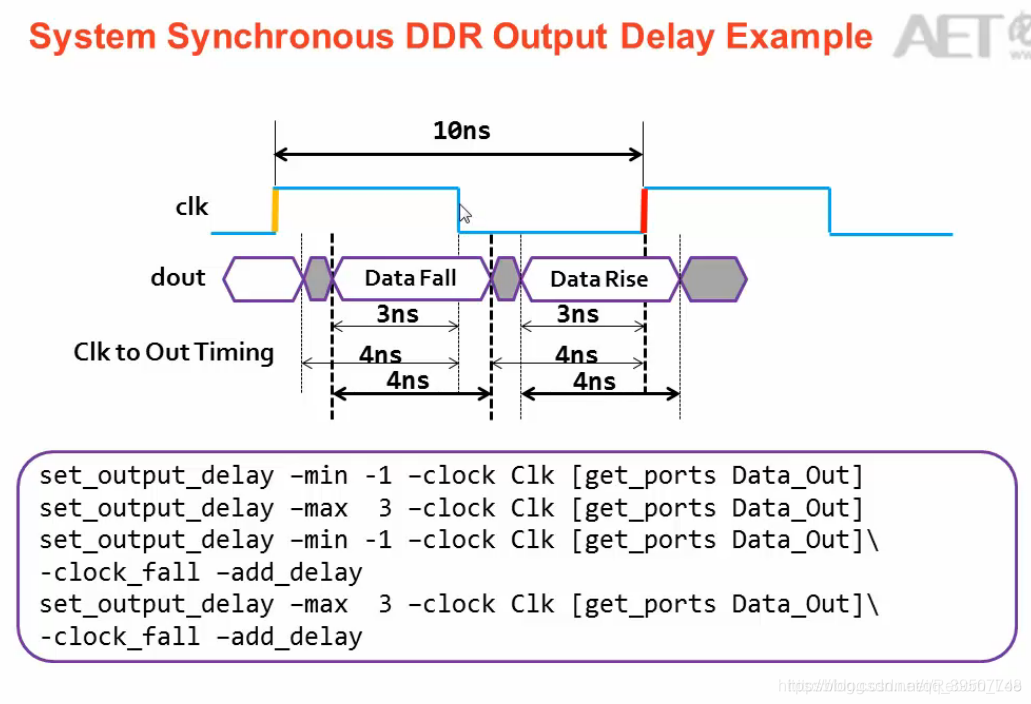

之所以要这么设置,是因为DDR在时钟下降沿采集前一个上升沿发送的数据,在下一个上升沿采集前一个下降沿发送的数据。因为默认设置都是针对上升沿的,因此我们还需要针对下降沿再设置一下参数。

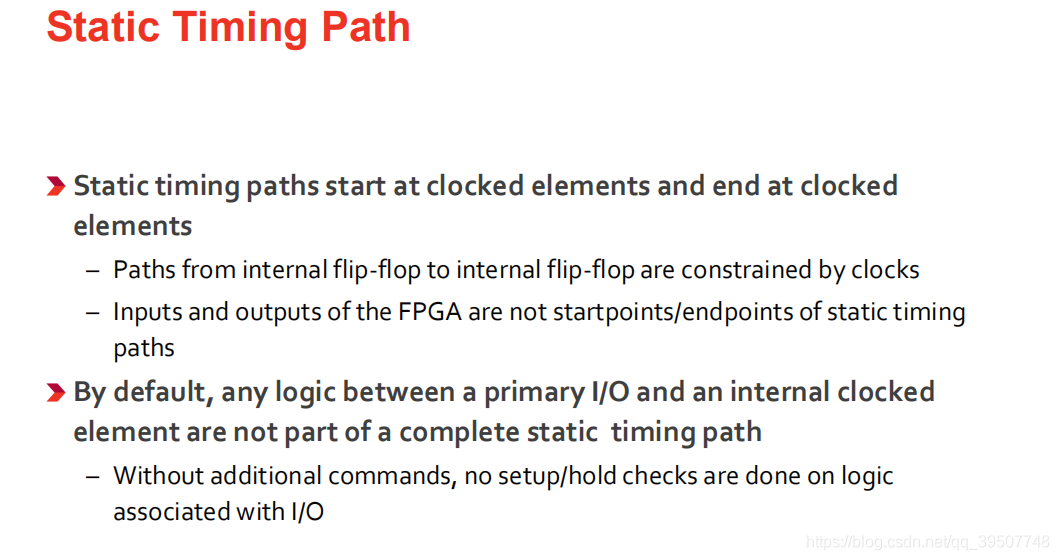

之所以要这么设置,是因为DDR在时钟下降沿采集前一个上升沿发送的数据,在下一个上升沿采集前一个下降沿发送的数据。因为默认设置都是针对上升沿的,因此我们还需要针对下降沿再设置一下参数。 静态时序路径从时钟元件开始,在时钟元件结束

静态时序路径从时钟元件开始,在时钟元件结束 2、输出延时

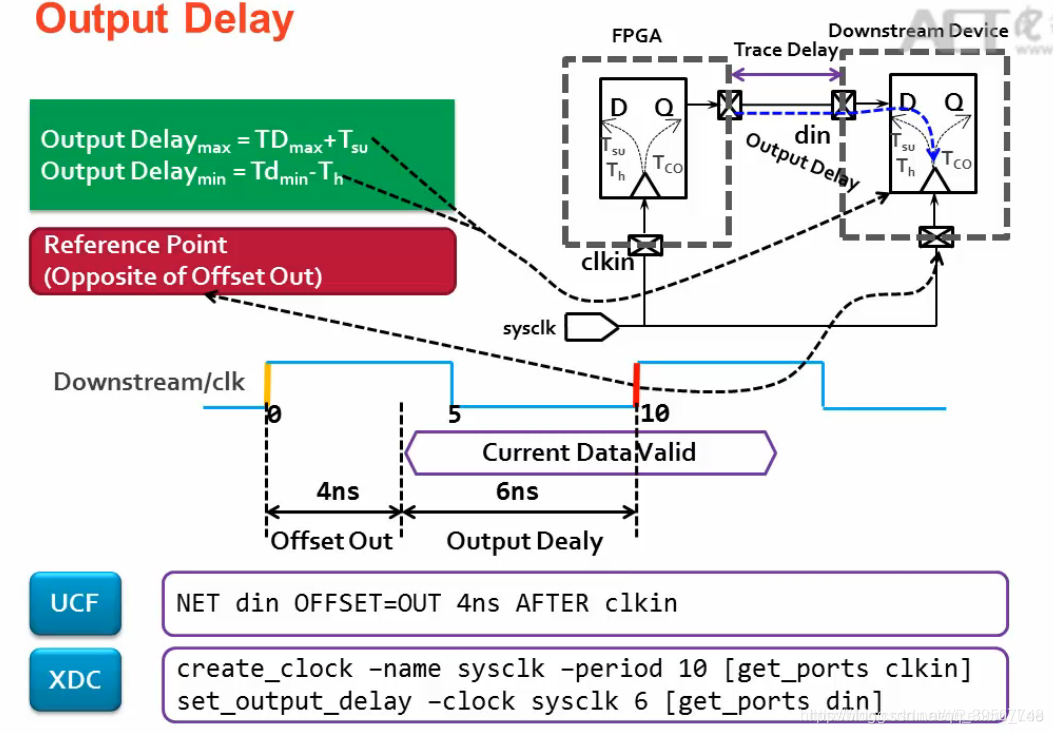

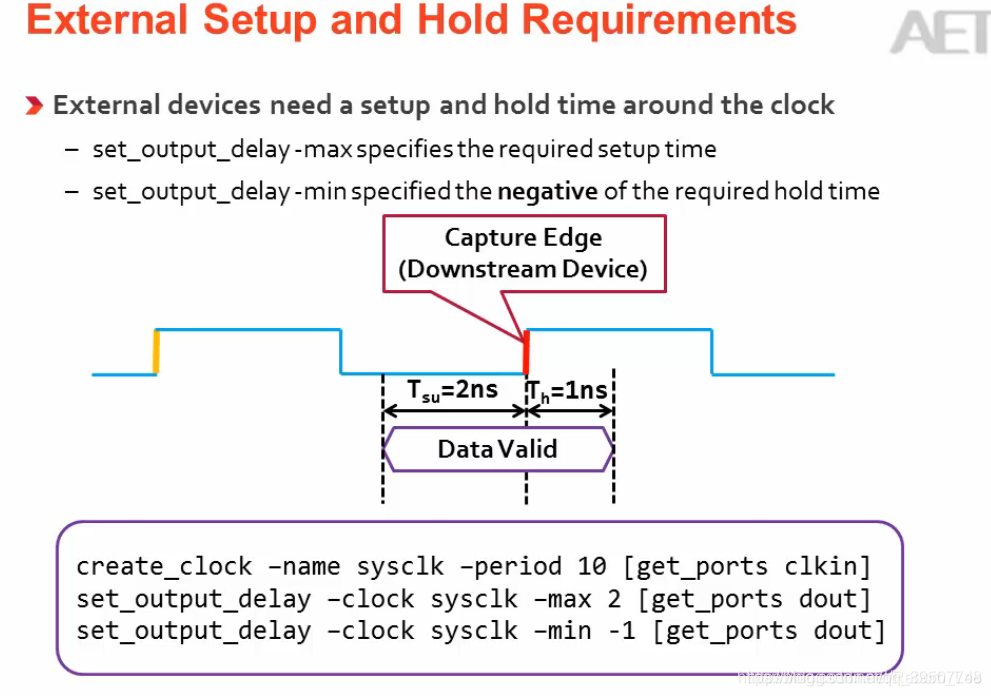

2、输出延时  输出延时指的是从FPGA输出数据后到达外部器件时钟沿的延时时间,其中PCB板上的走线延时以及外部器件的数据建立和保持时间。也可以理解为在捕获沿到来时,数据已经存在的时间,如上图所示!!!

输出延时指的是从FPGA输出数据后到达外部器件时钟沿的延时时间,其中PCB板上的走线延时以及外部器件的数据建立和保持时间。也可以理解为在捕获沿到来时,数据已经存在的时间,如上图所示!!! 因为是以下游芯片的捕获沿为参考点,所以建立时间为正,保持时间为负。

因为是以下游芯片的捕获沿为参考点,所以建立时间为正,保持时间为负。 输出静态时序路径的分段略有不同:

输出静态时序路径的分段略有不同:

关于时序报告中这几部分的延时为啥要这么算,可以参考这篇文章 传送门 最后的附录部分加以理解。

关于时序报告中这几部分的延时为啥要这么算,可以参考这篇文章 传送门 最后的附录部分加以理解。 7、输出延时摘要

7、输出延时摘要

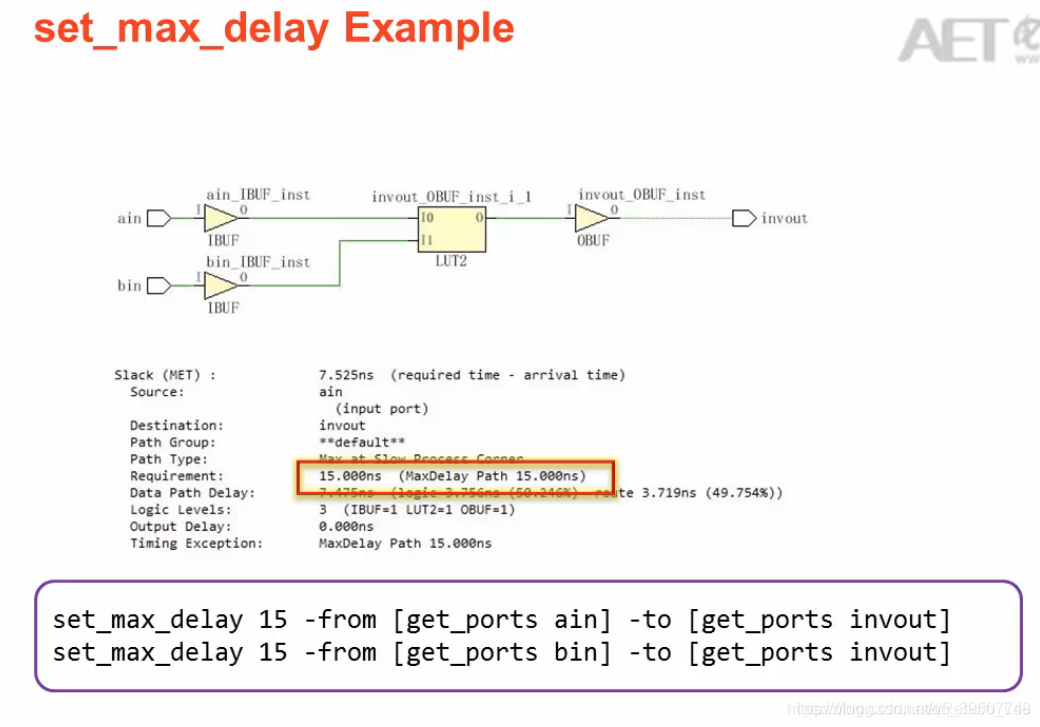

2、设置最大延时举例

2、设置最大延时举例  3、最大延时时序报告

3、最大延时时序报告