| 3.2 静态随机存取存储器 | 您所在的位置:网站首页 › 存储器英语怎么写 › 3.2 静态随机存取存储器 |

3.2 静态随机存取存储器

学习目标:

学习目标:

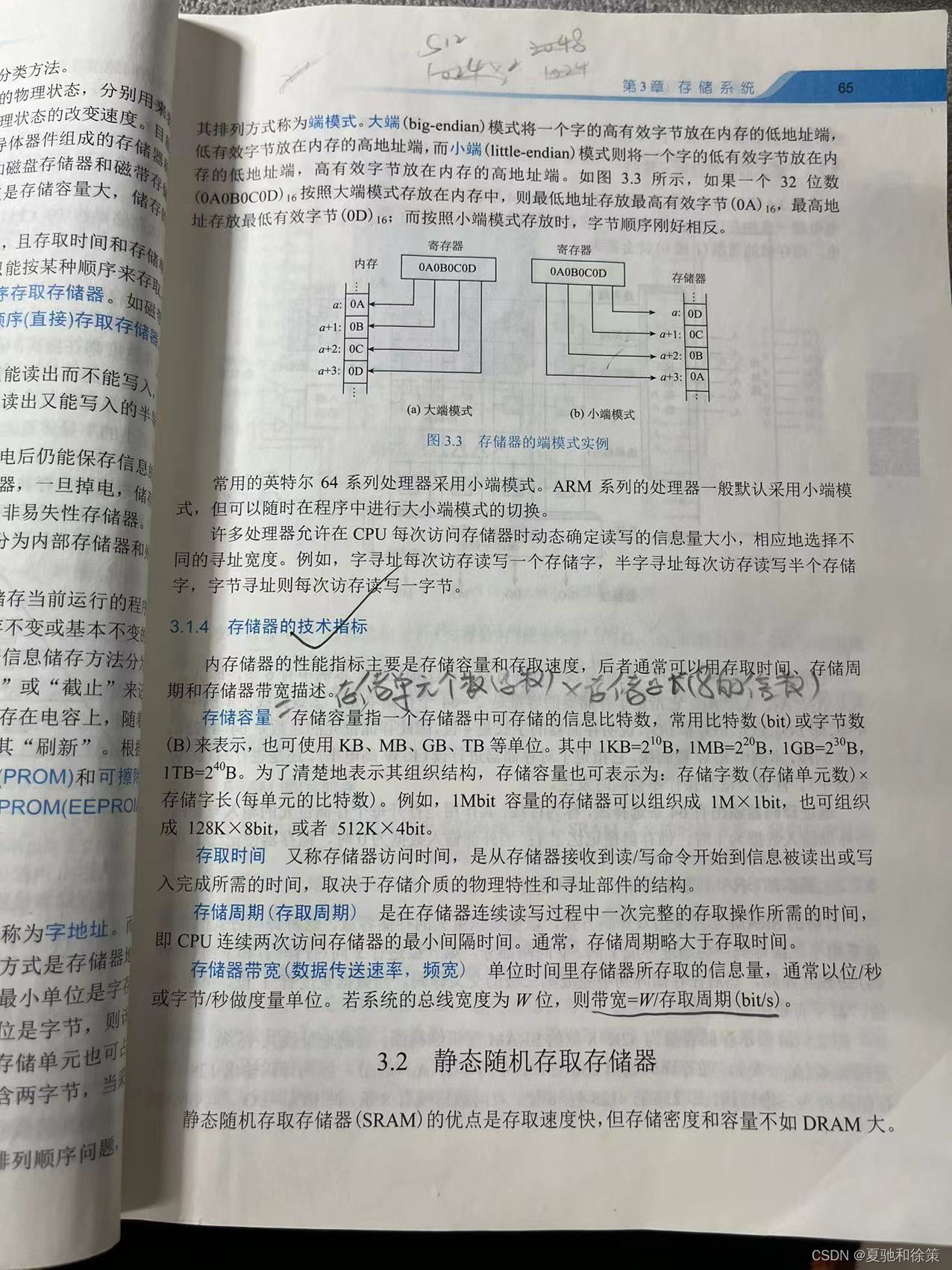

学习静态随机存取存储器(SRAM)的基本原理、结构和工作方式,理解其与动态随机存取存储器(DRAM)的区别和优缺点,掌握SRAM的性能参数和应用领域,了解SRAM的发展历程和未来趋势。同时,学习SRAM的设计方法和优化技术,包括电路设计、布局布线、时序分析、功耗优化等方面,熟悉SRAM的测试方法和可靠性评估方法,能够使用常见的SRAM设计工具和仿真软件进行SRAM的设计和验证。 学习步骤:了解静态随机存取存储器(SRAM)的基本概念、结构和工作原理,以及其与动态随机存取存储器(DRAM)的区别和优缺点。 了解SRAM的存储单元(cell)的基本结构,包括传输门(transfer gate)、存储节点(storage node)、读写线(bit line)、字线(word line)等。 学习SRAM的写入和读取操作,包括写入时的地址选择、数据输入和存储单元状态改变,读取时的地址选择、数据输出和存储单元状态读取。 理解SRAM的时序要求,包括存储单元的写入和读取时间、字线的激活时间、预充电时间等。 了解SRAM的常见应用场景,如高速缓存、寄存器等,并学习如何根据应用场景选择适合的SRAM芯片。 学习SRAM的性能指标,如容量、速度、功耗、可靠性等,以及如何评估和比较不同的SRAM芯片。 实践操作,进行SRAM的设计、仿真、布局和验证,加深对SRAM的理解和应用能力。 阅读相关的学术论文、技术手册、数据手册等,了解SRAM的最新发展和未来趋势,保持对SRAM领域的更新和深入认识。 3.2.0 存储元的读写原理

读操作: 1. 地址传递:计算机通过地址总线将读取请求发送到存储元的地址输入端。地址总线传输的二进制信号指示要读取的存储元的位置。 2. 读使能信号:读使能信号(Read Enable,RE)发出后,存储元接收到读取请求并准备进行读取操作。 3. 数据输出:存储元将所存储的数据通过数据输出线输出到数据总线上。数据总线将数据传递给处理器或其他组件。 4. 数据捕捉:处理器或其他组件通过数据总线捕捉到存储元输出的数据。 写操作: 1. 地址传递:计算机通过地址总线将写入请求发送到存储元的地址输入端。地址总线传输的二进制信号指示要写入的存储元的位置。 2. 数据传递:计算机通过数据总线将待写入的数据传输到存储元的数据输入端。数据总线传输的二进制信号包含要写入的数据。 3. 写使能信号:写使能信号(Write Enable,WE)发出后,存储元接收到写入请求并准备进行写入操作。 4. 数据存储:存储元将接收到的数据存储在其内部电路中,更新存储元的状态以保存写入的数据。 在读写操作过程中,存储元需要根据地址和控制信号的变化来选择相应的操作。读操作涉及将数据从存储元输出,而写操作涉及将数据写入存储元。存储元的内部电路会根据读写使能信号的状态以及输入的地址和数据信号来判断何时进行读取和写入操作。 需要注意的是,存储元的读写原理可以因不同类型的存储器而有所差异,如SRAM(静态随机存储器)和DRAM(动态随机存储器)。每种存储器类型都有自己的特性和实现方式,但基本的读写原理与上述概述类似。 总结来说,存储元的读写原理涉及地址传递、读写使能信号、数据传递和数据存储等关键步骤。通过控制地址和读写使能信号,计算机可以将数据读取到存储元或将数据写入存储元。不同类型的存储器可能会有细微的差异,但核心的读写原理是相似的。 我的理解:当我们谈论存储元时,可以将其比喻为一个书柜或书架。 想象一下你有一个书柜,每个书柜的位置可以存放一本书。每本书都有一个唯一的编号,类似于存储元的地址。 在读操作中,你可以根据书的编号来选择要读取的书,然后从书柜中取出该书,读取其中的内容。这类似于存储元根据地址进行数据的读取。 在写操作中,你可以选择一本新书,并为它分配一个编号。然后,你将这本新书放入书柜的特定位置,使其与编号相对应。这类似于存储元将数据写入特定的地址位置。 书柜中的每本书都可以独立存储和检索,就像存储元可以独立存储和检索数据。 当然,实际的存储元可能包含更复杂的电路和逻辑,但这个比喻可以帮助我们理解存储元的基本概念。存储元是计算机存储器的基本单元,类似于书柜中的一个位置,用于存储和检索数据。根据地址选择数据进行读取和写入,就像根据书的编号选择书进行阅读和存放。 2.六管静态存储元电路

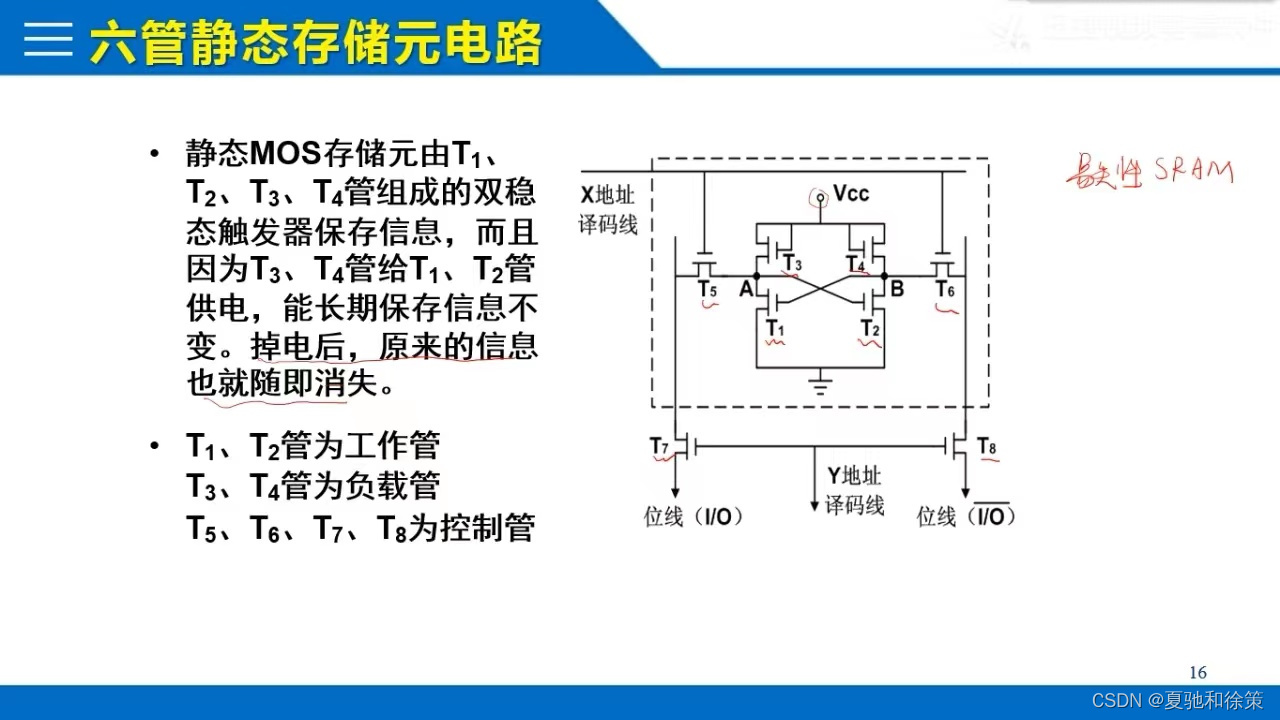

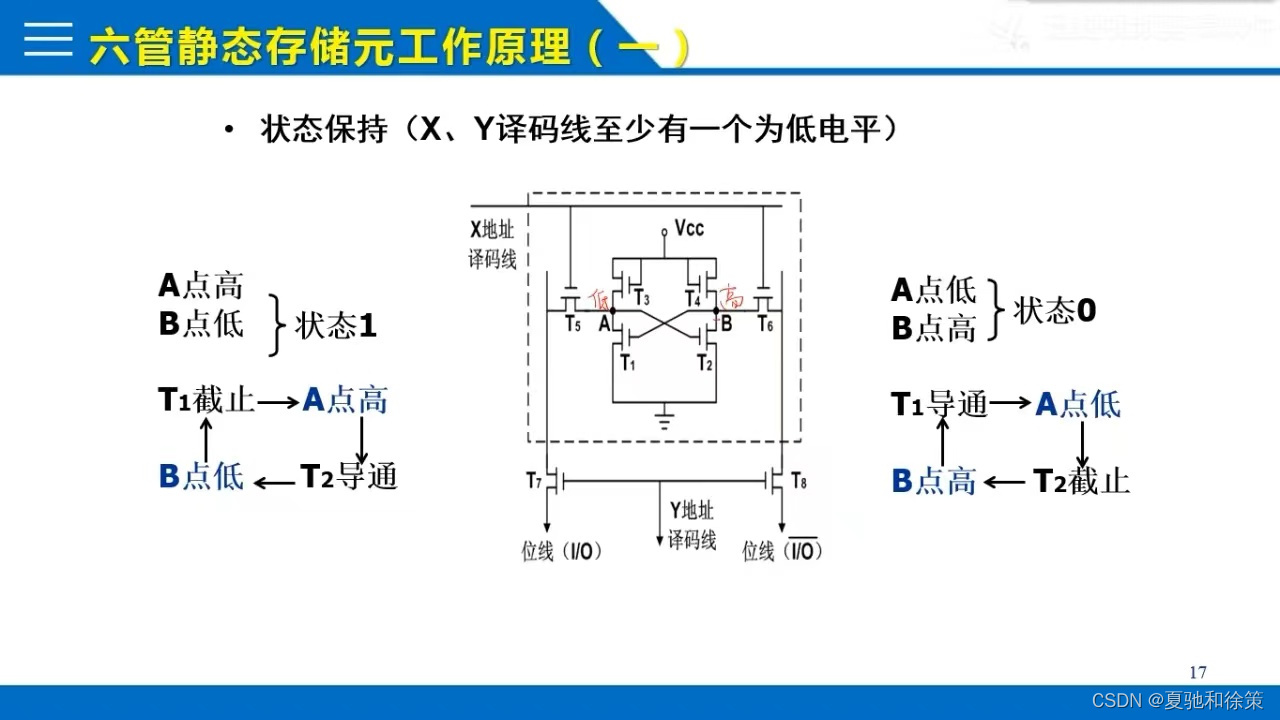

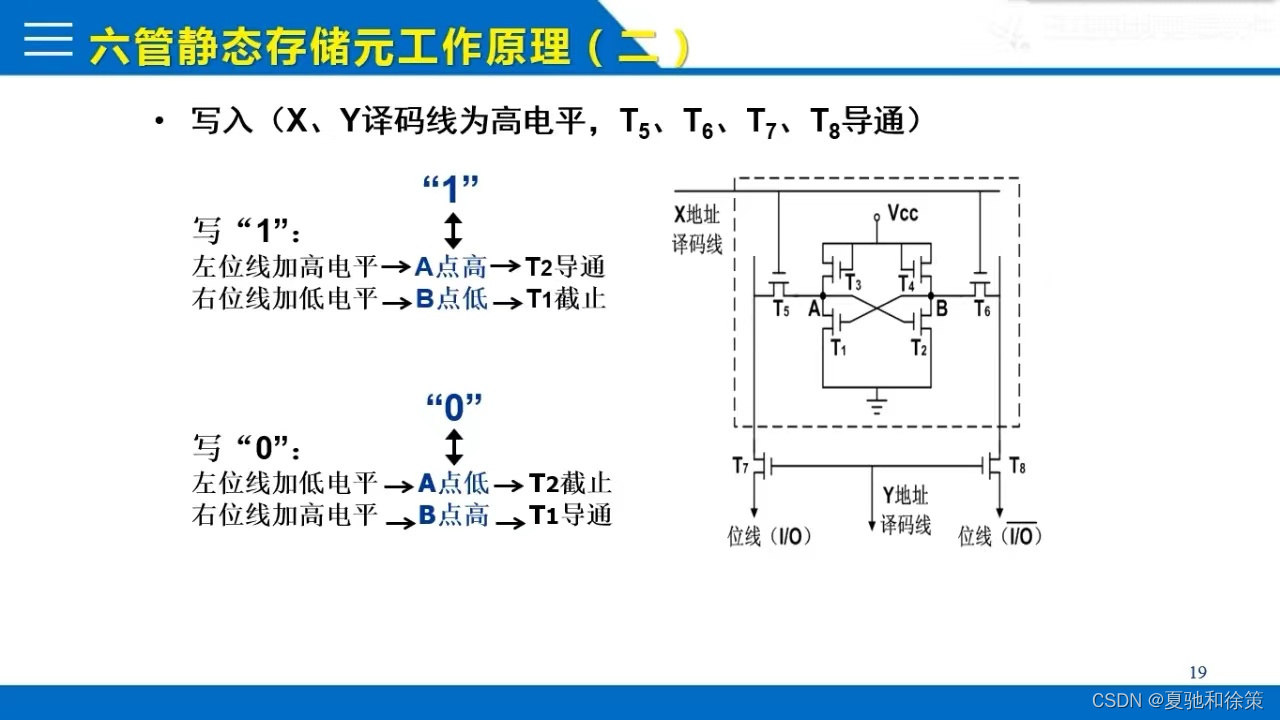

六管静态存储元(6T SRAM)是一种常见的静态随机存储器(SRAM)电路结构,用于存储和检索数据。下面我将简要解释六管静态存储元电路的工作原理。 六管静态存储元由6个晶体管组成,通常包括两个互补的双稳态反相器(Cross-Coupled Inverter)和两个传输门(Transmission Gate)。 基本原理如下: 1. 双稳态反相器:由两个互补的晶体管组成,构成一个反馈环路。当输入电压在某个阈值范围内时,其中一个晶体管导通,而另一个截止,使得输出保持在稳定的逻辑电平上。 2. 传输门:由两个互补的晶体管组成,分别连接到双稳态反相器的输出端和输入端。通过控制传输门的开关状态,可以实现数据的读取和写入。 读操作: 1. 读使能信号(Read Enable,RE)控制传输门的开关状态。当RE为高电平时,传输门打开,允许数据从双稳态反相器的输出端传输到读取线路。 2. 读取线路接收传输门输出的数据,并将其传递给数据总线或处理器。 写操作: 1. 写使能信号(Write Enable,WE)控制传输门的开关状态。当WE为高电平时,传输门打开,允许数据从数据总线输入到双稳态反相器的输入端。 2. 数据总线上的数据通过传输门进入双稳态反相器,并改变反馈环路中晶体管的导通状态,从而更新存储元中的数据。 六管静态存储元的优点是具有快速的读写速度和稳定的存储性能。它在存储器设计中广泛应用,特别是用于高速缓存和寄存器等需要快速访问的场景。 需要注意的是,实际的六管静态存储元电路可能还包含了预充电电路和辅助电路,以确保电路的可靠性和稳定性。此外,六管静态存储元通常以阵列的形式组成SRAM芯片,形成大容量的存储器单元。 总结来说,六管静态存储元是一种常见的静态随机存储器电路,由双稳态反相器和传输门组成。通过控制传输门的开关状态和输入输出信号的传输,可以实现数据的读取和写入操作。它具有快速的读写速度和稳定的存储性能,在计算机存储器中得到广泛应用。 我的理解:

可以通过比喻的方式来理解六管静态存储元电路的概念。 想象一下你有一个小房间,里面有两个门和两个人。这个小房间的状态可以是开门或关门两种,表示存储元的两个稳定状态。 现在,假设其中一个人是门禁,他的状态取决于房间内是否有人。如果房间内有人,他会打开门;如果房间内没有人,他会关闭门。这个人相当于双稳态反相器。 另一个人是传输门,他可以打开或关闭房间的门。当门禁打开门时,传输门可以选择让外面的人进入房间,表示写入数据;当门禁关闭门时,传输门可以选择让房间里的人出去,表示读取数据。传输门控制数据的输入和输出。

通过这个比喻,我们可以理解六管静态存储元的基本工作原理。双稳态反相器作为存储元的状态存储部分,传输门作为数据输入输出的控制部分。通过控制门的开关状态和数据的输入输出,可以实现数据的读取和写入操作。 当然,实际的六管静态存储元电路比这个简化的比喻要复杂得多,涉及更多的电路元件和逻辑。但是,这个比喻可以帮助我们初步理解六管静态存储元的概念和基本工作原理。

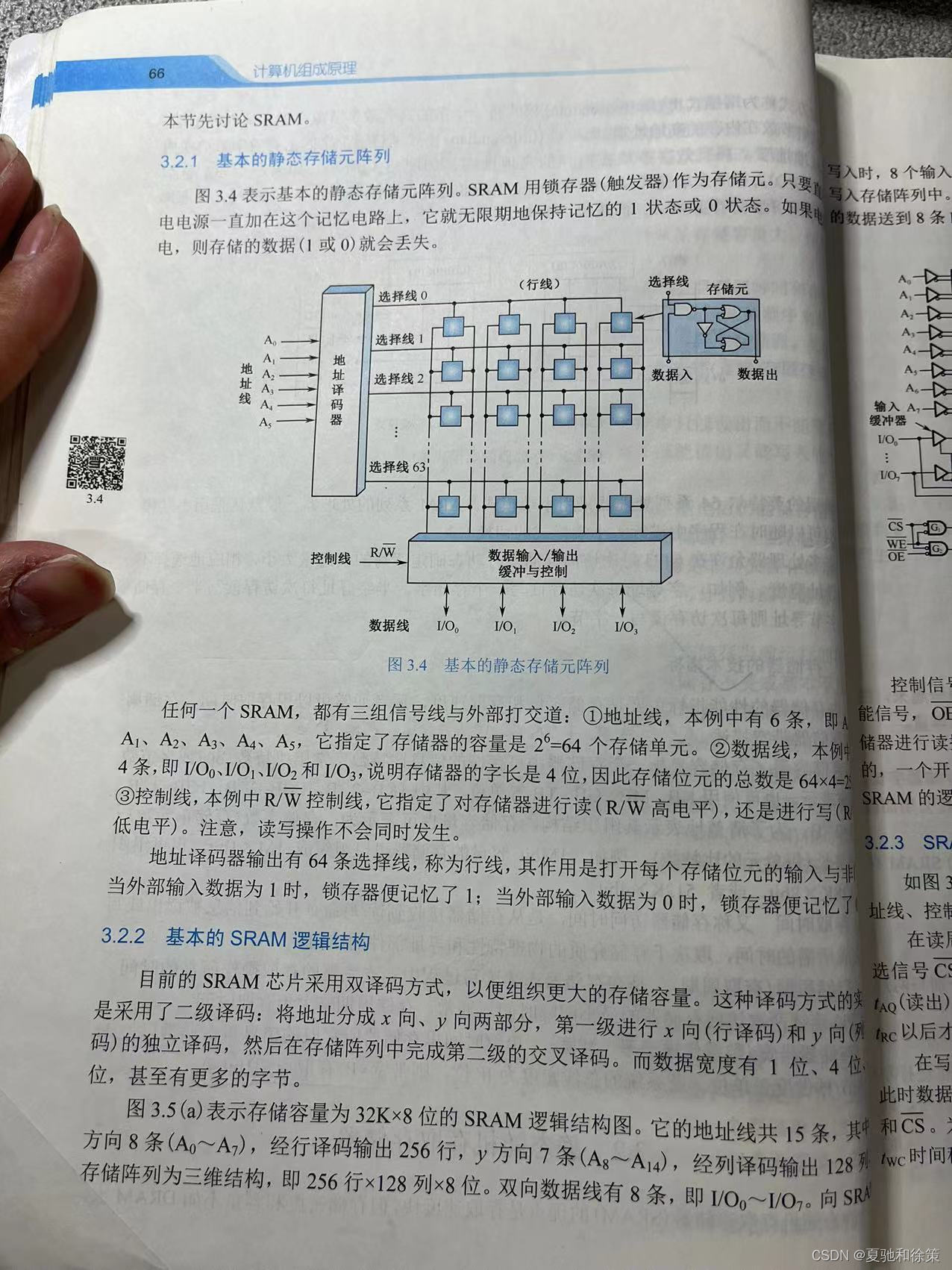

静态存储元阵列是构成静态随机存取存储器(SRAM)的基本单元,它通常由存储单元和访问电路组成。每个存储单元通常由一个存储电容和一个存储晶体管组成,这些存储单元被组织成一行或一列,构成一个存储单元阵列。 静态存储元阵列的访问电路包括读取和写入电路,用于控制存储单元的读取和写入操作。读取电路通常包括一个预读电路和一个比较电路。预读电路将要读取的数据预读到一个数据线上,并将其与存储单元中存储的数据进行比较。比较电路产生一个输出信号,指示读取的数据是否与存储单元中存储的数据相等。写入电路通常包括一个写入控制电路和一个写入数据选择电路,用于将数据写入存储单元中。 静态存储元阵列通常被组织成多个存储块,每个存储块包括多个存储单元阵列和一些控制电路,用于实现存储器的读取、写入和其他操作。存储块之间通常通过一些连接电路进行连接,形成一个完整的存储器。常见的静态随机存取存储器包括SRAM芯片和SRAM模块等。

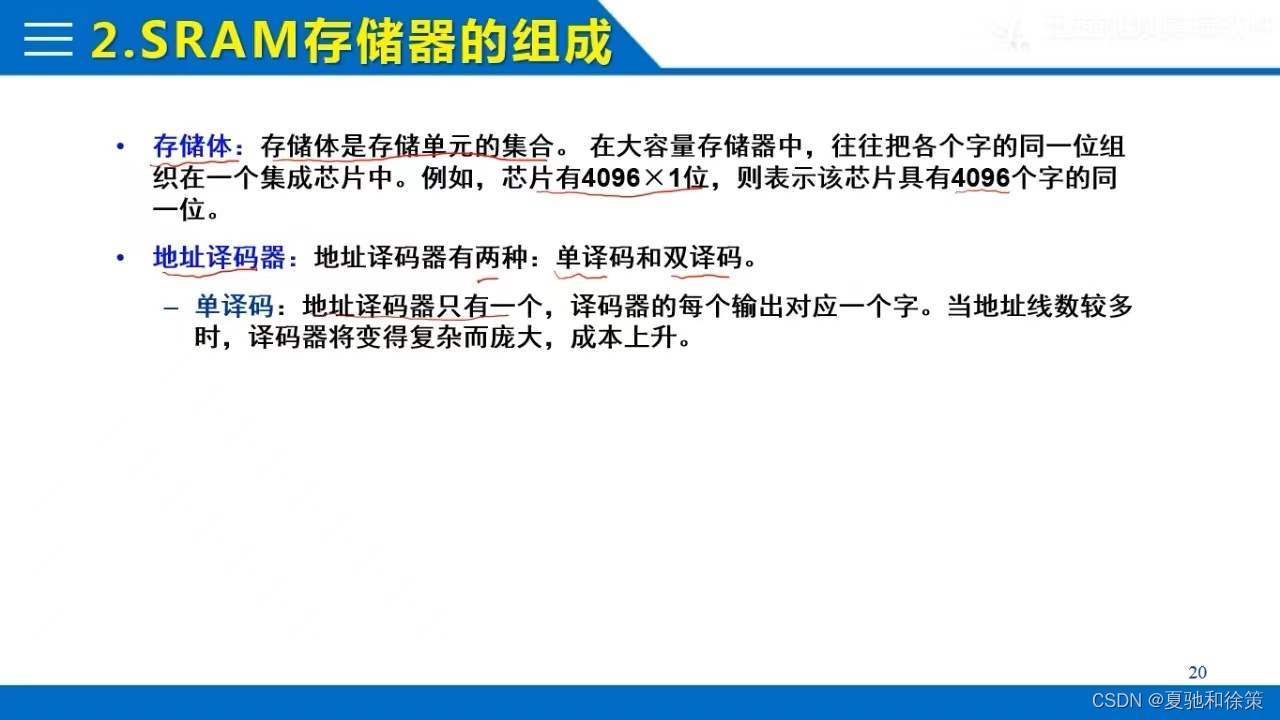

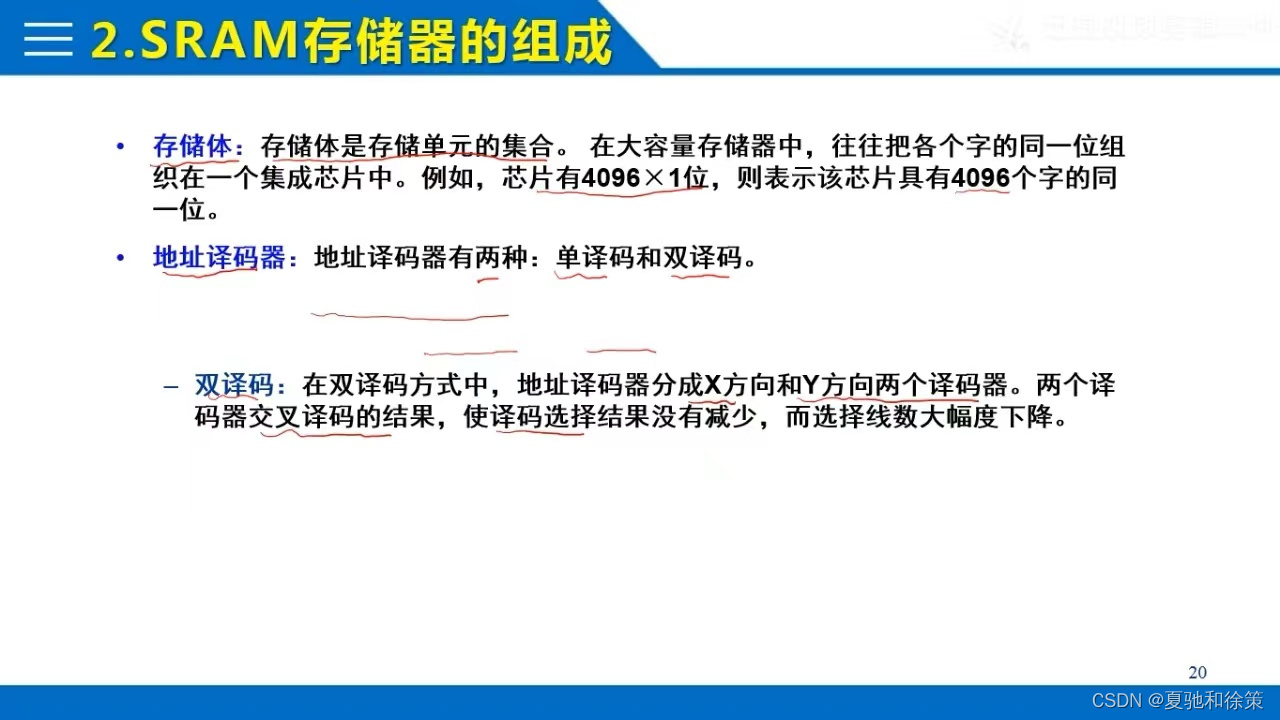

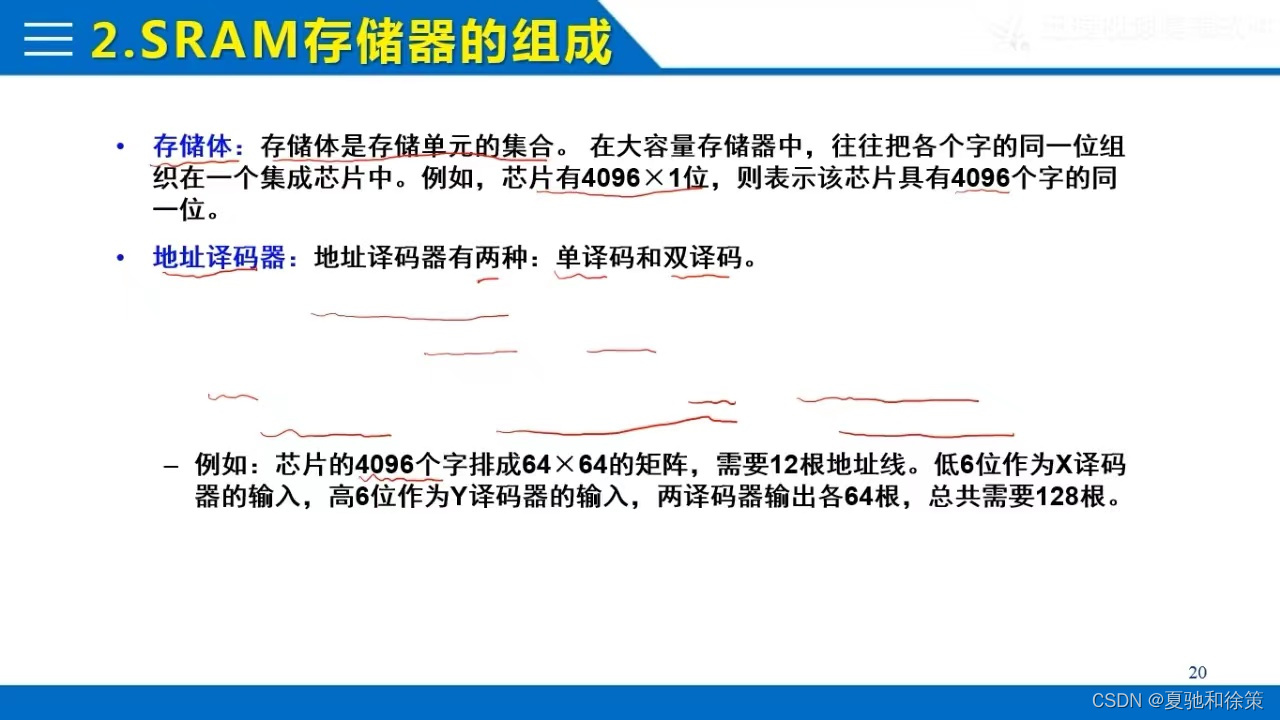

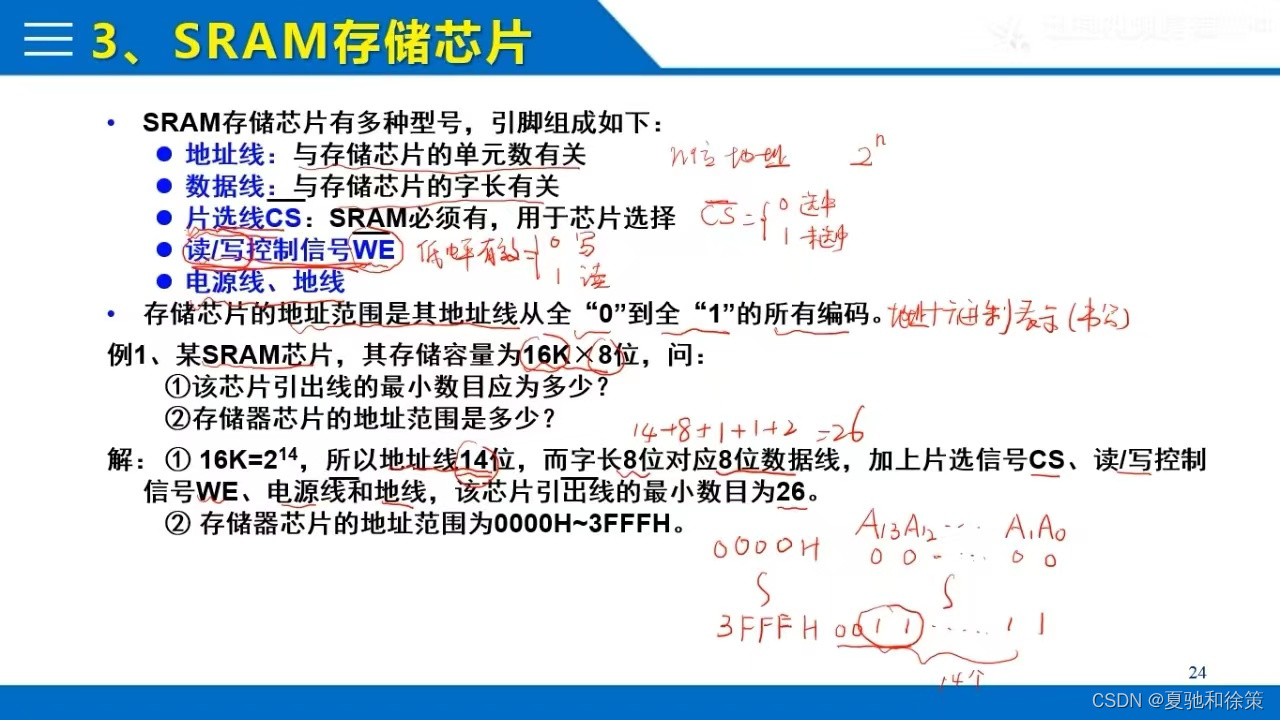

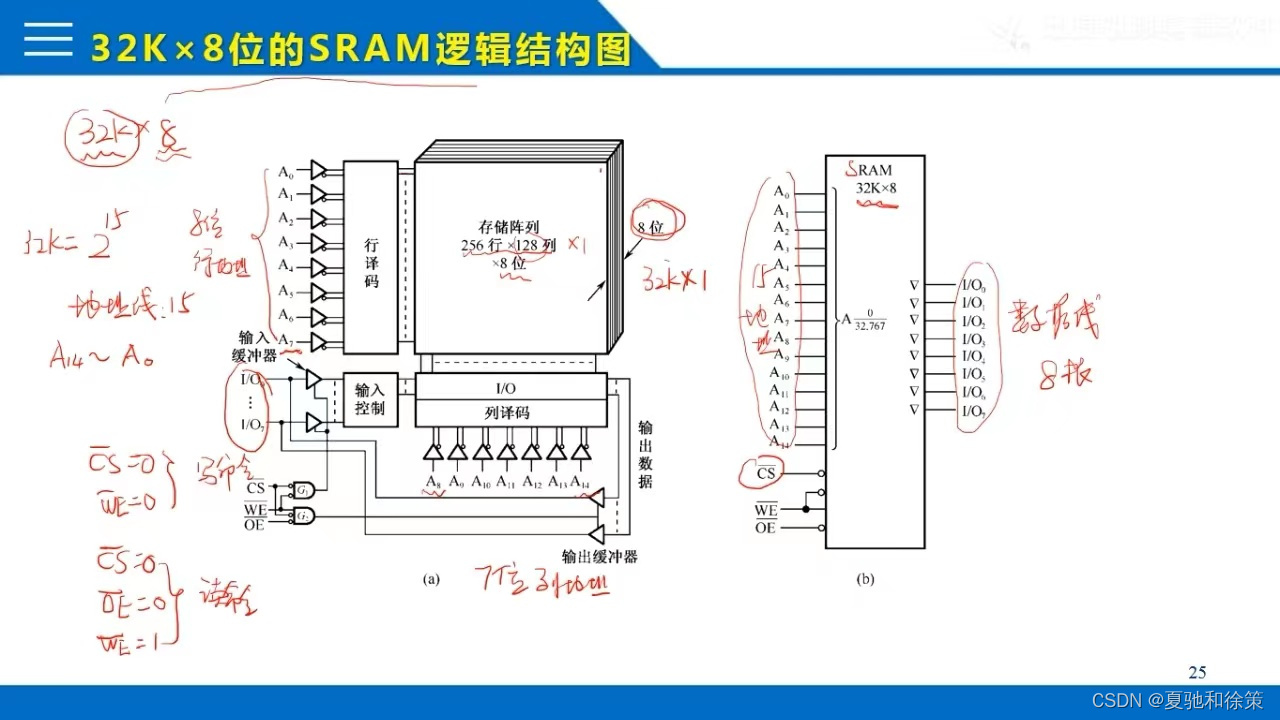

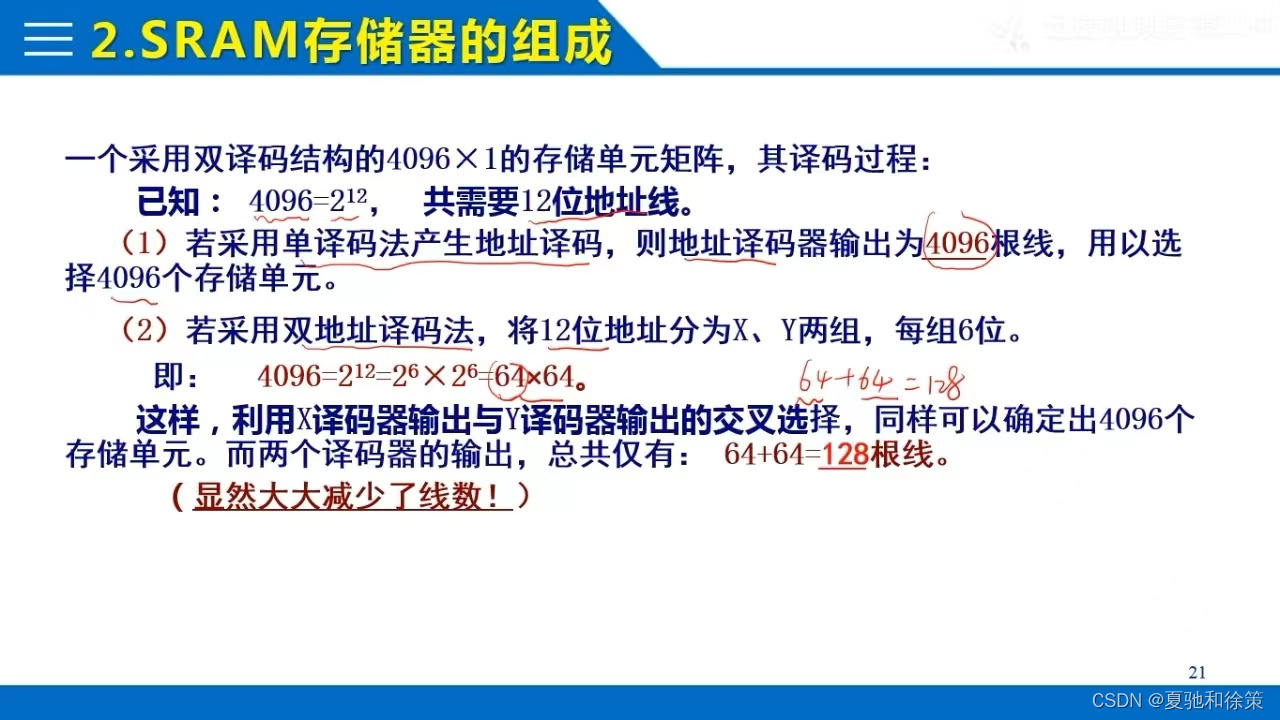

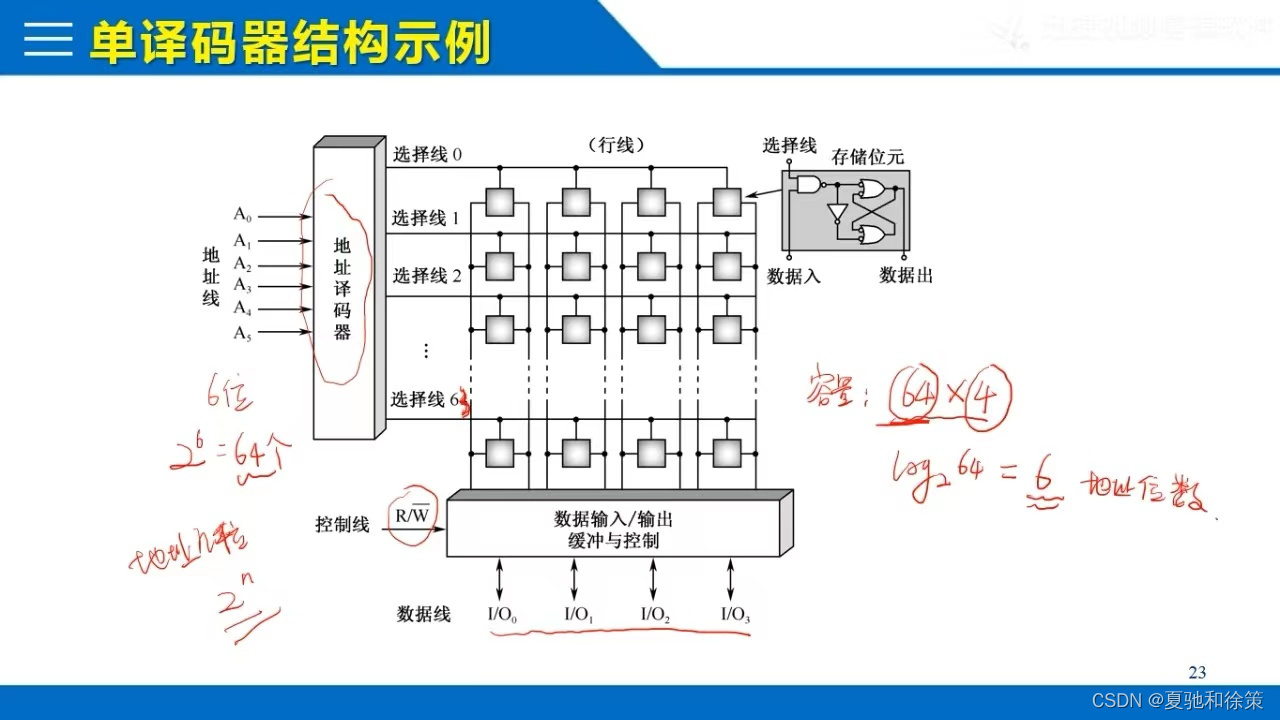

SRAM是一种静态随机存取存储器,由于其高速读写和易于实现的特点,被广泛应用于各种计算机系统中。SRAM存储器通常由多个存储单元组成,每个存储单元可以存储一个二进制位。 SRAM的基本逻辑结构包括两个部分:存储单元阵列和控制电路。存储单元阵列是由多个存储单元组成的矩阵,每个存储单元都有一个地址,可以通过地址线来访问。控制电路主要负责对存储单元阵列进行读写操作,包括地址译码、数据输入输出、读写控制等。

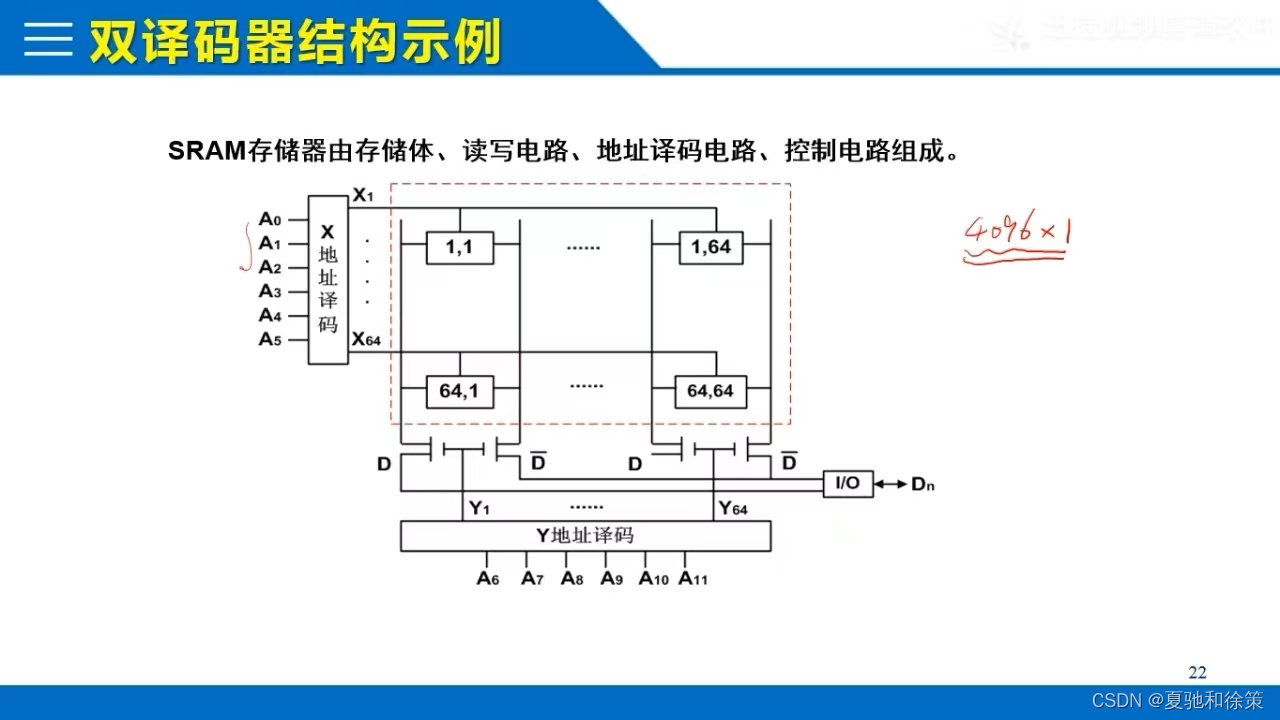

具体来说,一个SRAM存储器通常包括以下几个部分: 存储单元阵列:由多个存储单元组成的矩阵,每个存储单元可以存储一个二进制位。存储单元通常是由一个存储器单元和一个读/写门组成。存储器单元负责存储数据,读/写门负责控制数据的读写。 地址译码电路:用于将CPU发出的逻辑地址转换成SRAM中对应的物理地址。地址译码电路通常由多个逻辑门和寄存器组成,可以实现不同的寻址模式和存储器容量。 数据输入/输出电路:用于将CPU发出的读写数据传输到存储单元阵列中,或将存储单元阵列中的数据传输到CPU。数据输入/输出电路通常由多个三态缓冲器和选择器组成,可以实现高速数据传输和多路选择功能。 读写控制电路:用于控制存储单元阵列的读写操作。读写控制电路通常包括读/写使能信号、时序控制信号、读/写选择信号等,可以实现不同的读写操作和存储器容量。 总之,SRAM的逻辑结构包括存储单元阵列、地址译码电路、数据输入/输出电路和读写控制电路等部分,这些部分协同工作,实现了高速、可靠的数据存储和读写功能。 例子:

双译码器:

双译码器:

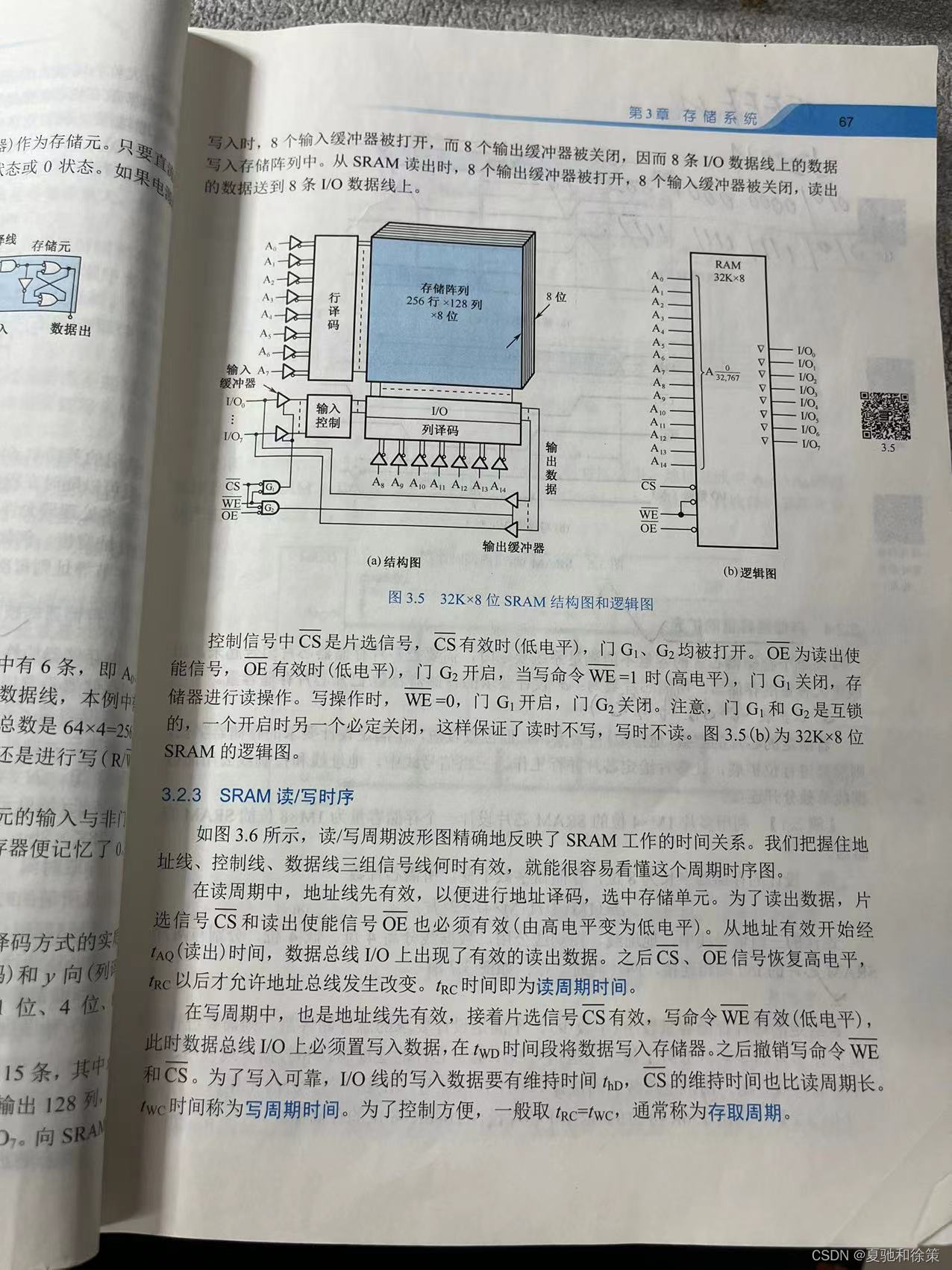

4.芯片实例: 4.芯片实例:

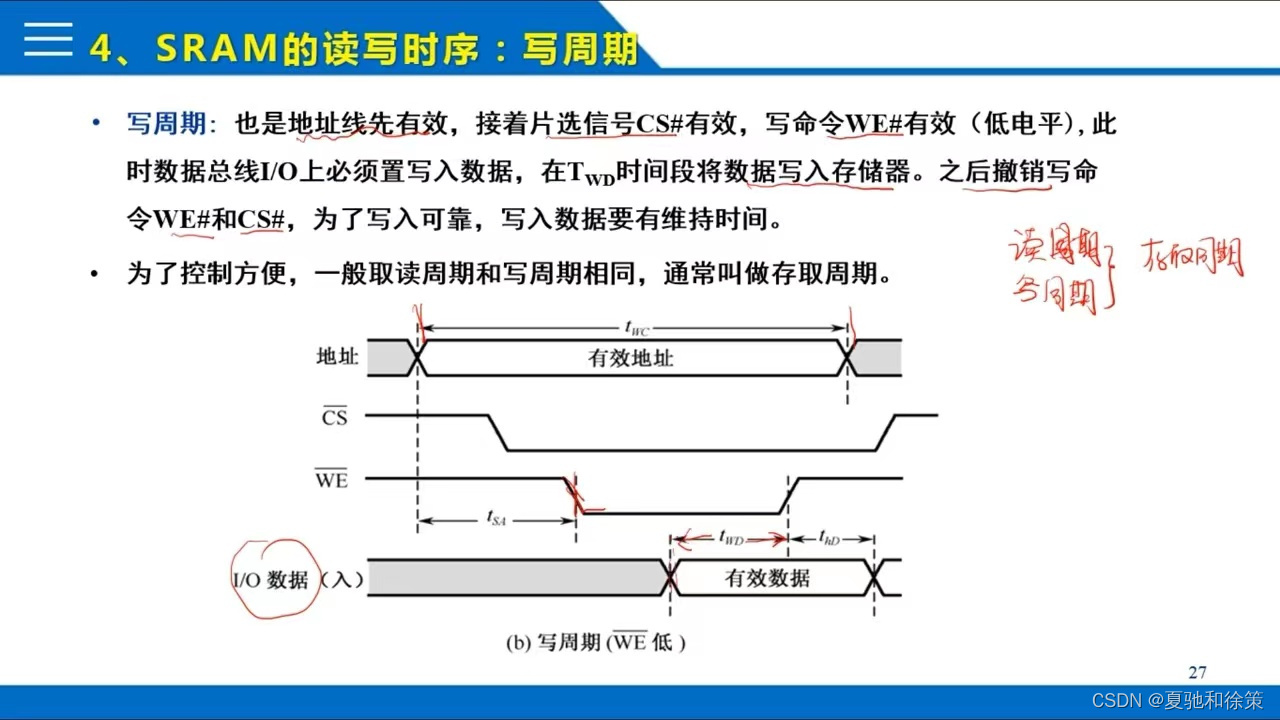

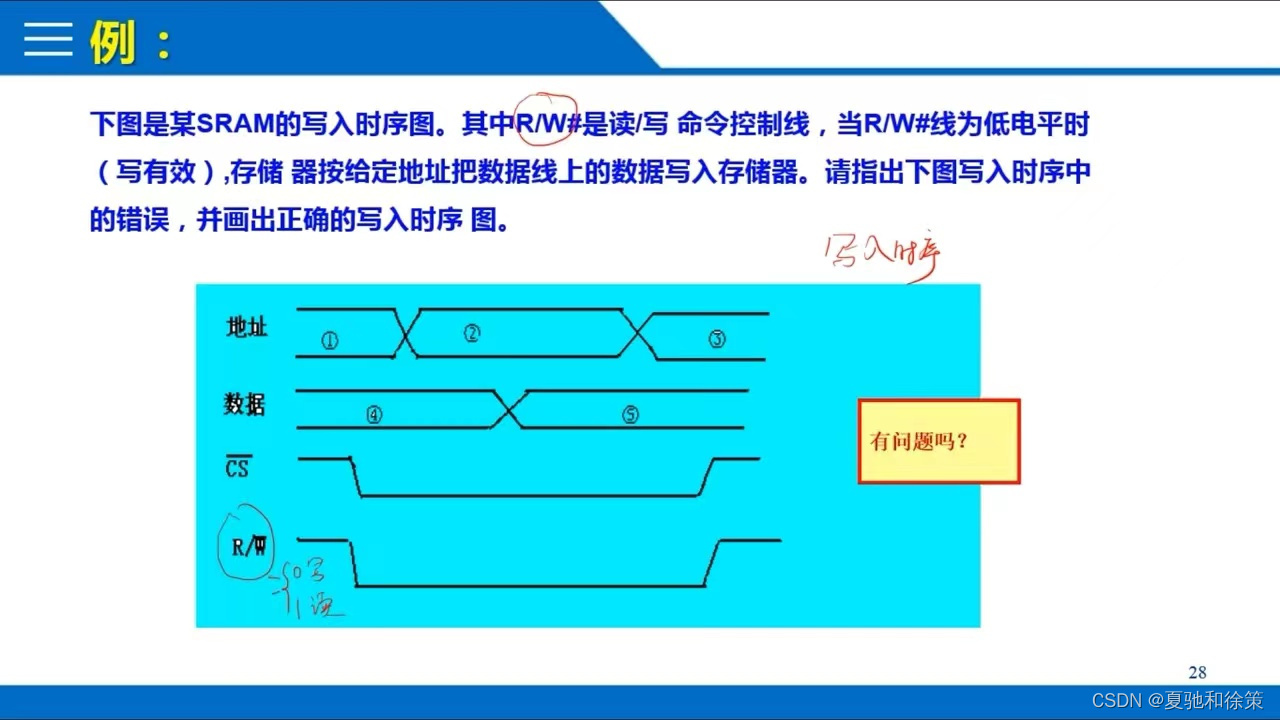

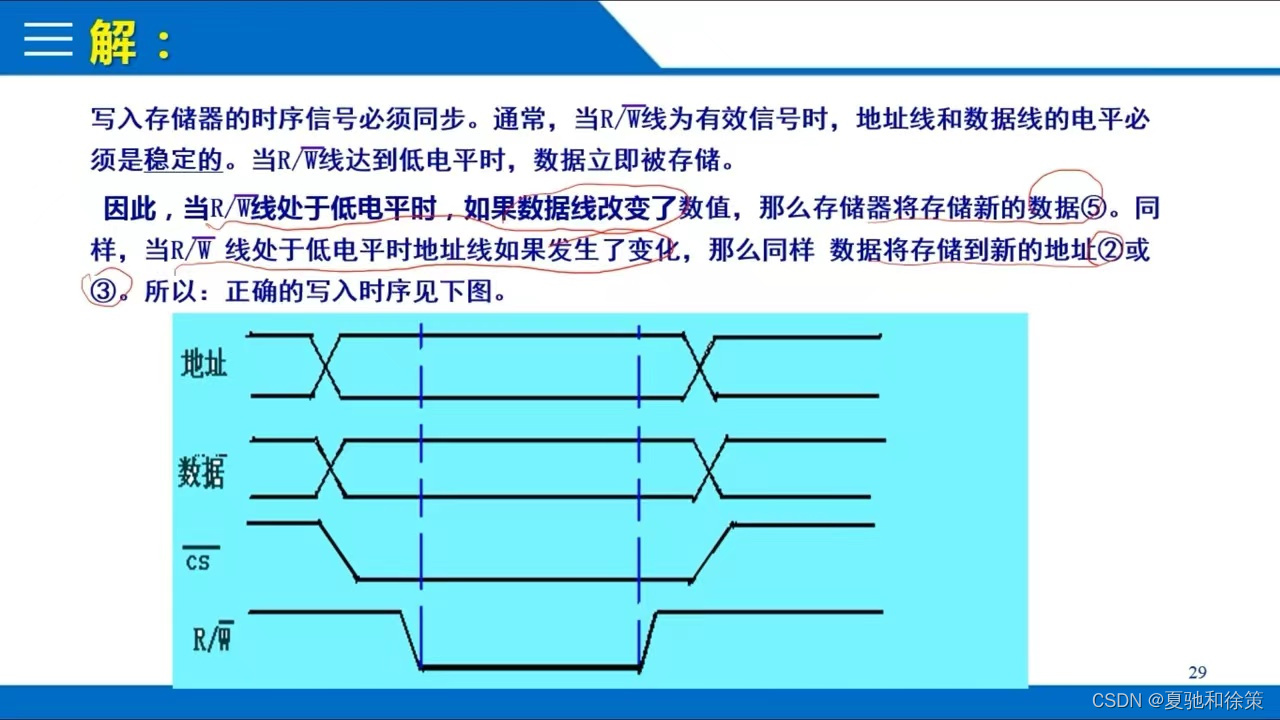

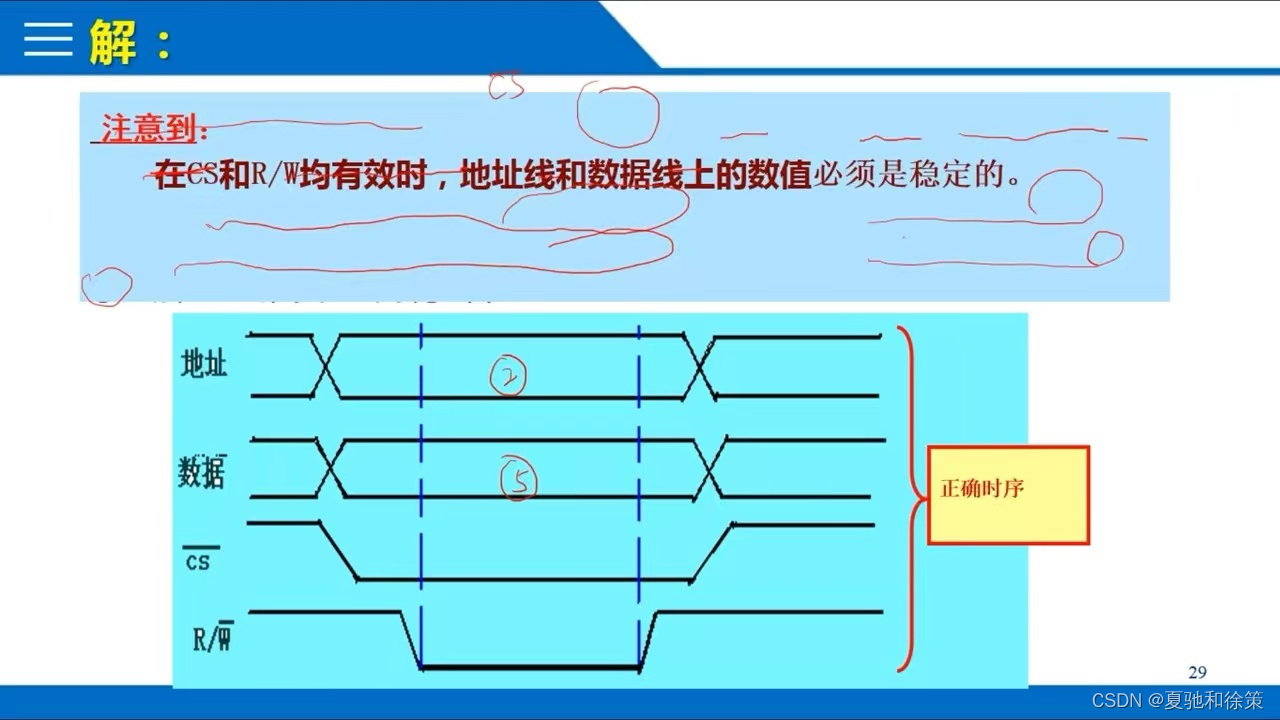

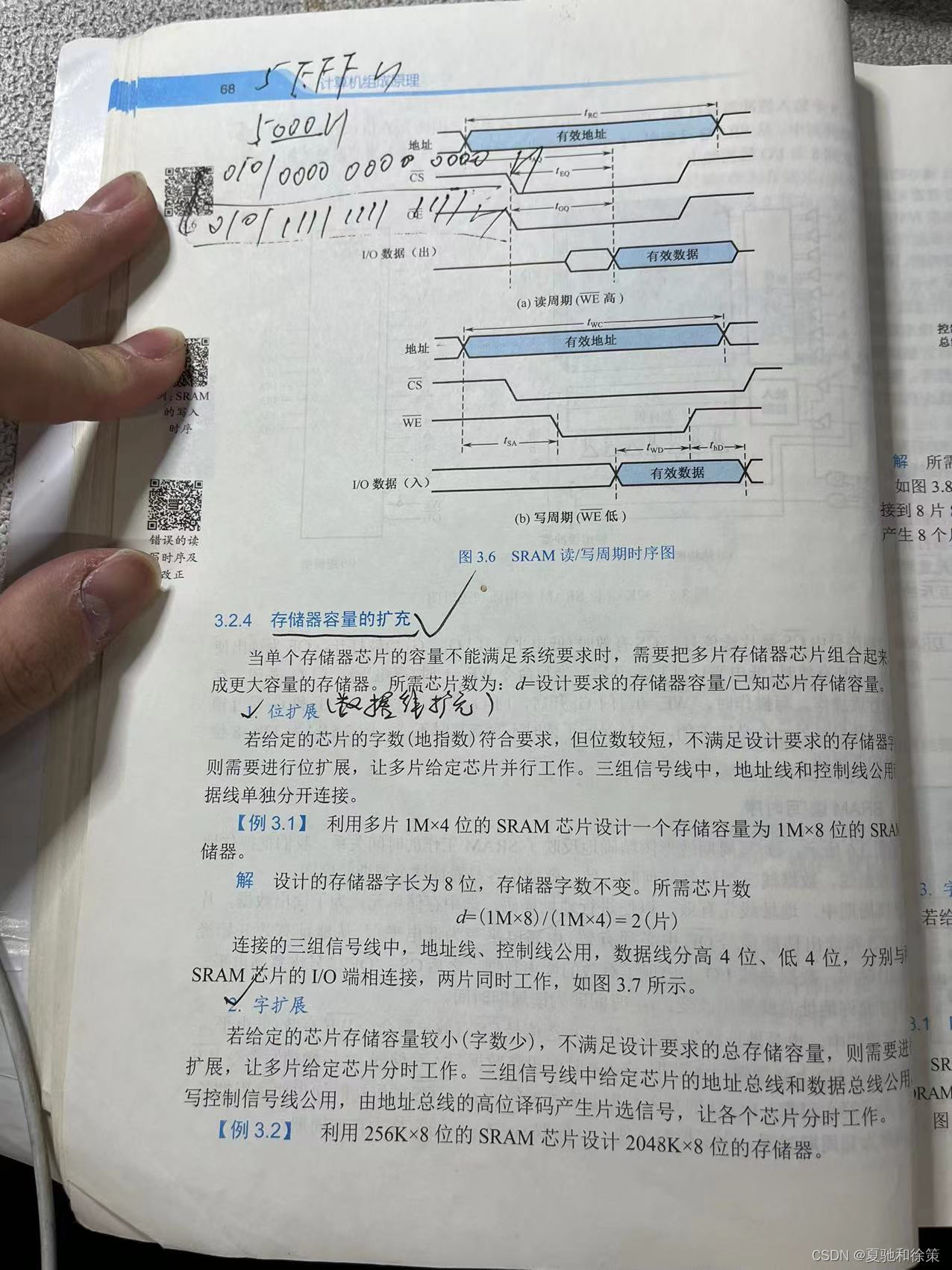

SRAM(静态随机存取存储器)读/写时序是指在进行读/写操作时,各个信号的变化顺序和时间间隔的规定。下面是常见的 SRAM 读/写时序: 读操作: 地址输入:首先CPU将地址信息送到地址总线上,通过地址译码电路选择要读取的SRAM芯片。读信号输入:CPU向SRAM输入读信号(例如 RD# 信号),使 SRAM 进入读状态。存储器响应:SRAM 将存储器中对应地址的数据放置在数据总线上,等待CPU的读取。数据输出:CPU接收到存储器的响应后,从数据总线上读取数据。写操作: 地址输入:首先CPU将地址信息送到地址总线上,通过地址译码电路选择要写入的SRAM芯片。写信号输入:CPU向SRAM输入写信号(例如 WR# 信号),使 SRAM 进入写状态。数据输入:CPU将要写入的数据放置在数据总线上,等待写入。写入确认:SRAM 接收到写信号后,确认可以写入,将数据从数据总线上读取并写入存储器中。需要注意的是,在 SRAM 的读写操作中,由于 SRAM 的响应速度非常快,因此信号的时序和时间间隔非常重要,一旦出现不符合要求的情况,就可能导致读写操作失败或者产生错误。

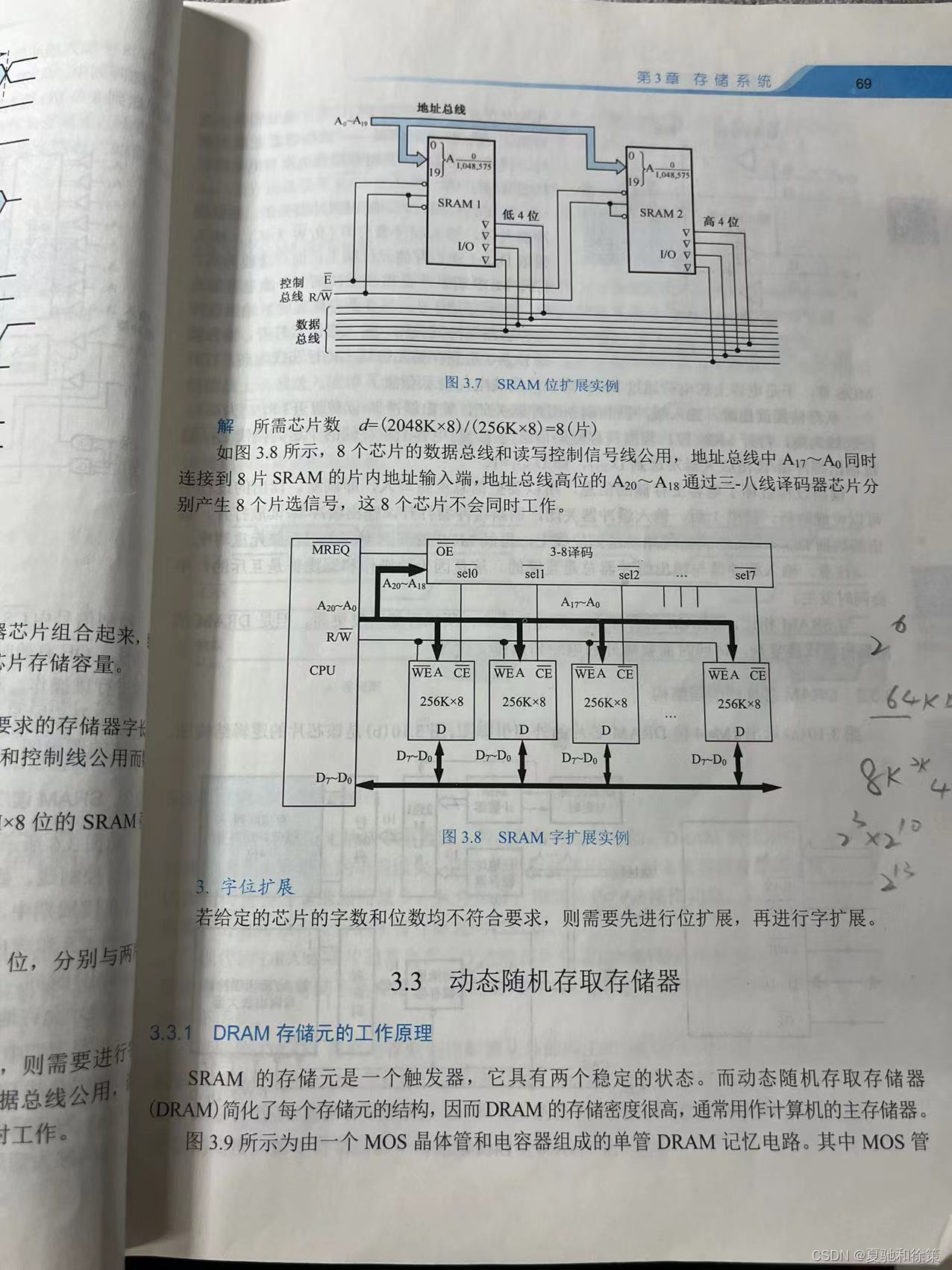

存储器容量的扩充是指通过一定的方法增加存储器的容量,以满足更大存储需求的过程。在计算机系统中,存储器的容量往往是一个重要的性能指标,因此存储器容量的扩充也是一项非常重要的技术。 存储器容量的扩充主要有以下几种方法: 单体存储芯片容量扩充:单体存储芯片容量扩充是指通过改进存储芯片的工艺技术,增加单个存储芯片的容量。这种方法可以在不改变系统设计的情况下,增加存储器的容量。 存储芯片数量扩充:存储芯片数量扩充是指通过增加存储芯片的数量,以增加存储器的容量。这种方法需要对系统进行重新设计,增加存储芯片的数量可能会引起数据线的延长、芯片选择信号的复杂等问题。 存储器芯片组扩充:存储器芯片组扩充是指在原有的存储器基础上增加新的存储器芯片组。这种方法需要重新设计系统,并增加一些控制电路,以确保新的存储器芯片组能够正常工作。 存储器级联扩充:存储器级联扩充是指通过将多个存储器级联起来,以增加存储器的容量。这种方法可以在不改变系统设计的情况下,增加存储器的容量。但是级联会增加存储器的访问延迟和功耗。 以上几种方法可以单独使用,也可以结合使用,具体的扩充方法需要根据具体的应用情况来确定。 静态随机存取存储器(SRAM)是计算机存储器中的一种,具有快速读/写速度和易于实现的优点。以下是SRAM的重点、难点和易错点总结: 重点: SRAM的逻辑结构和基本存储元阵列。SRAM的读/写时序,包括地址信号和控制信号的设置和时序关系。SRAM的容量扩充方法和技术,包括级联和交织等方式。难点: SRAM的读/写时序比较复杂,需要理解控制信号的作用和时序关系,同时需要考虑时序误差对读/写操作的影响。SRAM的容量扩充需要考虑多个存储器的地址映射和数据传输,容易出现地址冲突和数据丢失等问题。易错点: 地址信号的设置错误,容易导致读/写错误。控制信号的设置不当,容易导致时序错误和读/写错误。容量扩充时没有考虑地址映射和数据传输的问题,容易导致地址冲突和数据丢失等问题。为了避免以上问题,学习SRAM时应该注重理解逻辑结构、时序和容量扩充方法,多做实验并注意调试过程中的细节问题。

|

【本文地址】