| 80x86/Pentium微机原理及接口技术 | 您所在的位置:网站首页 › 奔腾微处理器 › 80x86/Pentium微机原理及接口技术 |

80x86/Pentium微机原理及接口技术

|

80x86/ Pentium微机原理及接口技术 1. 计算机基础... 1 1.1常用术语... 1 1.2计算机中数与编码的表示方法... 1 1.2.1进制表示及进制转换... 1 1.2.2有符号数表示... 1 1.2.3编码表示... 2 2. 80x86及Pentium微处理器... 2 2.1 8086/8088微处理器的内部结构与工作原理... 2 2.1.1执行单元EU.. 3 2.1.2总线接口单元BIU.. 4 2.2 8086/8088的内部寄存器... 5 2.3工作模式与引脚... 5 2.4存储器组织... 7 2.4.1实模式下存储器组织... 7 2.4.2存储器分段管理... 8 2.4.3奇偶存储器结构... 9 2.5堆栈组织... 10 2.6时序... 11

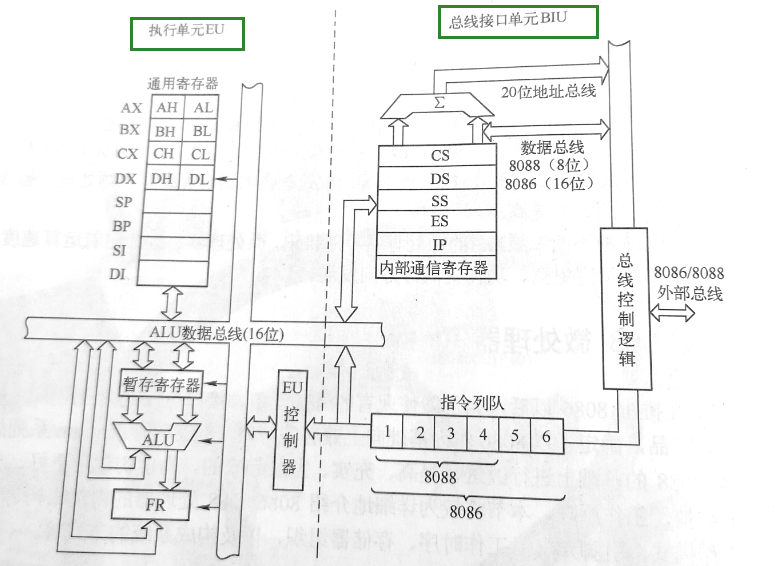

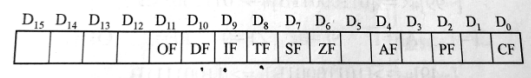

80x86/ Pentium微机原理及接口技术 1. 计算机基础 1.1常用术语 (1) 位(bit):每一位只有两种状态0或1。计算机能表示的最小数据单位。 (2) 字节(Byte):8位二进制数为一个字节。计算机基本存储单元内容用字节表示。 (3) 字(Word):PC常将2个字节定义为一个字,一个字为16位二进制数。微处理器内部数据传输、处理基本单位。 (4) 指令:由0和1组成的代码。让微处理器进行某种操作的命令。 (5) 指令系统:一台计算机能识别的全部指令。 (6) 程序:为了使计算机完成某种工作而编制的一系列指令。 (7) 存储器:存储数据和程序。可以把存储器看成很多存储单元,每个存储单元存8位二进制编码(1字节)。存储单元编号称为存储地址。 (8) 存储容量单位:1B=8bit;1KB=1024B=1024×8bit;1MB=1024KB; 1.2计算机中数与编码的表示方法 1.2.1进制表示及进制转换(1) 10进制数:123.45D=1×102+2×101+3×100+4×10-1+5×10-2 (2) 2进制数:1010.101B=1×23+0×22+1×21+0×20+1×2-1+0×2-2+1×2-3=10.875D (3) 16进制数:A2.F3H=10×161+2×160+15×16-1+3×16-2=163.03125D (4) 10进制转2进制:整数部分除2取余,直到商为0。余数从下往上写。小数部分乘2取整,直到满足精度要求。整数从上往下写。 (5) 2进制转16进制:从右到左每4位转换成对应的16进制数。10-15用A-F表示。 1.2.2有符号数表示问题:计算机是如何处理有符号数的? 将符号数值化,2进制数最高位定义为符号位,0表示+,1表示-。 (1) 真值:现实中的数字(2进制)必须有+/-。 (2) 原码:最高位为符号位(0表示+,1表示-),其余位均为数值位的二进制数。 (3) 反码:正数反码和原码相同,负数反码=原码符号位不变,其他各位取反。 (4) 补码:正数补码和原码相同,负数补码=原码中符号位不变,其他各位取反后+1。 (5) 运算规则:[X]原=[[X]补]补;[X]原=[[X]反]反;[X±Y]补=[X]补±[Y]补=[X]补+[±Y]补 1.2.3编码表示(1) 非压缩型BCD码:1个字节表示1位10进制数,高4位清0。00000001 00000001表示11 (2) 压缩性BCD码:1个字节表示2位10进制数。00010001表示11 (3) ASCII码:用7位2进制数对字符进行编码,共有27=128个字符。 2. 80x86及Pentium微处理器 2.1 8086/8088微处理器的内部结构与工作原理 图2-1 8086/8088CPU内部结构图 8086/8088微处理器内部分为执行单元EU和总线接口单元BIU两部分。 执行单元负责完成指令的执行工作,总线接口单元负责完成预取指令和数据传输工作。可以实现流水作业,在执行指令的同时取下一条指令。 2.1.1执行单元EUEU包括:1个运算器,8个16位通用寄存器(4个数据寄存器,4个指针寄存器),1个16位标志寄存器FR,16位内部数据总线等。 (1) 运算器:完成8位或16位运算工作。 (2) 16位内部数据总线:用于微处理器内部各部分间数据传送,位数决定了微处理器的位数。 (3) 4个数据寄存器:AX、BX、CX、DX,存放参与运算的数据或运算结果。每一个数据寄存器都是16位,可以将高低8位作为2个独立的8位寄存器使用。高8位分别为AH、BH、CH、DH,低8位分别为AL、BL、CL、DL。 AX:累加器。 BX:基址寄存器。 CX:计数寄存器。 DX:数据寄存器。 (4) 4个指针寄存器: SP:堆栈指针寄存器。 BP:基址指针寄存器。 SI:源变址寄存器。 DI:目标变址寄存器。 (5) 标志寄存器FR(状态控制寄存器): 反应运算结果的状态或控制某种状态。

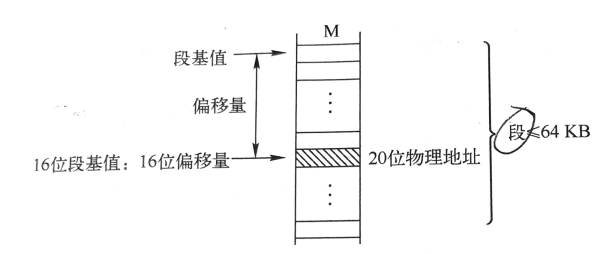

图2-2标志寄存器FR 16位FR中有9位有效位; 6位为状态位: CF:进位状态位 AF:辅助进位状态位 SF:符号状态位 PF:奇偶状态位 ZF:零状态位 OF:溢出状态位 3位为控制位: IF:中断允许标志 DF:方向标志 TF:陷阱标志,用于单步操作 2.1.2总线接口单元BIUBIU包括:1个20位地址加法器,4个16位段寄存器,1个16位指令指针寄存器IP,1个4/6字节指令队列和总线控制逻辑等。 (1) 4个段寄存器:存放当前段的16位段基值。微处理器要访问某个单元,必须将该单元所在段的段基值存到段寄存器里,使其成为当前段。 CS:代码段寄存器,常用于存程序代码段的段基址,只能读出,不能通过指令赋值。 SS:堆栈段寄存器 DS:数据段寄存器 ES:附加数据段寄存器 (2) 指令指针寄存器IP:存放指令的偏移地址。 专为微处理器使用,不能通过指令进行访问。 当微处理器从代码段CS和指令指针寄存器IP所决定的内存单元中取出一个字节或一个字指令代码后,IP自动加1或加2,指向下字节或字的指令代码。 (3) 指令队列:与CPU速度匹配的高速缓存器,用以支持流水线工作。 (4) 20位地址加法器:通过20位地址加法器可自动完成由16位描述的逻辑地址转换成20位的物理地址。 逻辑地址:8086/8088微处理器采用存储器分段描述方法,将整个存储区划分成很多段,每个存储单元均处于某个段中,每个单元可以用两个参数描述:段基址、偏移量,指令中书写格式为段基址:偏移量,称为逻辑地址。 物理地址:16位段寄存器里面的段基值左移4位(乘以16),再与16位偏移量相加,形成20位物理地址。 8086/8088微处理器有20根外部地址线,但内部总线、内部寄存器只有16位,通过20位地址加法器,将逻辑地址变成物理地址,从而描述存储器单元的20位地址。 2.2 8086/8088的内部寄存器一共有14个16位寄存器: 4个段寄存器:存放当前段的16位段基值。微处理器要访问某个单元,必须将该单元所在段的段基值存到段寄存器里,使其成为当前段。 4个数据寄存器:AX、BX、CX、DX,存放参与运算的数据或运算结果。每一个数据寄存器都是16位,可以将高低8位作为2个独立的8位寄存器使用。 4个指针寄存器:SP:堆栈指针寄存器。BP:基址指针寄存器。SI:源变址寄存器。DI:目标变址寄存器。 1个指令指针寄存器IP:存放指令的偏移地址。 1个标志寄存器FR(状态控制寄存器):反应运算结果的状态或控制某种状态。 2.3工作模式与引脚

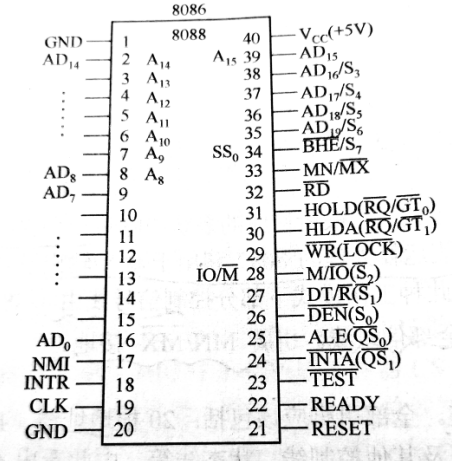

图2-3 8086/8088引脚分配 引脚分配图说明:内部标注的引脚是8088与8086定义不同的引脚。括号内为最大工作模式下的引脚定义。 8086和8088CPU主要特点:

8088 8086 相同点 内部数据总线为16位,寄存器和指令系统完全兼容

不同点

外部数据总线为8位 外部数据总线为16位 指令队列缓存器为4字节 指令队列缓存器为6字节 无控制线 有控制线 存储器和IO选择控制线为/M 存储器和IO选择控制线为M/

(1) 最小工作模式:构成单位处理器的简单系统,全部信号线均由8086/8088CPU提供,引脚MN/接+5V。 (2) 最大工作模式:构成多处理器的复杂系统。系统中除有一个主微处理器8086/8088外,还有两个协处理器:8087(用于数值运算处理),8089(用于输入输出设备服务),部分控制信号线是由8288总线控制器提供的,引脚MN/接地。 (3) 8086/8088为40引脚双列直插式DIP芯片。部分引脚采用复用技术,包括分时复用(某一时刻提供一种信息,另一些时刻提供另外一些信息),分状态复用(输入输出定义不同、高电平低电平定义不同、不同模式下定义不同)等。 主要引脚: AD0~AD15:地址/数据分时复用线 A16/S3~A19/S6:地址/状态分时复用线 MN/ ALE:地址锁存允许信号,三态输出线。

RESET:复位信号,输入线,高电平有效。使处理器马上结束当前操作,对处理器内部寄存器进行初始化。复位后除了内部寄存器CS=FFFFH,其他寄存器及指令队列均被清零。

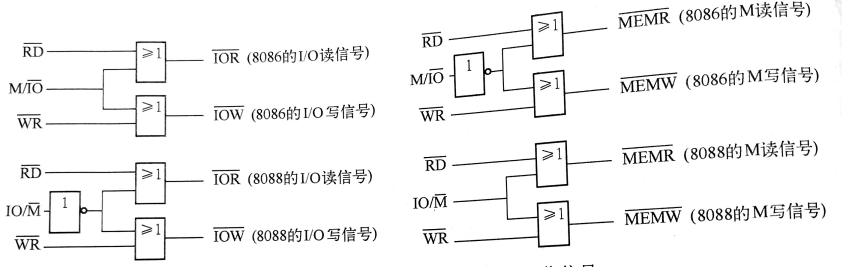

M/

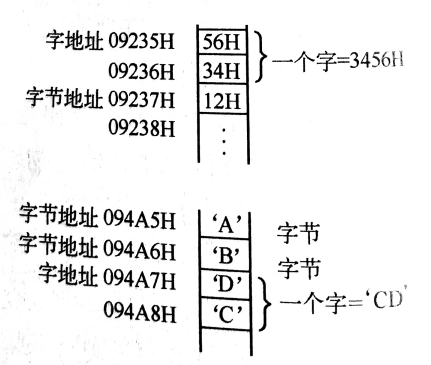

图2-4 8086/8088对存储器或I/O操作信号 2.4存储器组织 2.4.1实模式下存储器组织(1) 所有数据以字节形式存放在存储单元中,每一个单元均占一个地址,任何两个相邻字节构成一个字,占两个地址。80x86用地址值较小的那个字节单元地址作为这个字单元地址。 (2) 一个16位字中低8位数据存在较小地址单元中,高8位数据存在地址较高单元中。

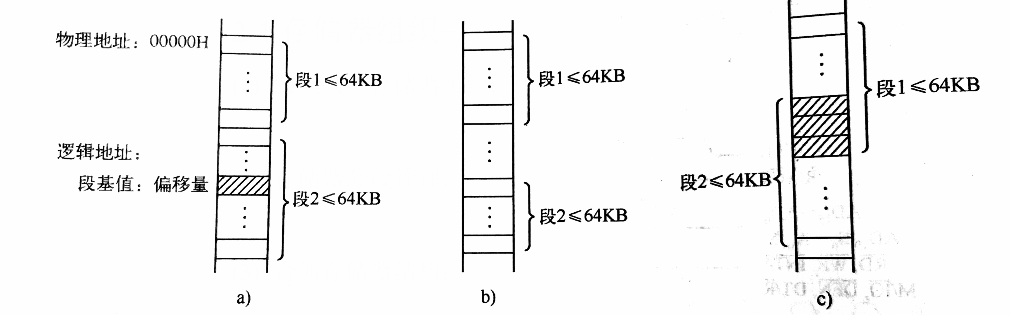

图2-5单元地址的描述 2.4.2存储器分段管理(1) 在软件中8086/8088对存储器采用分段描述的方法,将整个存储区划成很多段,每一段大小可各不相同,但均≤64KB。如下图2-6所示,各段之间可以紧密连接(a),部分或完全重叠(c),也可以不相关(b)。

图2-6 8086/8088内存分段管理 (2) 8086/8088所管理的存储器,所有数据以字节形式存放在存储单元中,每个单元均有一个唯一的20位地址,称为物理地址。每一个存储单元一定处于某个段中,且距该段的起始单元有一个偏移量,如下图2-7所示。指令中描述为段基值:偏移量,称为逻辑地址。通过20位地址加法器可自动完成由16位描述的逻辑地址转换成20位的物理地址。偏移量以字节数计算。

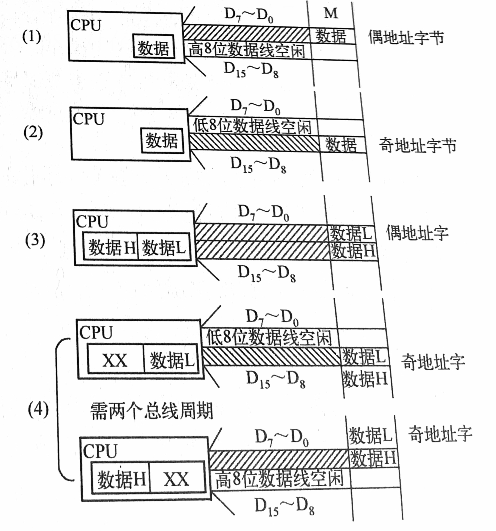

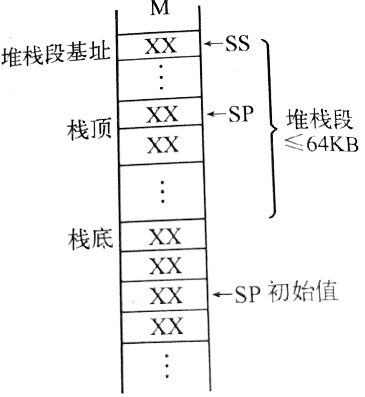

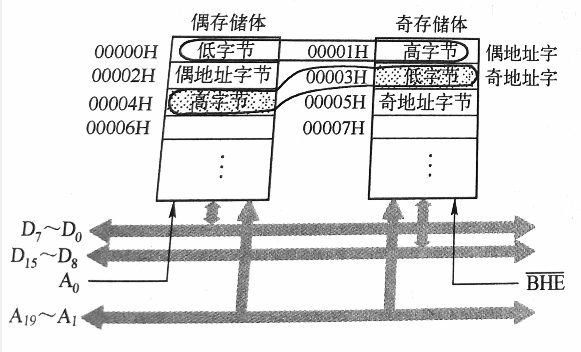

图2-7 物理地址和逻辑地址 (3) 8086/8088微处理器对每个存储单元的描述,一种是20位的物理地址,在地址总线上;一种是由两个16位参数描述的逻辑地址,在指令中。物理地址唯一,逻辑地址不唯一。 (4) 分段方法进行存储器组织的优点:可以使指令系统中大部分指令只涉及16位地址,减少了指令长度,提高运行程序的速度。8086存储空间高达1M,但在程序执行过程中,只在一个较小存储空间运行,段寄存器的值很少改变。 2.4.3奇偶存储器结构8086有16个外部数据总线,为了使8086既可以传输8位数据,又可传输16位数据,8086的存储器采用奇偶两个存储体结构。两块存储体分别用和A0控制,两存储体可同时传输数据,达到传输16位数据的目的,也可以只对某一块存储体传输8位数据。 在总线周期的T1时刻引脚输出为低电平时,表示当前高8位数据总线D15~D8上数据有效。A0引脚输出低电平,则低8位数据线传送数据。 图2-8奇偶存储体结构 当操作字时,对于偶地址字,在一个读/写周期内,低8位数据线传送低字节,高8位数据线传送高字节,此时A0=0、 当操作字节时,若该字节地址为偶数,则在读/写操作周期中,低8位数据线传输数据,高8位数据线空闲,此时A0=0、 图2-9 8086存储器传输特点 2.5堆栈组织(1) 8086/8088的堆栈组织: 堆栈是一个特定的存储区,在内存中开辟一块存储区,专门用来存数据,一端是固定的,一端是活动的,所有的信息存取都在活动的一端进行。栈指针始终指向堆栈的顶部,操作原则是后进先出。 8086/8088微机的堆栈是按字组织的,每次在堆栈中存取数据均是两个字节的操作,数据的高8位存于地址较高单元,低8位存于地址较低单元。 如图2-10所示,堆栈是由堆栈段寄存器SS指定的一段存储区,由SP作为栈指针指向栈顶,即指向存放数据的最小字地址单元。堆栈段可以有一个或多个,每一个堆栈的容量≤64,如果更换堆栈区,应重新设置SS,而且更换SS内容时要紧接着赋给SP新值。

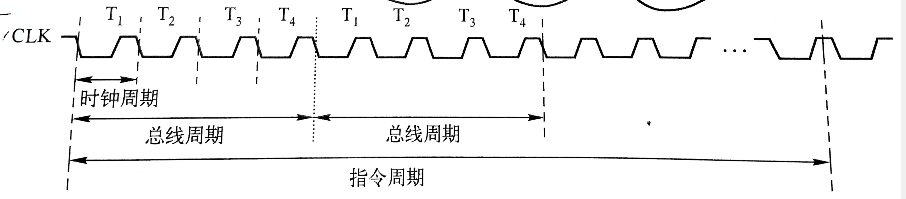

图2-10 8086/8088堆栈组织 (2) 8086/8088的堆栈操作:栈区操作为16位数据操作且默认通过SS:SP访问。 设置栈区:使用栈区之前设置SS和SP的初值,栈区的容量(长度)。 进栈操作:PUSH src;进栈时指针SP先减2,再把1个字压入栈区。SP 出栈操作:POP dest;出栈时栈顶中的字先出栈,然后指针SP加2。低字节 (3) 堆栈操作用途: 堆栈可以作为缓冲器,暂存一些希望运行时不被破坏的参数;调用子程序或中断过程发生时,用堆栈保护断点及现场参数。在子程序返回或中断返回时弹出断点及现场参数,使主程序继续工作;可以利用堆栈实现数据交换。 2.6时序 图2-11时钟周期、总线周期、指令周期 处理器的周期状态可分为时钟周期、总线周期、指令周期。 (1) 时钟周期是两个脉冲信号的前沿之间的间隔,用T表示。取决于系统主频,是处理器完成一个微操作所需的时间,也是处理器的基本时间计量单位。 (2) 总线周期是处理器完成一个基本操作所用的时间。总线读或写操作的周期由4个时钟周期组成。总线周期包括:存储器写总线周期、存储器读总线周期、I/O接口写总线周期、I/O接口读总线周期、中断响应周期、DMA响应周期、复位周期等。 (3) 指令周期是处理器执行一条指令所需的时间。

|

【本文地址】

:最小工作模式/最大工作模式控制信号

:最小工作模式/最大工作模式控制信号 :高8位数据总线允许/状态分时复用线,三态输出。

:高8位数据总线允许/状态分时复用线,三态输出。

=0,如下图2-9中(3)所示。对于奇地址字必须由两个读/写周期完成,第1个周期低8位数据线空闲,高8位数据线传输数据的低字节,此时A0=1、

=0,如下图2-9中(3)所示。对于奇地址字必须由两个读/写周期完成,第1个周期低8位数据线空闲,高8位数据线传输数据的低字节,此时A0=1、