| RISC | 您所在的位置:网站首页 › 咸阳市一模分数线划分情况公布 › RISC |

RISC

|

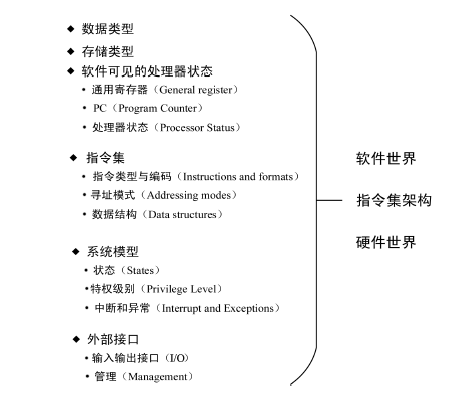

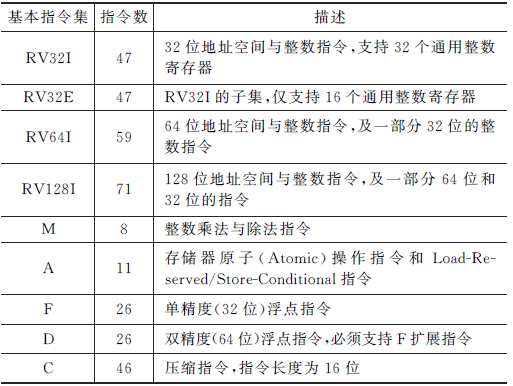

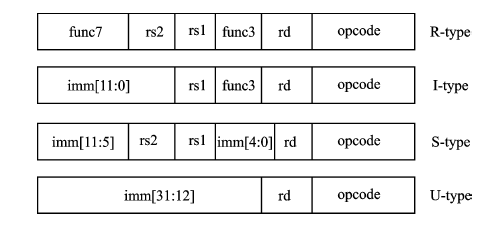

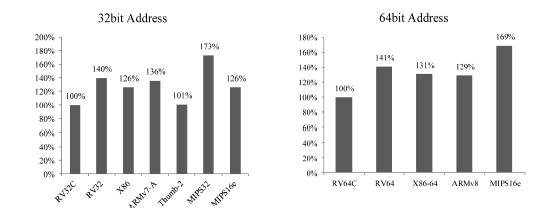

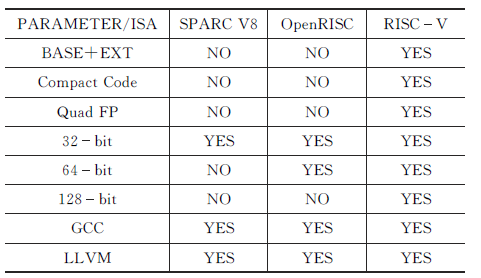

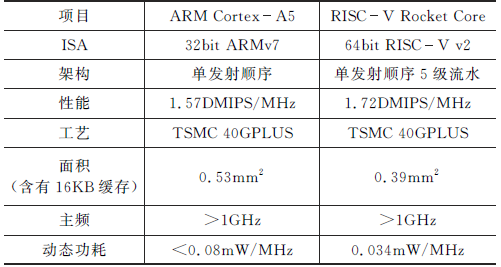

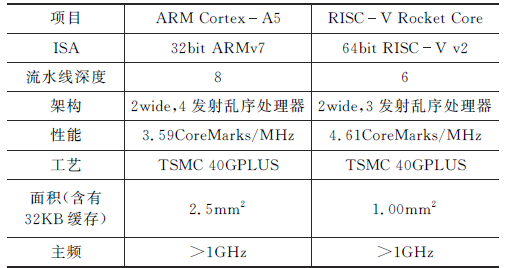

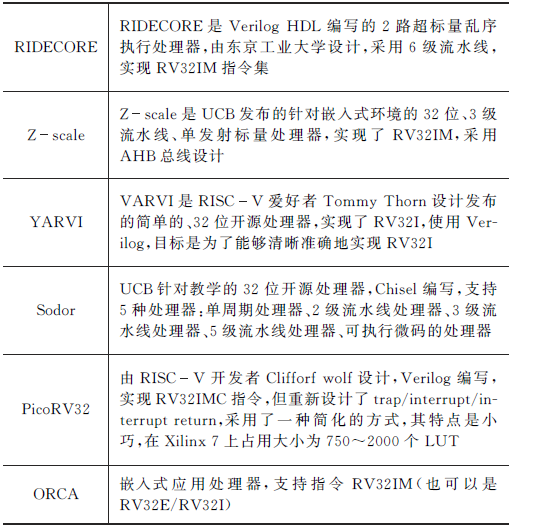

概述 RISC-V是一个基于精简指令集原则的开源指令集架构(Instruction Set Architecture,ISA)。与大多数指令集相比,RISC-V指令集可以自由地用于任何目的,允许任何人设计、制造和销售RISC-V芯片和软件[1]。 RISC-V指令集的设计考虑了小型、快速、低功耗的现实情况来实做,但并没有对特定的微架构做过度的设计[2]。  RISC-V架构 RISC-V架构RISC-V架构主要由美国加州大学伯克利分校的Krste Asanovic教授等开发人员于2010年开发出来的。伯克利的开发人员之所以发明一套新的指令集架构,而不是使用成熟的x86或者ARM 架构,是因为这些架构经过多年的发展变得极为复杂和冗繁,存在着高昂的专利和架构授权问题,修改ARM 处理器的RTL代码是不被支持的,而x86处理器的源代码不可能得到,并且其他的开源架构(譬如SPARC、OpenRISC)均有或多或少的问题。因此,,伯克利的教授与研究人员决定发明一种全新的、简单且开放免费的指令级架构,于是RISC-V架构诞生[3]。 指令集指令集是一组指令的集合,而指令是处理器进行操作的最小单元(譬如加减乘除操作或者读/写存储器数据)。有了指令集架构,便可以使用不同的处理器硬件实现方案来设计不同性能的处理器。处理器的具体硬件实现方案称为微架构(Microarchitecture)。虽然不同的微架构实现可能造成性能与成本的差异,但是软件无须做任何修改便可以完全运行在任何一款遵循同一指令集架构实现的处理器上。 综上所述,指令集架构可以被看作为一个抽象层,如下图所示。  指令集架构示意图 指令集架构示意图1.模块化的指令子集 RISC V的指令集使用模块化方式进行组织,每一个模块使用一个英文字母来表示。RISCV最基本也是唯一强制要求实现的指令集部分是由I字母表示整数指令子集。其他的指令子集部分均为可选的模块,其代表性的模块包括M、A、F、D、C,如下面表格所列。  RISC V的模块化指令集 RISC V的模块化指令集2.规整的指令编码 RISC-V基本指令类型如下图所示,分别为R 类、I类、S类、U 类。RISC V 的指令集编码非常规整,指令所需的通用寄存器的索引(Index)都被放在固定的位置。  RISC V指令格式 RISC V指令格式3.优雅的压缩指令子集 RISC V 架构的研究者进行了详细的代码体积分析,如图3所示,通过分析结果可以看出,RV32C的代码体积相比RV32的代码体积减少了40%。  各指令集的代码密度比较 各指令集的代码密度比较4.开源指令集架构的比较 RISC V与其他开源指令集架构相比,在不同的特性上都有改进,如下表所列。  开源指令集架构比较开源处理器核 开源指令集架构比较开源处理器核Rocket Chip Rocket Core Rocket Core是一款64位、5级流水线、单发射顺序执行的处理器,使用Chisel进行开发。 Rocket Core性能和面积等参数非常具有竞争力,伯克利研究者将Rocket Core与Cortex A5进行了对比。 Rocket Core是64位的架构,Cortex A5是32位架构,但Rocket Core与Cortex A5相比性能大幅度增加,而面积功耗却更小。参数对比如下表所列。  Rocket Core与Cortex A5参数对比 Rocket Core与Cortex A5参数对比BOOM Core BOOM Core也是伯克利开发的一款开源处理器核,面向更高的性能目标,是一款超标量乱序发射、乱序执行的处理器核。 BOOM Core的性能和面积等参数同样非常有竞争力,伯克利将BOOM Core与ARM Cortex A5进行了对比。BOOM Core是64位架构,Cortex A5是32位架构,BOOM Core与Cortex A5相比性能大幅度增加,且面积功耗更小。参数对比如下图所列。  BOOM Core与Cortex A5参数对比 BOOM Core与Cortex A5参数对比PULPino Core与SoC PULPino是由苏黎世瑞士联邦理工学院(ETHZurich)开发的一款开源的单核MCU SoC平台,具有功耗低、面积小的特点。同时ETH Zurich还开发了配套的多款32位RISC V 处理器核,分别是RI5CY、Zero riscy和Micro-riscy。 RI5CY RI5CY是一款四级流水线、按序单发射的处理器,其IPC(Instructions Per Clock)接近1,支持标准的RV32I指令子集,同时可以配置压缩指令子集(RV32C)、乘除法指令子集(RV32M)以及单精度浮点指令子集(RV32F)。它的设计旨在提高超低功耗信号处理应用的能效。 Zero riscy Zero riscy是一款二级流水线、按序单发射的处理器,支持标准的RV32I指令子集,同时可以配置压缩指令子集(RV32C)、乘除法指令子集(RV32M),还可以被配置成16个通用寄存器版本的RV32E。该处理器核主要面向的是超低功耗、超小面积的场景。 Micro riscy Micro riscy是一款面积更加小的处理器核,它仅支持16个通用寄存器版本的RV32EC架构,并且没有硬件的乘除法单元,其面积小于12k个逻辑门。 其他开源处理器 其他开源处理器如下表所列。  内核C语言 内核C语言通过一个实际的框架程序来展示RISC V处理器的C语言启动代码。其中,代码段3是C语言启动代码的实现。代码段4是向量表。 【代码段 3】 #include "riscv_encoding.h" #include snip extern uint32_t __data_load_start__; snip extern uint32_t __bss_start__; snip extern void (*const vector_base[])(void); extern void main(void); snip const struct { uint32_t* load; uint32_t* start; uint32_t* end; }dsection = { snip }; const struct { uint32_t* start; uint32_t* end; }bsection = { snip }; void __attribute__((section(".init"), naked)) reset_handler() { egister uint32_t *src, *dst; snip /*嵌入汇编 */ asmvolatile("csrw 0x307, %0"::"r"(vector_base)); snip asmvolatile("la gp, __sdata_start__+ 0x800"); asmvolatile("la sp, __stack_end__"); snip /*进行系统时钟初始化等*/ init(); /*将数据的初始化值拷贝至RAM */ if(&__vectors_load_start__ ! =&__RAM_segment_start__){ for(uint8_t idx = 0; idx < 3; idx++){ src=dsection[idx].load; dst=dsection[idx].start; while(dst < dsection[idx].end){ *dst=*src; dst++; src++; } } } /*将.bss区域清零*/ for(uint8_t idx=0;idx < 3;idx++){ dst=bsection[idx].start; while(dst |

【本文地址】