| 【MSP430G2553】图形化开发笔记(3) GPIO | 您所在的位置:网站首页 › 君越电动车是什么牌子 › 【MSP430G2553】图形化开发笔记(3) GPIO |

【MSP430G2553】图形化开发笔记(3) GPIO

|

目录

概述IO 的一般读写控制IO 的输出类型图腾柱输出下拉电阻输出上拉电阻输出

MSP430 单片机的 IO 输出IO 的内部电阻线与逻辑的实现

MSP430 单片机的 IO 输入中断IO 外部中断使用方法机械按键的消抖

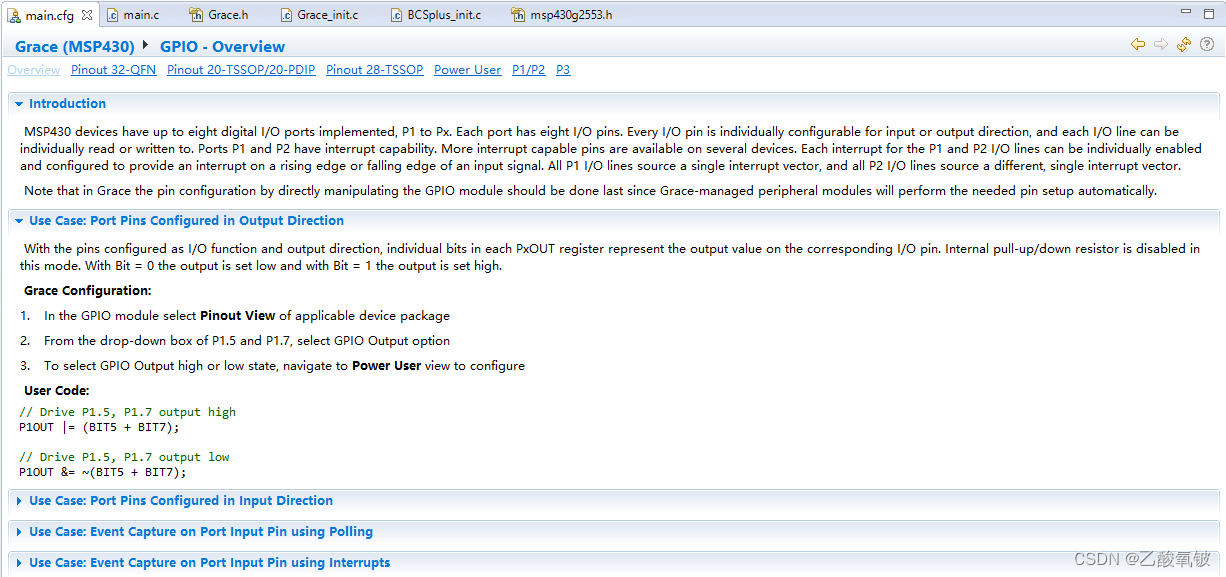

Grace中配置GPIOGPIO-Overview介绍用例:端口引脚配置为输出方向用例:端口引脚配置为输入方向用例:使用轮询对端口输入引脚进行事件捕获用例:使用中断对端口输入引脚进行事件捕获

Pinout View模式Pinout 32-QFNPinout 20-TSSOP/20-PDIPPinout 28-TSSOP

Power User模式寄存器模式

上机实战目标配置Grace编程main.cInterruptVectors_init.c

现象

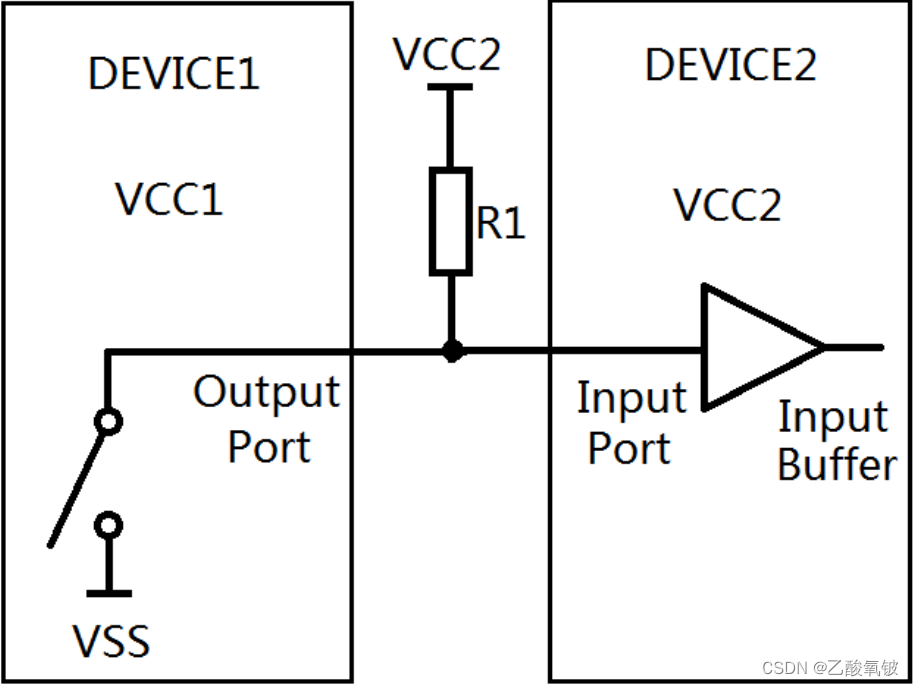

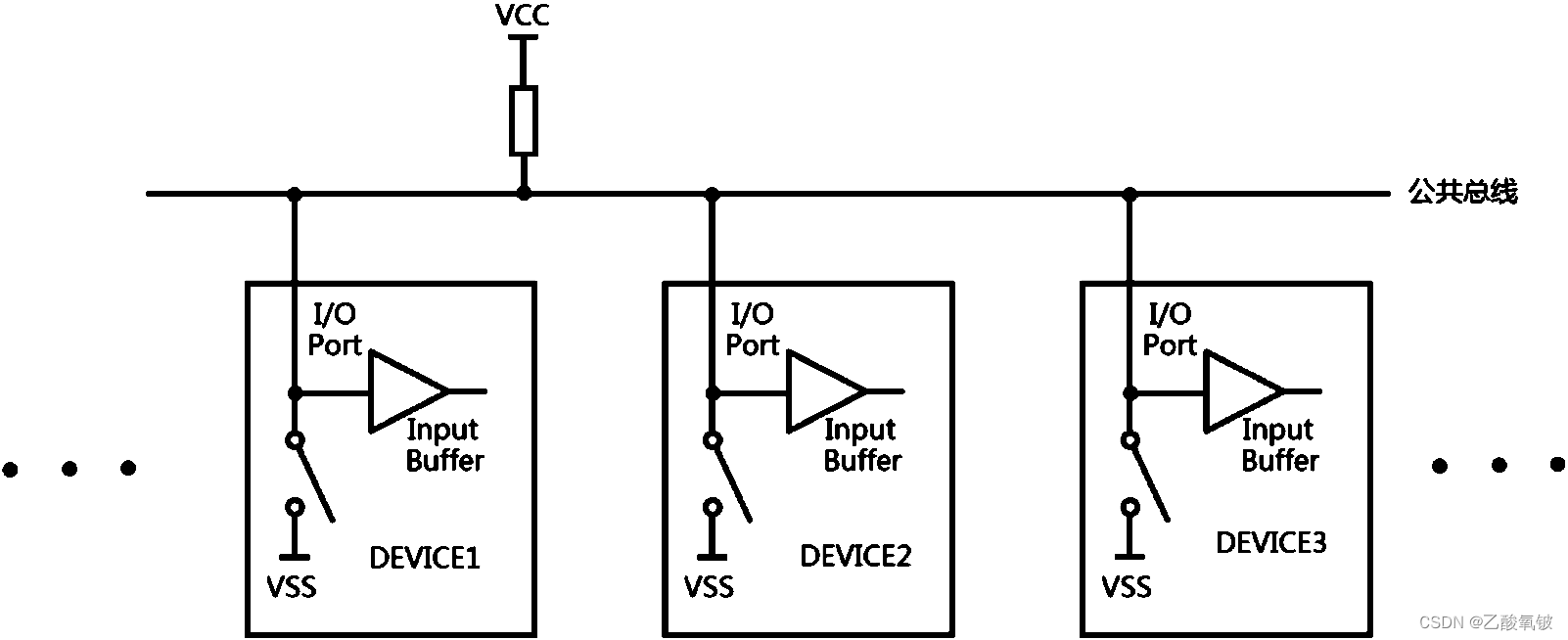

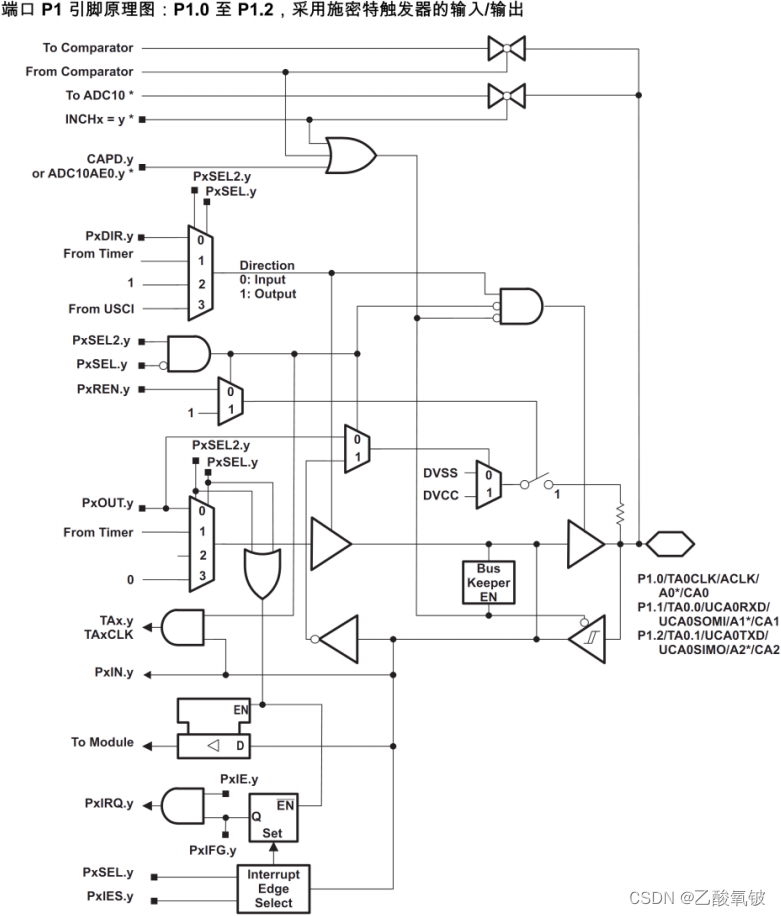

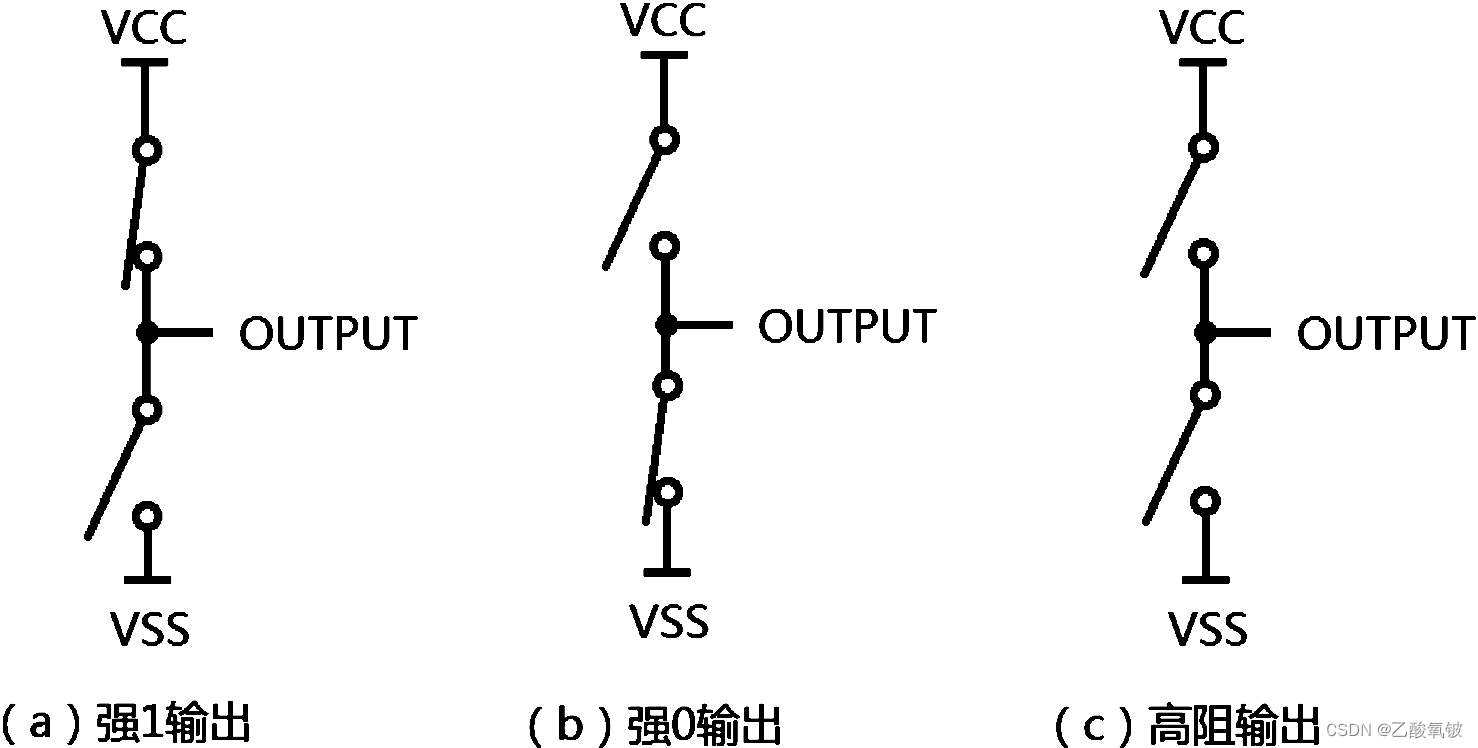

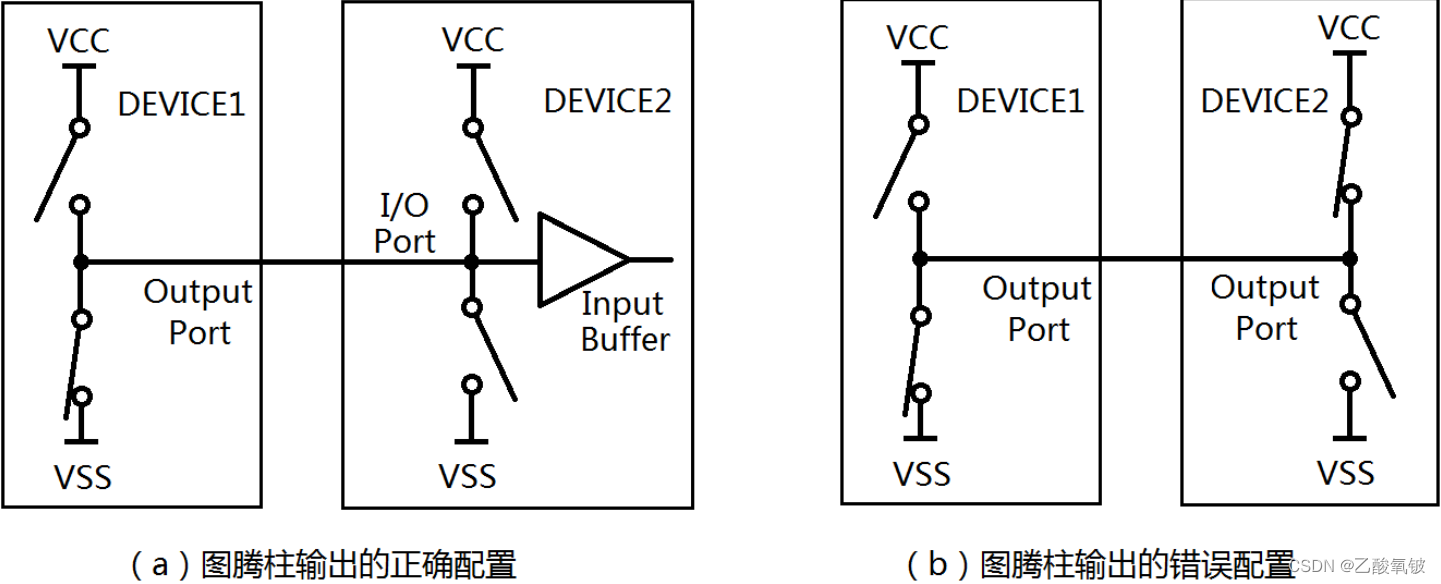

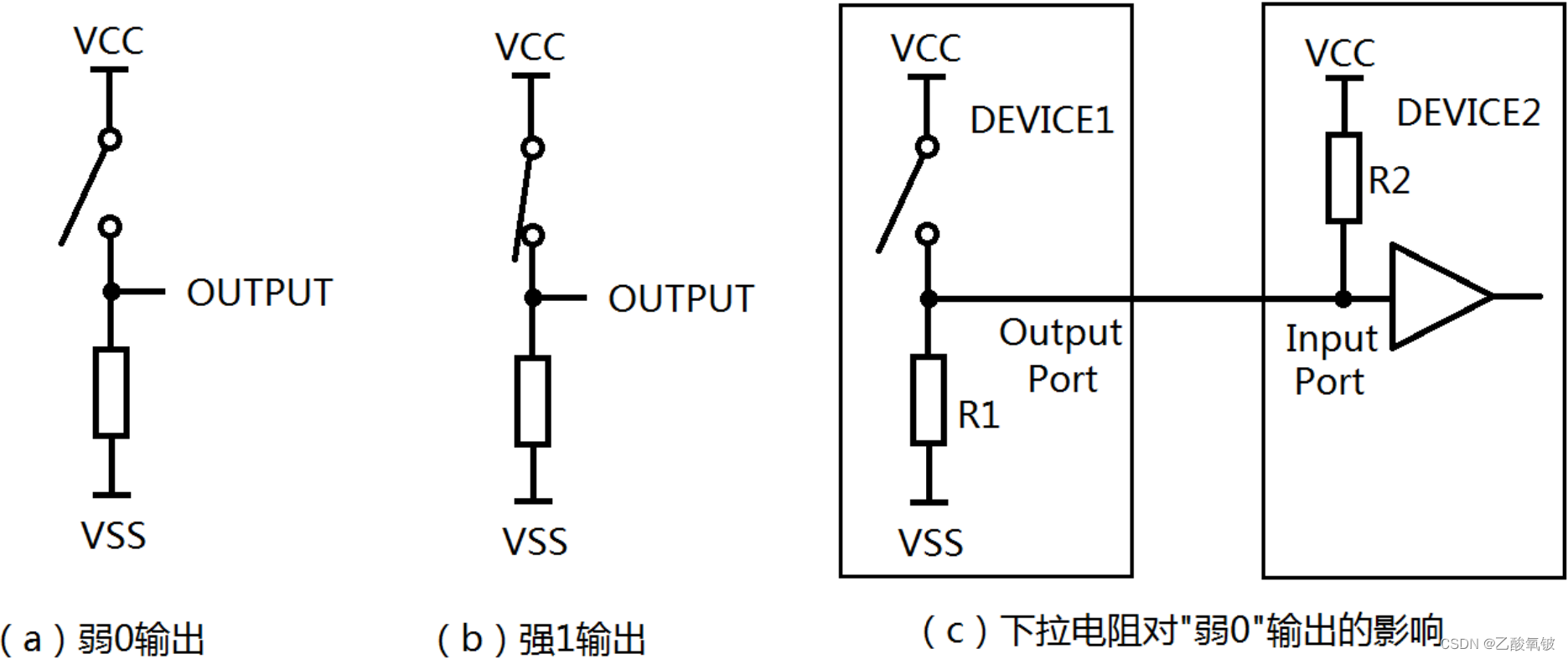

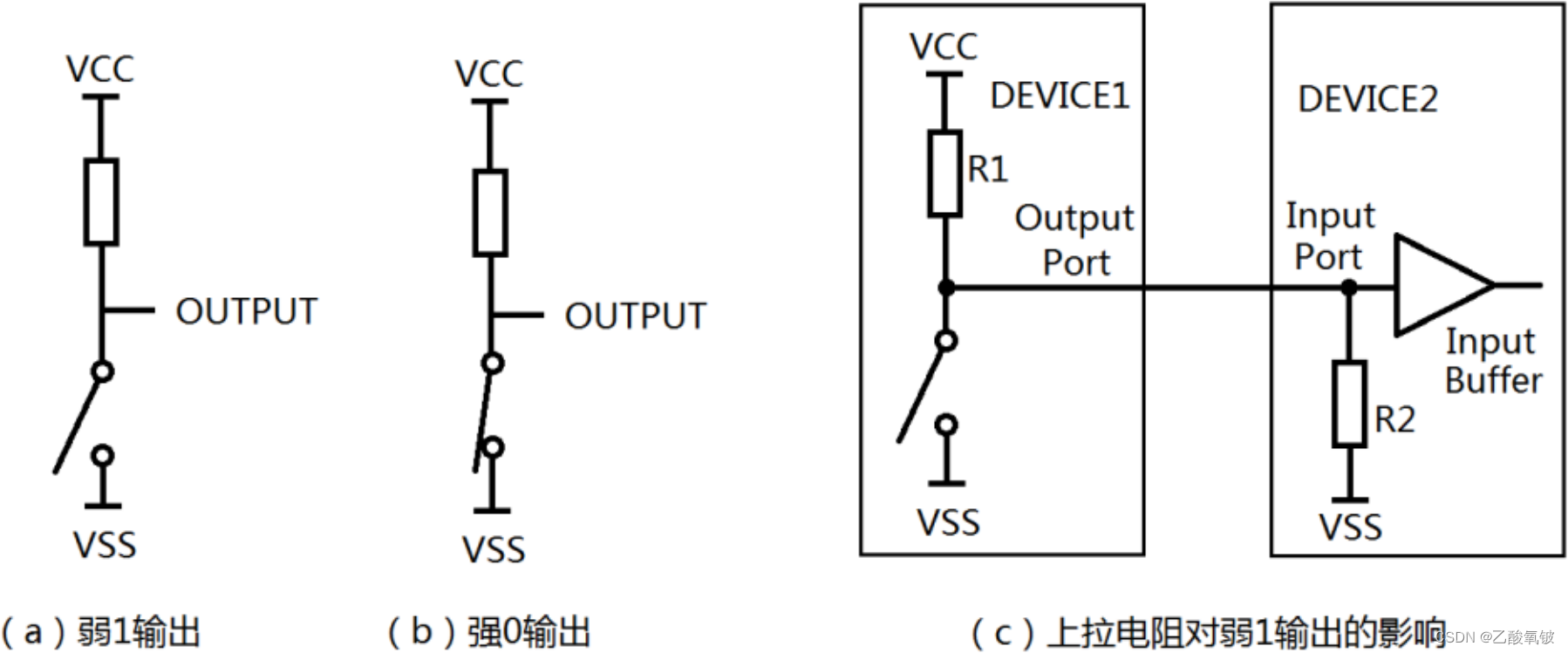

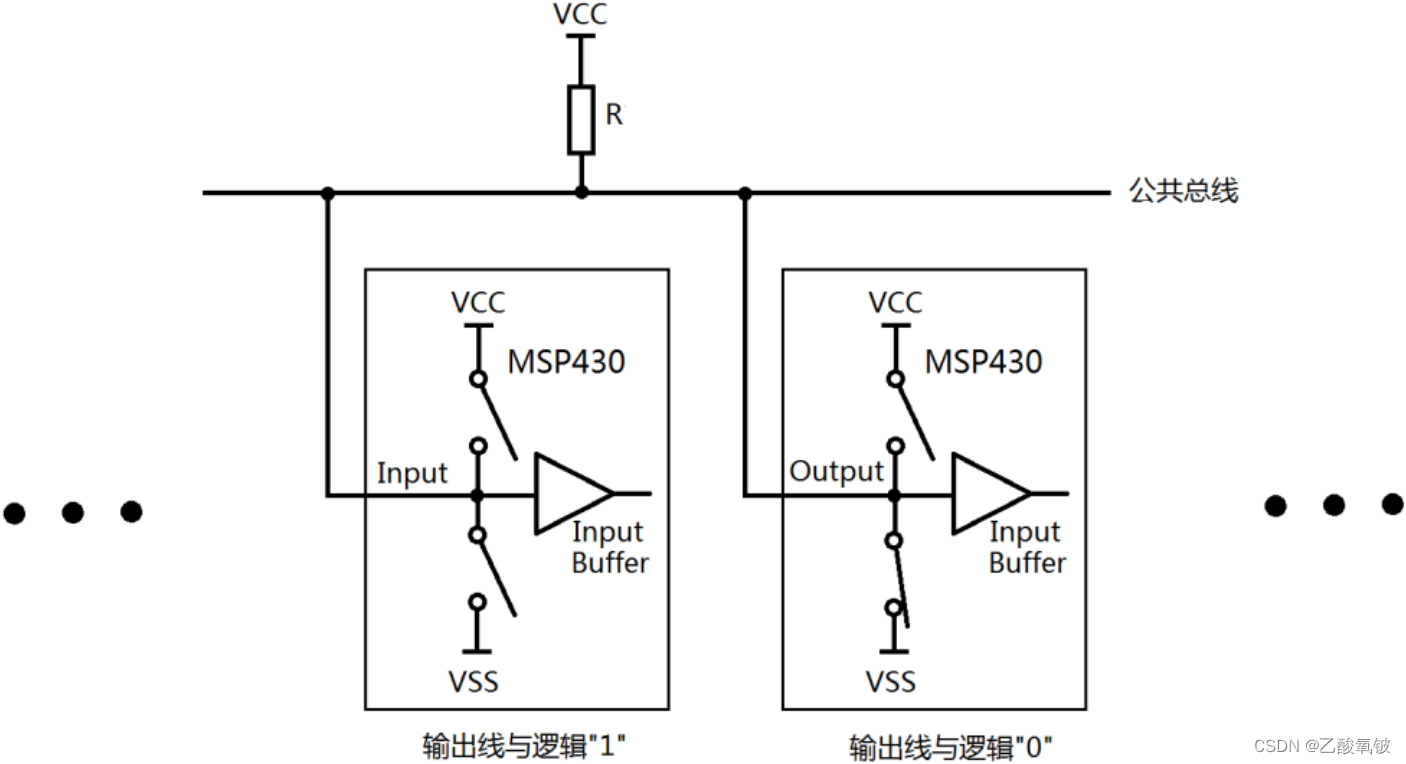

平台: Code Composer Studio 6.2.0 + Grace 2.2.0 MSP430G2553 LaunchPad™ Development Kit (MSP-EXP430G2ET) 以下大部分内容摘自《LaunchPad口袋实验平台 —— MSP-EXP430G2篇》傅强、杨艳 编著(TI大学计划嵌入式微控制器技术丛书) 概述 这是 MSP430G2553 单片机P1.0-P1.2 的原理框图,其他 IO 口的结构还不完全一样。 以上总总迹象表明,IO 口没有最复杂只有更复杂,我们不关心用了多少硬件电路才实现了 IO 的这些功能,我们关心怎么配置寄存器去享用这些功能。 IO 的一般读写控制读写 IO 口前,必须先设置 PxDIR,PxDIR 高电平代表 IO 是输出,低电平代表 IO 口是输入。CPU 读 IO,实际上是读 PxIN 寄存器。CPU 写 IO,实际是写 PxOUT 寄存器。 提示:作为高阻输入 IO 时,务必关掉内部上下拉电阻开关 PxREN,否则输入就不是高阻 态了。 IO 的输出类型数字电路的输出有高电平 1、低电平 0 和高阻态 z。决定高低电平的是 VCC 和 GND,在初学者映像中,VCC 算电源,GND 不算电源,这样的理解不够准确和深刻。GND 也是电源,一样得有吞吐电流的能力,没有 GND 也就没有 VCC。准确的说 VCC 和 GND 都是电压源,所以 GND 经常用 VSS 来代替。根据输出电平的“强弱”分类,可将 IO 输出分为图腾柱输出、上拉电阻输出、下拉电阻输出 3 种。 图腾柱输出 图腾柱、推挽/推拉、Push and Pull、Totem Pole 指的都是同一种电路。下图是图腾柱输出电路简图,图中的开关是受控电子开关,可以由三极管或场效应管构成。由两个开关分别连接 VCC 和 VSS 构成的输出电路称为图腾柱输出,此电路输出为强 1,强 0。 有人可能有疑问,OUTPUT 为强 1 输出接在外部电路的 GND 上会怎样?会短路。那么这种情况下到底还是不是输出 1 呢,这个问题是典型的“自相矛盾”。对于理想电压源VCC,接在哪都得是 VCC,同样对于理想的地,谁接在上面都是 0V,短路情况下到底电压是多少伏,那要看 VCC 和 GND 哪个先“扛不住”了。 初学者还有一个观点,编程并不会“实质性”损坏硬件电路,这也是不确切的。如下图(b)所示,当两个 IO 口相连(这是极其正常普遍的),且两个 IO 是图腾柱输出的话,编程就可以造成硬件损坏。 1) 当程序使得器件 1 输出强 0,器件 2 输出强 1,短路便发生了,是否会永久损坏硬件视短路持续时间的长短。 2) 如果像下图(b)那样,两个图腾柱 IO 都设置为输出,发生短路是迟早的事情。正确的做法是像下图(a)那样,将器件 2 的图腾柱输出变为高阻态,仅作为输入口使用。 3) 现在的新型单片机的 IO 口,多数属于图腾柱输出,所以,在使用 IO 口前正确配置IO 方向尤为重要。从安全考虑,CPU 上电后所有 IO 一般都会设置为下图(a)器件2 那样的输入状态,也就是图腾柱输出为高阻。 下图所示为下拉电阻输出,该电路为强 1 弱 0 电路。 下图(a)输出为弱 0,为什么叫弱 0 呢?因为实际 OUTPUT 输出电平是不是 0 还取决于接什么样的负载。 上图(b)的输出为强 1,无论 OUTPUT 接什么负载,均输出高电平 1。这就是强 1 弱 0 的由来。 与图腾柱输出不同,两个下拉电阻输出的 IO 口相连,永远不会发生短路(前提是两 IO 的 VCC 必须等电位)。 上拉电阻输出 下图所示为上拉电阻输出,该电路为强 0 弱 1 电路。 下图(a)输出为弱 1,为什么叫弱 1 呢? 1) 如果 OUTPUT 接的是高阻负载,输出肯定是 1。 2) 其他负载情况则需根据负载和上拉电阻的分压关系来计算。 3) 如下图©所示,要根据负载情况合理设定上拉电阻的取值。 下图(b)的输出为强 0,无论 OUTPUT 接什么负载,均输出低电平 0。这就是强 0 弱 1的由来。 同样两个上拉电阻输出的 IO 口相连,永远不会发生短路(前提是两 IO 的 VSS 必须等电位)。  上拉电阻输出还广泛用于实现“线与”逻辑。如下图所示,所有器件输出和输入同时进行(图腾柱无法做到这一点),任何一个器件都可以将公共总线电平拉低,但只有所有器件输出都为“高”,公共总线的电平才能为高,这就是“线与”逻辑“线与”逻辑更独特之处在于,所有器件都可以通过输入缓冲一直“监视”总线电平的高低,这样就能知道总线电平是否与“自己期望电平”一致,从而判断是否有别的器件在与自己争夺总线。“线与”逻辑广泛用干多机总线通信中。 上拉电阻输出还广泛用于实现“线与”逻辑。如下图所示,所有器件输出和输入同时进行(图腾柱无法做到这一点),任何一个器件都可以将公共总线电平拉低,但只有所有器件输出都为“高”,公共总线的电平才能为高,这就是“线与”逻辑“线与”逻辑更独特之处在于,所有器件都可以通过输入缓冲一直“监视”总线电平的高低,这样就能知道总线电平是否与“自己期望电平”一致,从而判断是否有别的器件在与自己争夺总线。“线与”逻辑广泛用干多机总线通信中。  MSP430 单片机的 IO 输出

IO 的内部电阻

MSP430 单片机的 IO 输出

IO 的内部电阻

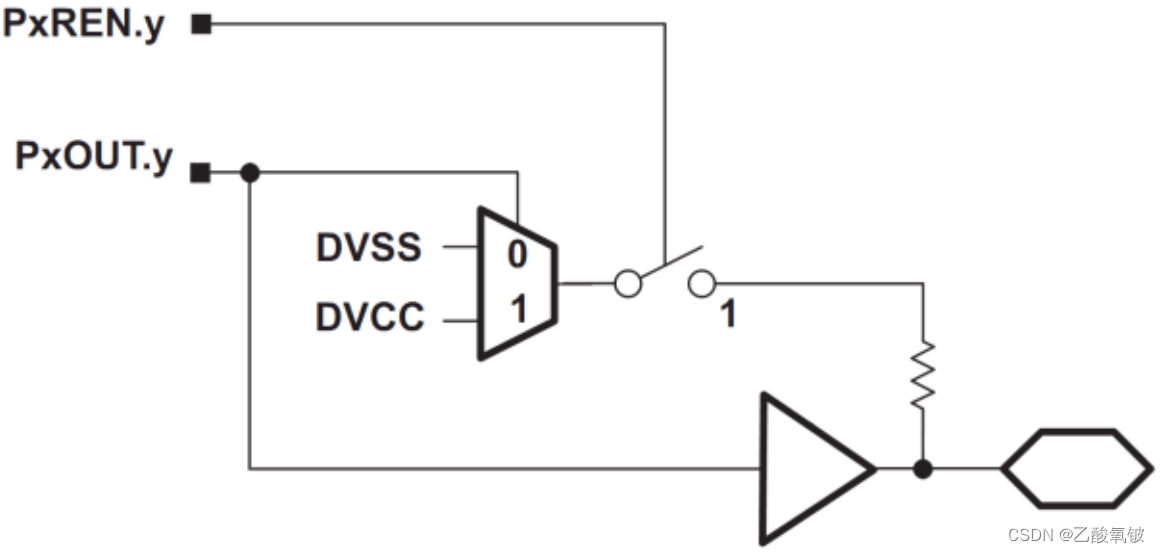

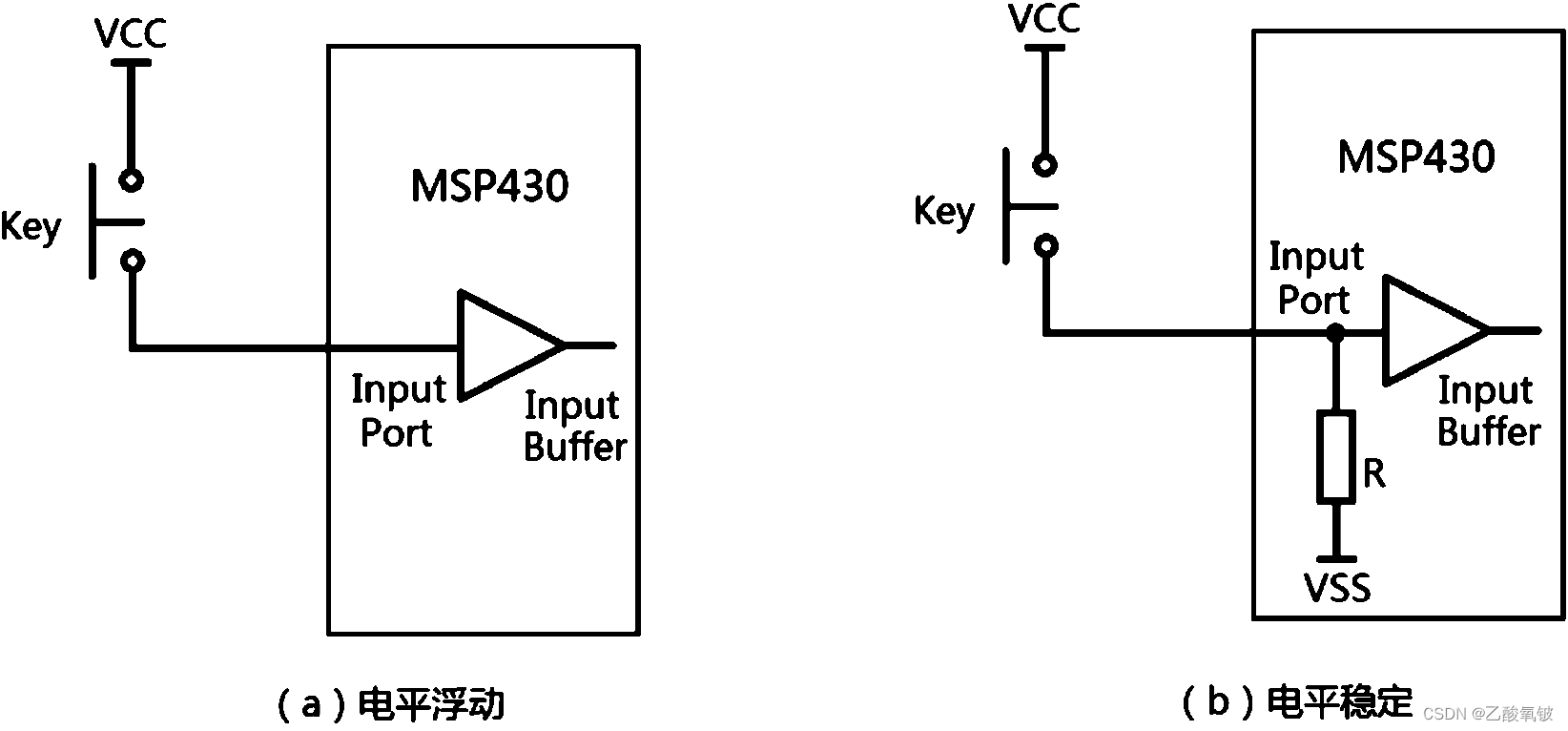

MSP430 单片机的内部电阻构造如下图所示: 注:芯片说明书中,PxOUT(PxREN)中的 x 代表端口号,如 P1 和 P2。PxOUT.y( PxREN.y)中 y 的意思是某个具体的 IO,例如 P1.3 中的 3。 MSP430 的 IO 口内部电阻与 5.3 节的“上拉输出”还是“下拉输出”本质不同,因为图腾柱输出并联上拉下拉电阻丝毫不会改变输出电平值!所以,MSP430 只有一种输出方式——图腾柱输出。 那 MSP430 的内部电阻有什么用呢? 当IO口设为输入口时,内部电阻可通过写PxOUT.y 位固定配置为上拉或是下拉,这样就可以作为输入按键的上下拉电阻使用。如下图(a)所示,按键电路输入高电平1是可靠的,但是输入低电平0则不可靠因为按键不按下时输入被悬空,电平浮动。下图 (b) 所示电路中,启用了内部电阻R并置于下拉,这样一来,输入低电平就是稳定的。同理,也可将开关接在VSS端,使用上拉电阻的方式构建按键电路。

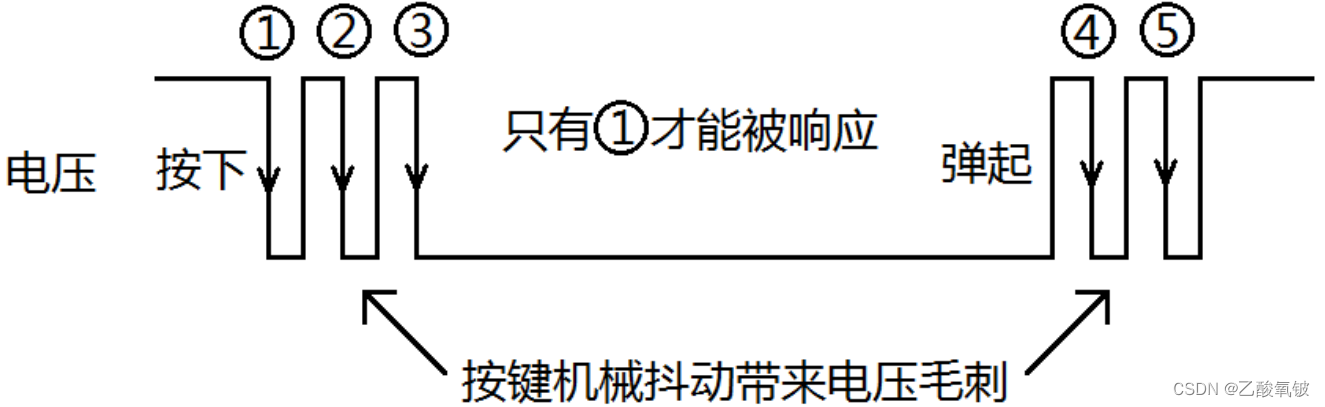

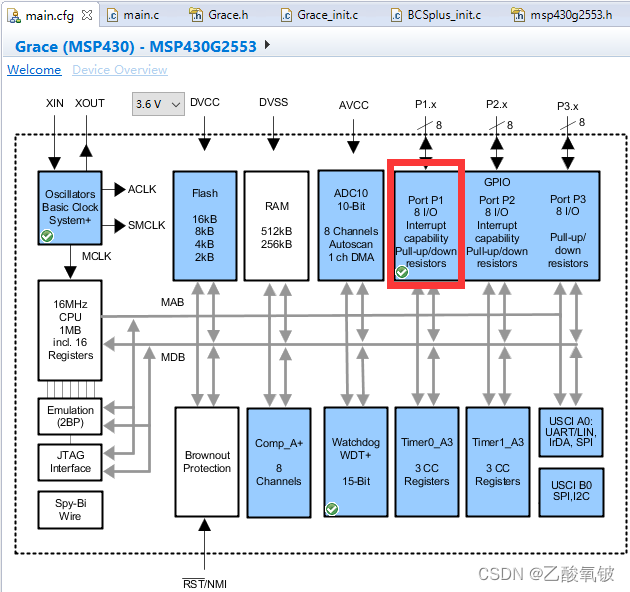

注:宏定义是完全替换代码的意思,所以要注意分号的使用。 这样在后续的程序中,就可以用 P10_ON 和 P10_OFF 代替输出高低电平代码。使用宏定义来消除“硬件差异”的做法是极其有用的编程思想。 MSP430 单片机的 IO 输入中断 IO 外部中断使用方法高级单片机的全部 IO 口都带外部中断功能,比如 ARM 系列。MSP430 单片机只有 P1和 P2 口带外部中断功能。要使用外部中断,遵循以下步骤: 通过 PxDIR 将 IO 方向设为输入。通过写 PxIES,决定中断的边沿是上升沿、下降沿或两种情况均中断。如果是机械按键输入,可以通过 PxREN 启用内部上下拉电阻,根据按键的接法,设定 PxOUT(决定最终是上拉电阻还是下拉电阻)。通过配置 PxIE 寄存器开启 IO 中断,通过“_enable_interrupts();”开启总中断。在中断子函数中,通过 if 语句查询具体中断的 IO 口,如果是机械按键输入,还需有消抖代码。根据具体 IO 的输入,编写事件处理函数。退出中断前,使用“PxIFG = 0;”来清除 IO 中断标志位。 机械按键的消抖 如下图所示,机械按键按下和弹起时,会有毛刺干扰。在一次按键过程中,会有若干次下降沿,只有①是真正的按键事件。如何避免其他几次下降沿“中断”的影响呢? 点击GPIO模块,如Port P1,

MSP430器件最多可以实现八个数字I/O端口,即P1至Px。每个端口有八个I/O引脚。每个I/O引脚都可以单独配置为输入或输出方向,并且每个I/O线都可以单独读或写。端口P1和P2具有中断能力。在一些设备上有更多的中断能力的引脚。P1和P2 I/O线的每个中断可以单独启用和配置,以便在输入信号的上升沿或下降沿提供中断。所有的P1 I/O线的来源是一个单一的中断向量,而所有的P2 I/O线的来源是一个不同的单一中断向量。 请注意,在Grace中,通过直接操作GPIO模块的引脚配置应该最后进行,因为Grace管理的外设模块会自动执行所需的引脚设置。 用例:端口引脚配置为输出方向在引脚被配置为I/O功能和输出方向的情况下,每个PxOUT寄存器中的个别位代表相应I/O引脚的输出值。在这种模式下,内部上拉/下拉电阻被禁用。位=0时,输出被设置为低电平,位=1时,输出被设置为高电平。 Grace配置 在GPIO模块中选择适用器件封装的Pinout View从P1.5和P1.7的下拉框中,选择GPIO输出选项要选择GPIO输出的高电平或低电平状态,请导航到Power User视图来配置用户代码: // Drive P1.5, P1.7 output high P1OUT |= (BIT5 + BIT7); // Drive P1.5, P1.7 output low P1OUT &= ~(BIT5 + BIT7); 用例:端口引脚配置为输入方向在引脚被配置为I/O功能和输入方向的情况下,每个PxIN寄存器中的个别位代表相应I/O引脚的输入值。PxIN寄存器是只读寄存器。位=0表示外部输入信号为低,位=1表示为高。 Grace配置 在GPIO模块中选择适用器件封装的Pinout View从P1.5的下拉框中,选择GPIO输入选项用户代码: // Check P1.5 input status if (P1IN & BIT5) { // P1.5 input level = logic high // >>>>>>>> Fill-in user code here Fill-in user code here Fill-in user code here Fill-in user code here Fill-in user code here |

【本文地址】

为什么 IO 口需要这么复杂的构造呢,我们来列举一下:

为什么 IO 口需要这么复杂的构造呢,我们来列举一下:

1) 如上图(c)所示,器件 1“打算”输出 0 给器件 2,但是器件 2 不是高阻输入结构(比如 TTL 电平器件),那么器件 2 是否能正确识别输入为 0 电平,取决于 R1 和R2 的比值,以及器件 2 的 1/0 识别门限值。 2) 下拉电阻 R1 越小,电平逻辑错误就越不易发生,但是这是以功耗为代价的。

1) 如上图(c)所示,器件 1“打算”输出 0 给器件 2,但是器件 2 不是高阻输入结构(比如 TTL 电平器件),那么器件 2 是否能正确识别输入为 0 电平,取决于 R1 和R2 的比值,以及器件 2 的 1/0 识别门限值。 2) 下拉电阻 R1 越小,电平逻辑错误就越不易发生,但是这是以功耗为代价的。 上拉电阻输出的应用范围非常广泛:

上拉电阻输出的应用范围非常广泛:

在实际编程中,可以用宏定义来消除“模拟”线与逻辑带来的不便。例如,将 P1.0 设为线与逻辑输出,可以用如下宏定义来描述:

在实际编程中,可以用宏定义来消除“模拟”线与逻辑带来的不便。例如,将 P1.0 设为线与逻辑输出,可以用如下宏定义来描述:

该页部分内容机翻如下:

该页部分内容机翻如下: