| VLSI基础 | 您所在的位置:网站首页 › 反相器组成 › VLSI基础 |

VLSI基础

|

第六章 时序逻辑电路

1. 组合电路和时序电路的区别

组合电路:输出是当前输入的函数时序电路: 输出是当前输入和之前输入(状态)的函数

2. 状态机

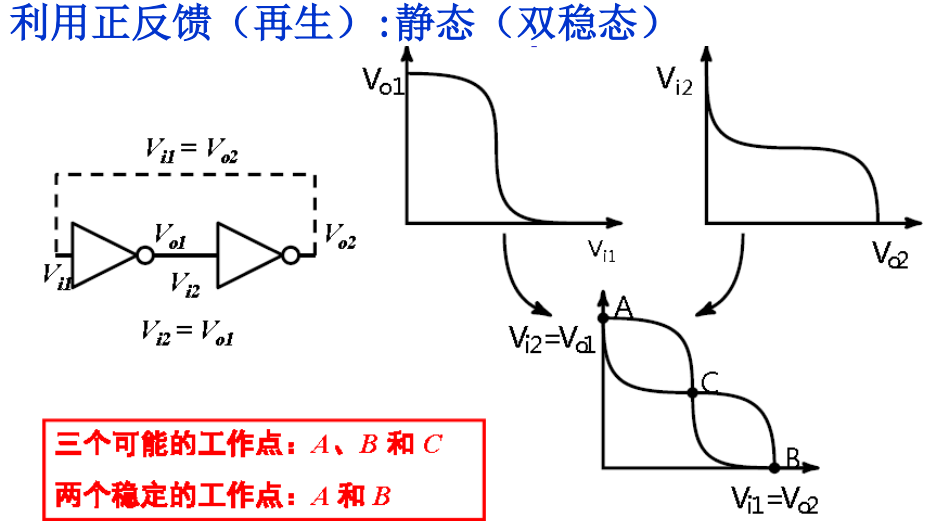

Moore状态机:输出仅仅与当前状态有关; Mealy状态机: 输出同输入和当前状态均有关。 3. 双稳态结构双稳态器件是存储器件的基本模块,双稳器件的的一种电路结构是:交叉耦合反相器 结构。

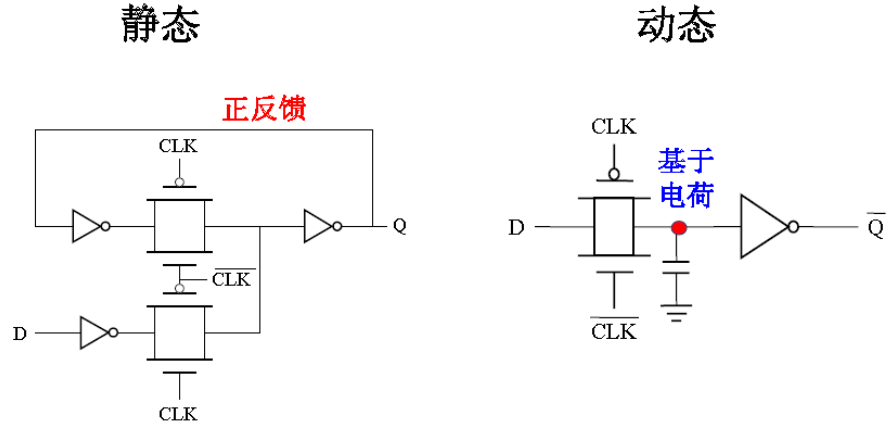

双稳态器件存在两种状态:稳定态和亚稳态。 双稳态器件一般都有两种存储机理: 基于正反馈(静态)基于电荷存储(动态) 4. 静态存储电路

锁存器(Latch)是电平敏感的

一般是时钟低电平时锁存数据 寄存器(Reister)是边沿触发的(edge-triggered)

寄存器是存放二进制数据的器件,通常由Latch构成通常是边沿触发的 触发器(Flip-flops)是交叉耦合的门构成的任何双稳态器件

Latch和Register都可能包含Flip-flop结构包括单稳态、不稳态(震荡)电路

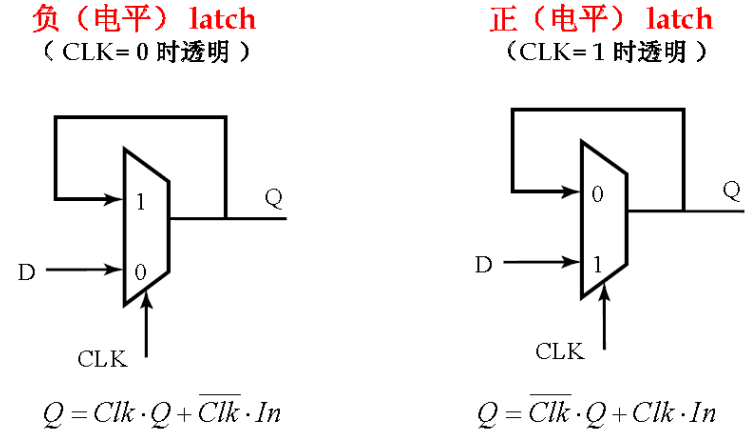

a. Latch

4. 静态存储电路

锁存器(Latch)是电平敏感的

一般是时钟低电平时锁存数据 寄存器(Reister)是边沿触发的(edge-triggered)

寄存器是存放二进制数据的器件,通常由Latch构成通常是边沿触发的 触发器(Flip-flops)是交叉耦合的门构成的任何双稳态器件

Latch和Register都可能包含Flip-flop结构包括单稳态、不稳态(震荡)电路

a. Latch

latch的实现方式可以是Mux构成的:

基于传输门实现的Mux的latch:

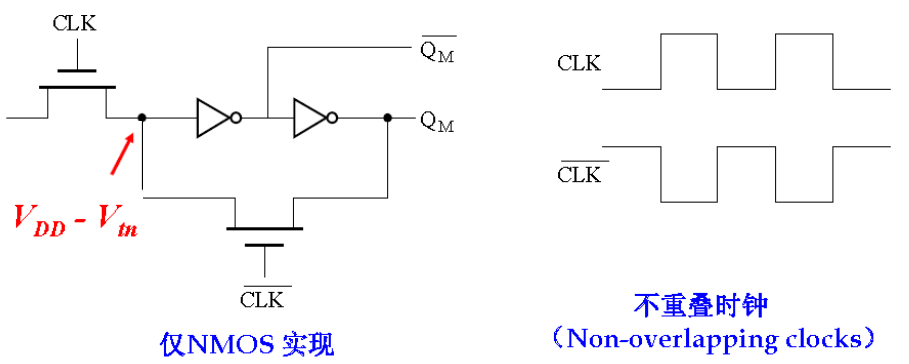

优点: 尺寸设计容易晶体管数目多(时钟负载因而功耗大)基于传输管Mux的Latch:  仅使用NMOS实现,电路简单,减少了时钟负载由电压阈值损失(影响噪声容限和性能,可能引起静态功耗)

仅使用NMOS实现,电路简单,减少了时钟负载由电压阈值损失(影响噪声容限和性能,可能引起静态功耗)

基于三态缓冲器的Latch:  b. D触发器/寄存器

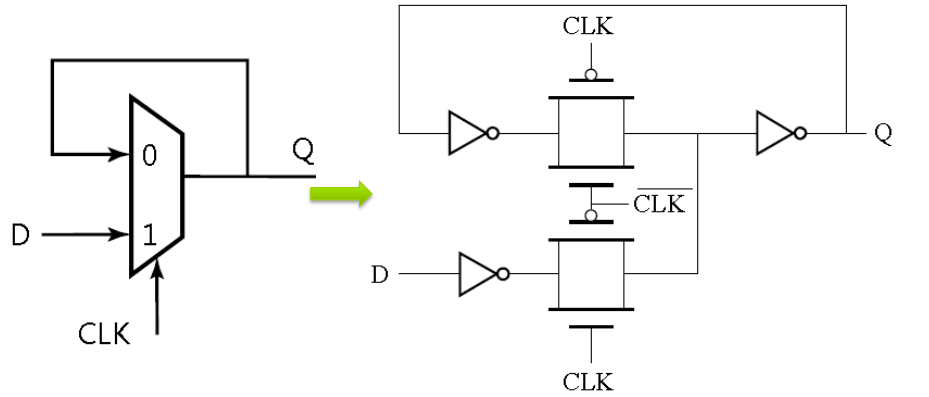

b. D触发器/寄存器

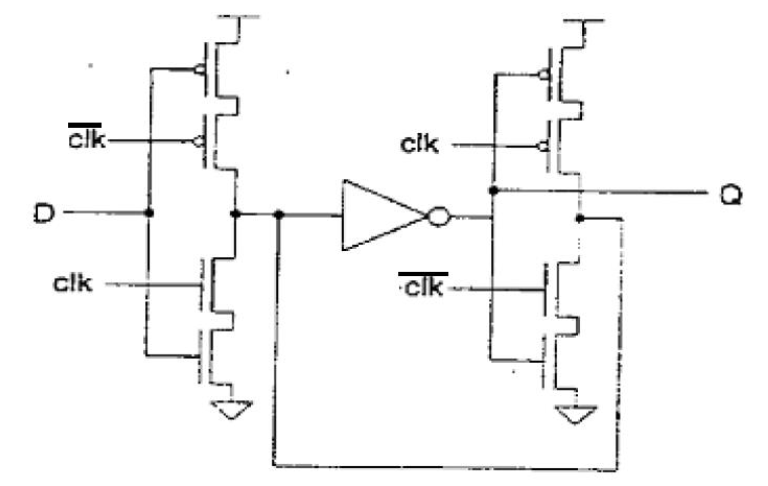

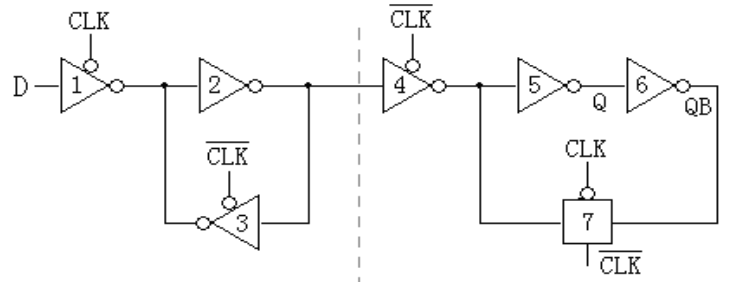

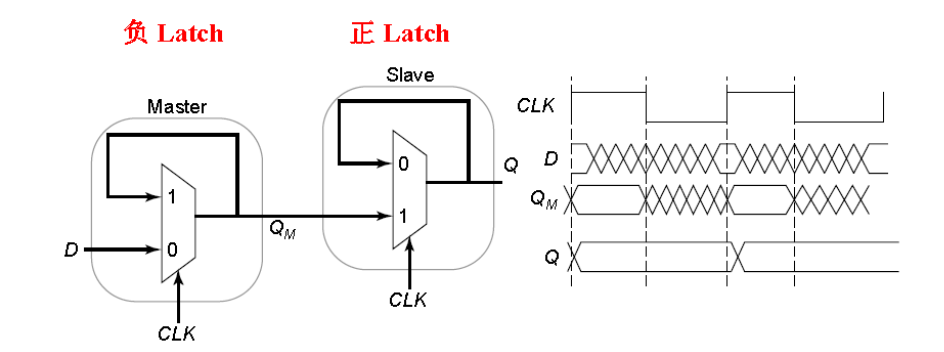

通常是主-从结构, 由一个正电平灵敏Latch和一个负电平灵敏Latch 构成( 主从Latch 对) 输出状态在效果上表现为在时钟边沿处发生变化(正边沿处或负边沿处),确保整个寄存器可能的反馈路径被切断,防止由于反馈造成的信号“竞争”问题。

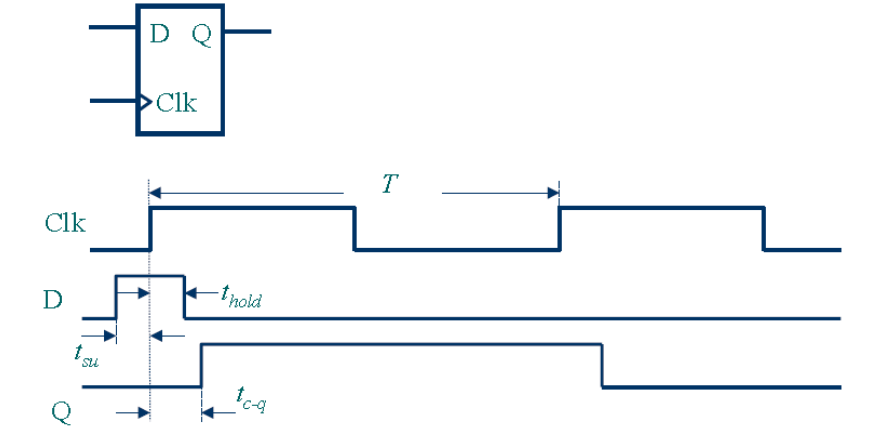

时序参数: Register的时序参数:

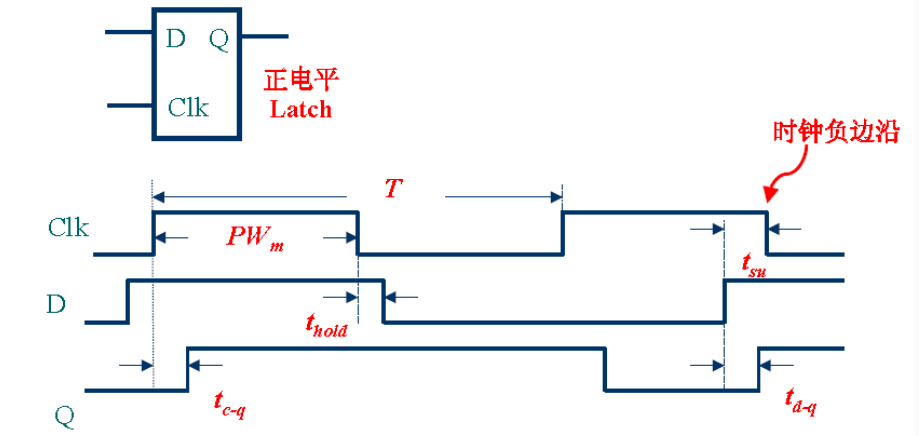

Latch的时序参数:

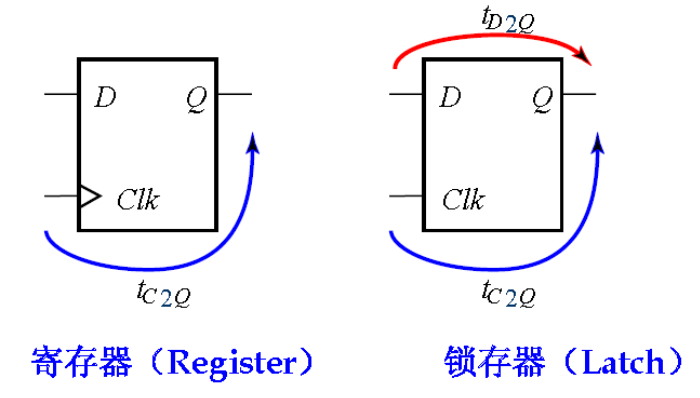

latch的hold时间实际上是半个周期多,如果数据在时钟正半个周期发生变化,输出也将变化。跟register不同的是,latch还有d-q的概念,即数据在透明期间改变到输出响应的时间。 两者的示意图也由差别:

latch的clk没有三角,有三角的代表register。 一般,两个电平灵敏的latch构成主从(Master-Slave)边沿触发寄存器:

高电平时主latch保持,Qm输出不变,Q等于时钟上升沿前的输入D值。效果相当于正沿触发。因此,在时钟上升沿时刻,如果数据D端发生改变,寄存器中仍然存的是D改变之前的值。 Register的工作方式与Verilog中非阻塞赋值的匹配例如如下verilog代码使用非阻塞赋值语句: always @(posedge clk or negedge rst_n) begin if(!rst_n) begin b |

【本文地址】

公司简介

联系我们