| 芯片制造的核心工艺:一文看懂薄膜沉积 | 您所在的位置:网站首页 › 半导体加热膜 › 芯片制造的核心工艺:一文看懂薄膜沉积 |

芯片制造的核心工艺:一文看懂薄膜沉积

|

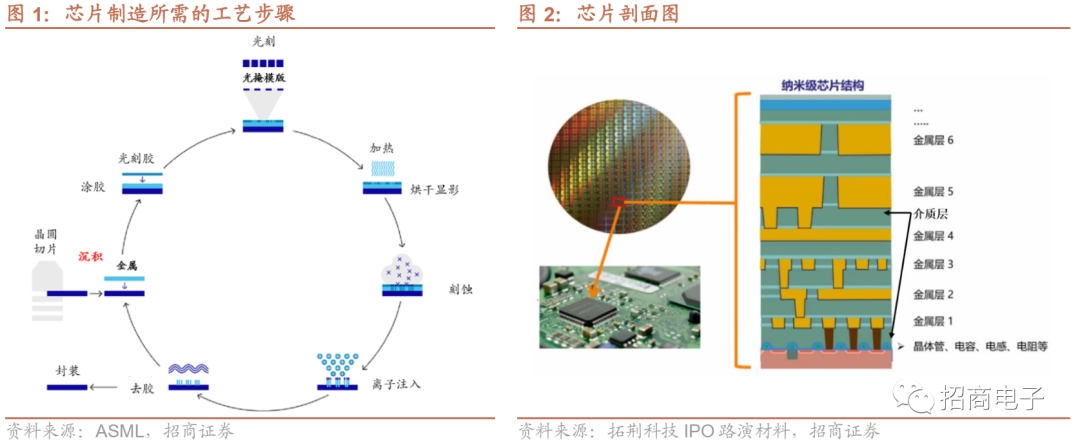

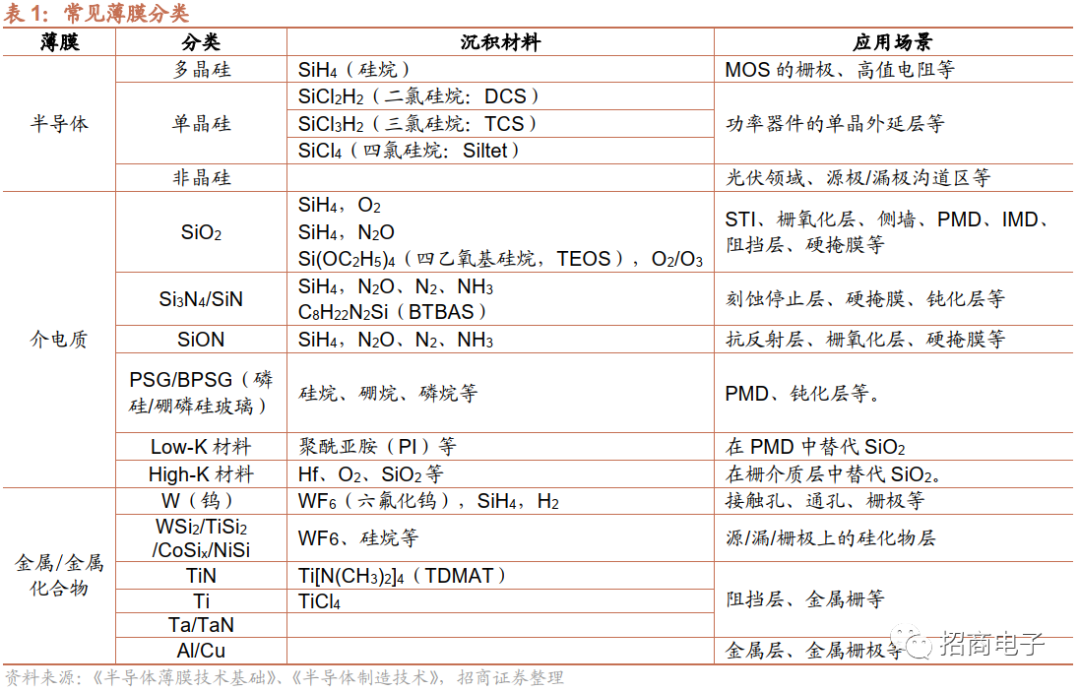

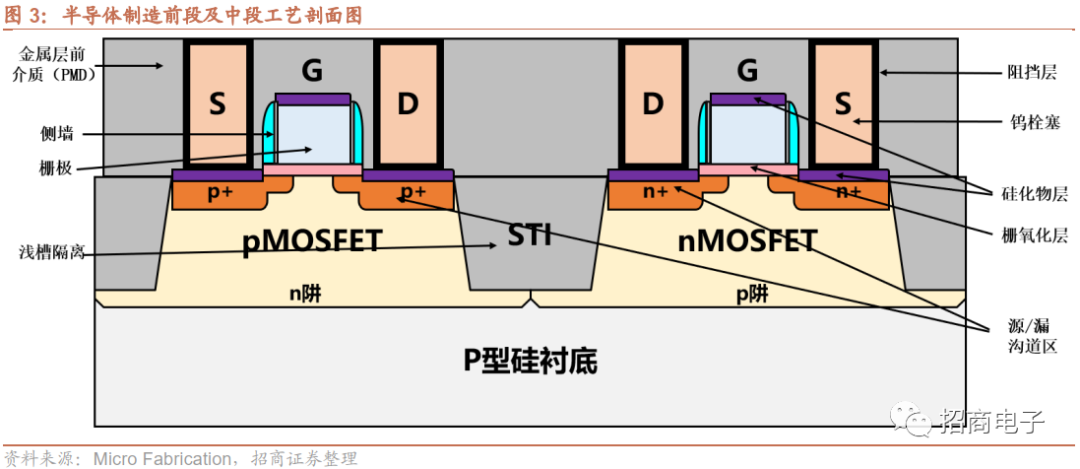

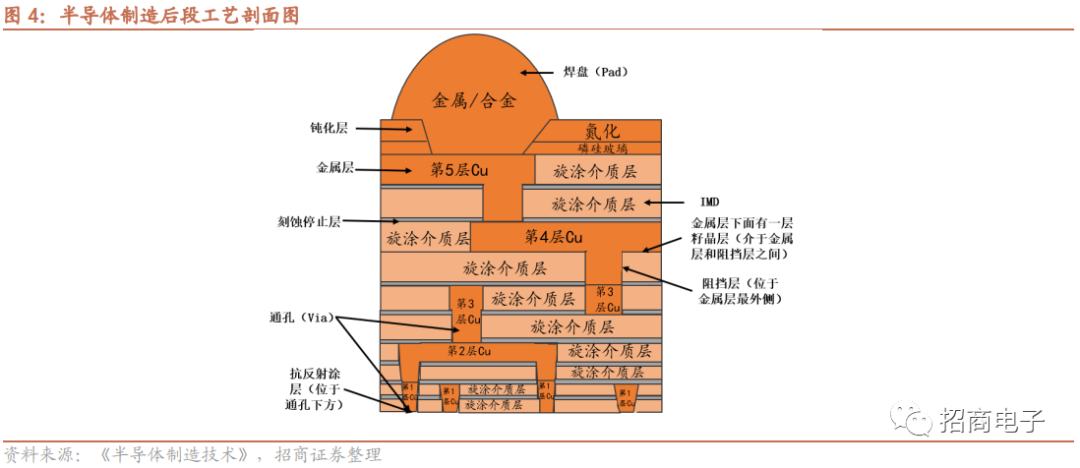

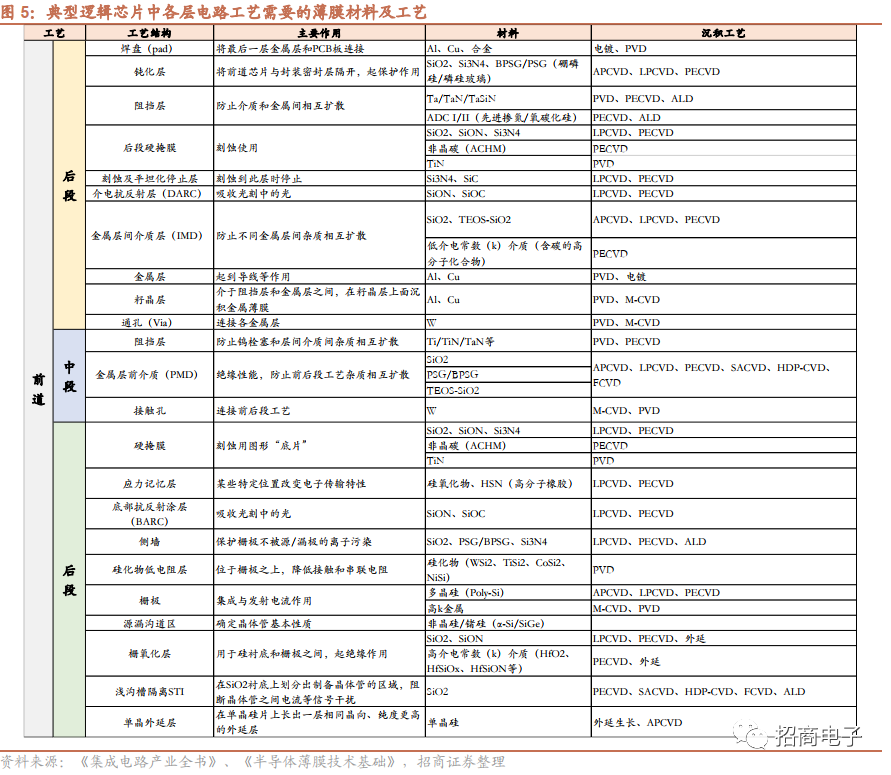

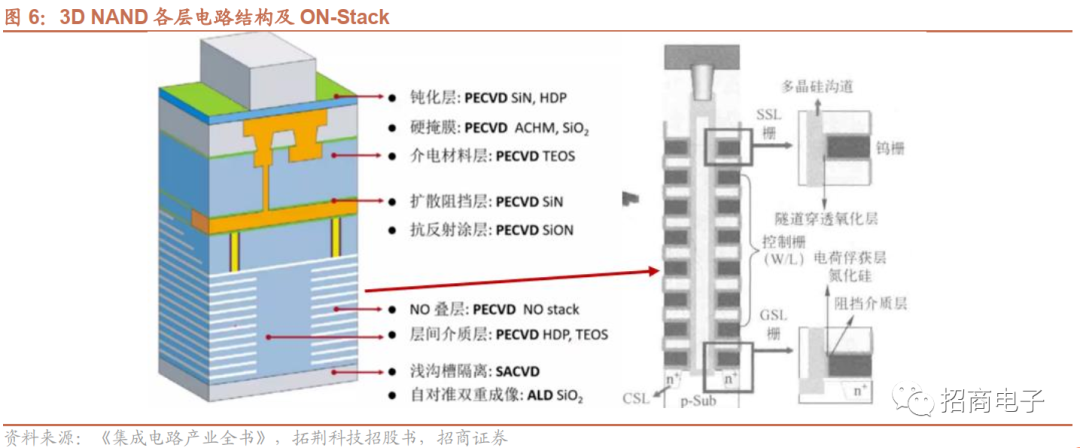

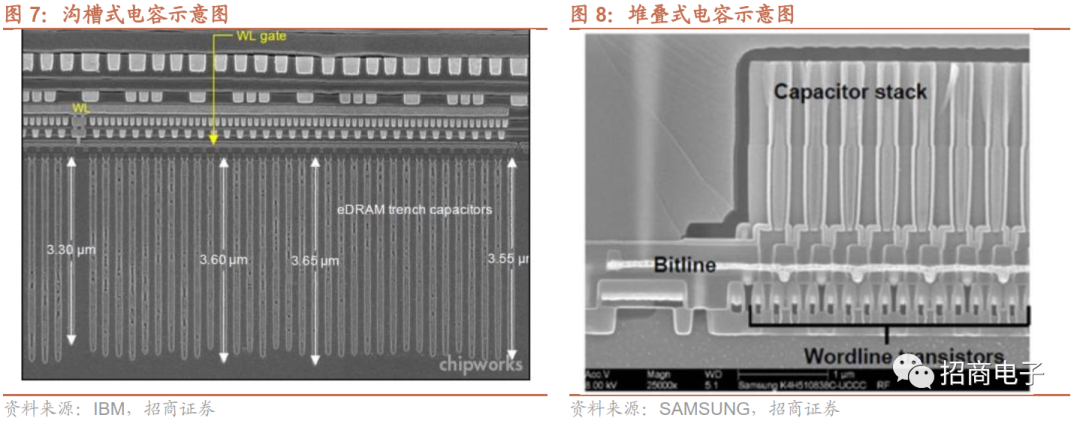

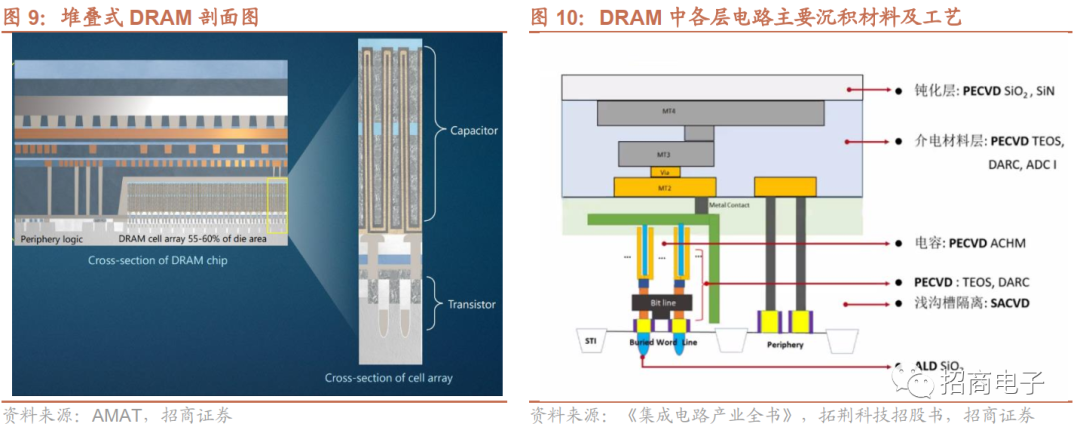

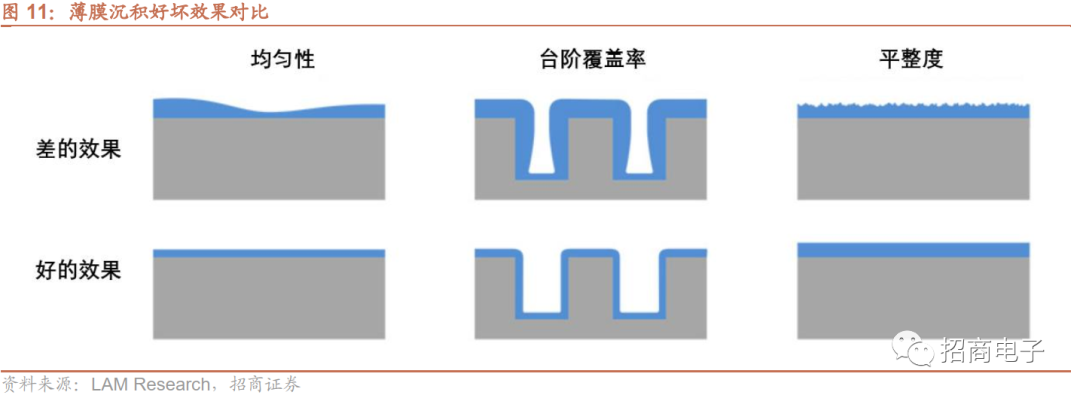

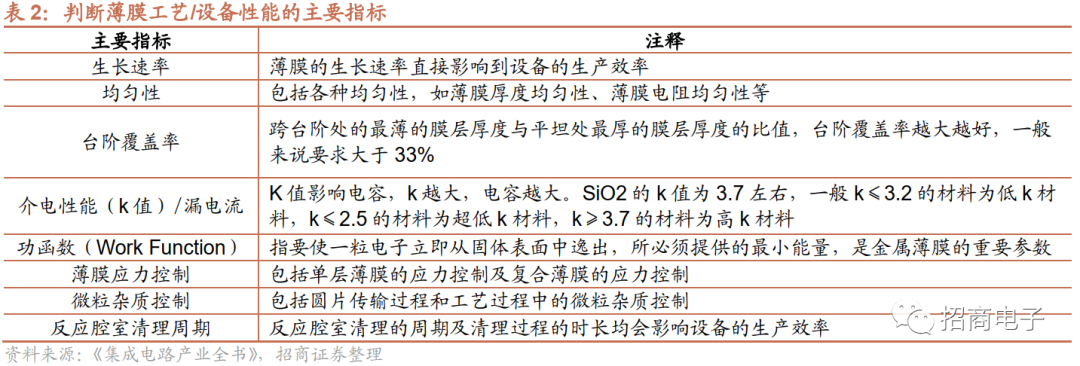

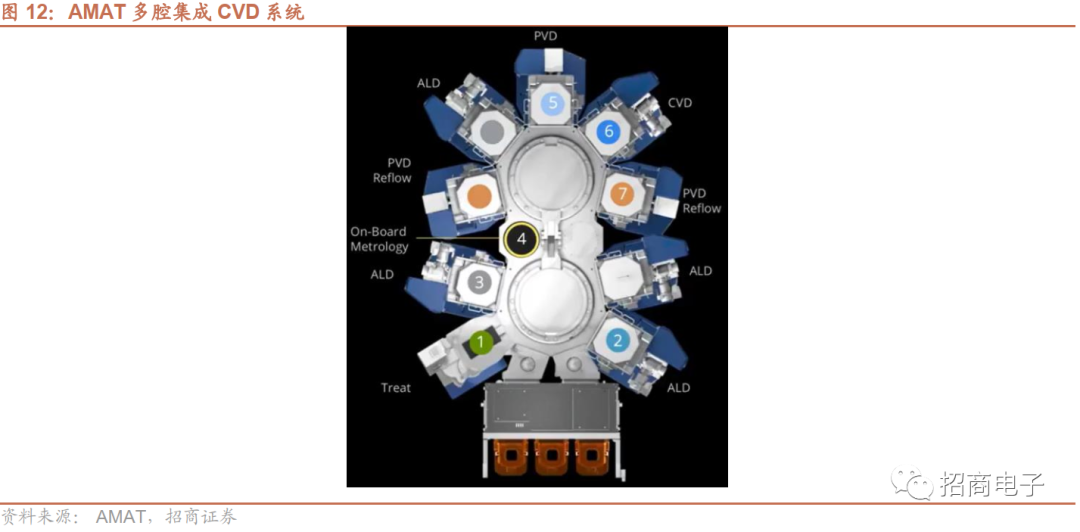

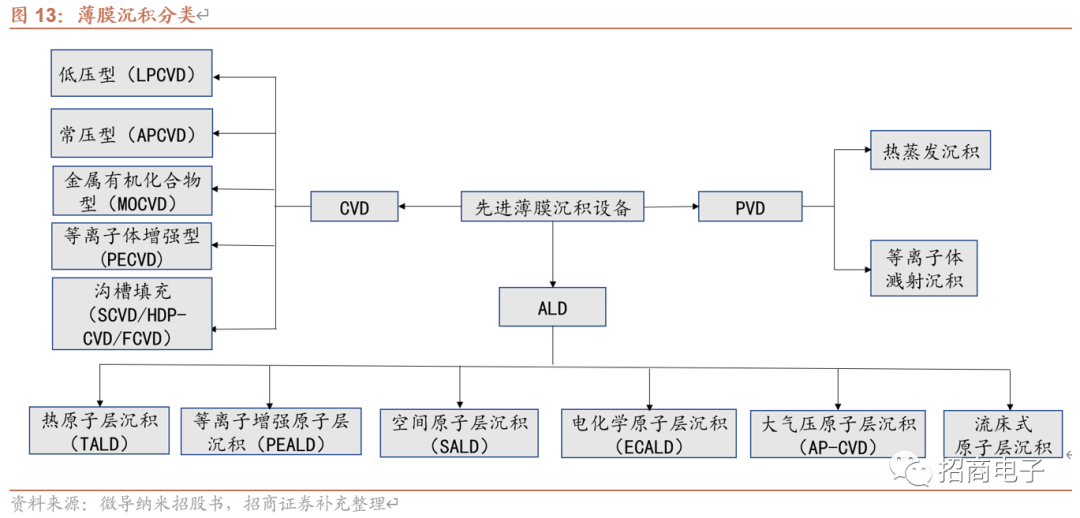

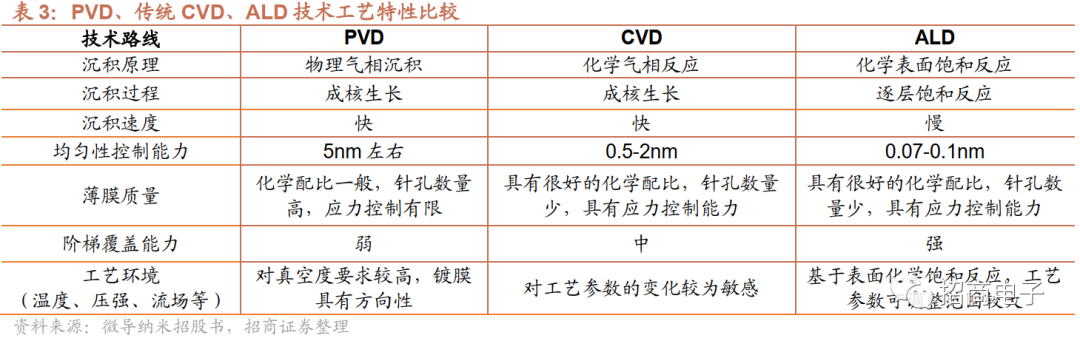

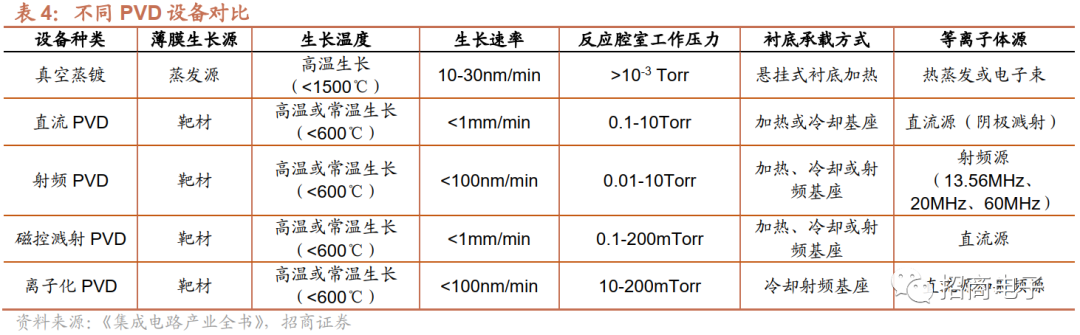

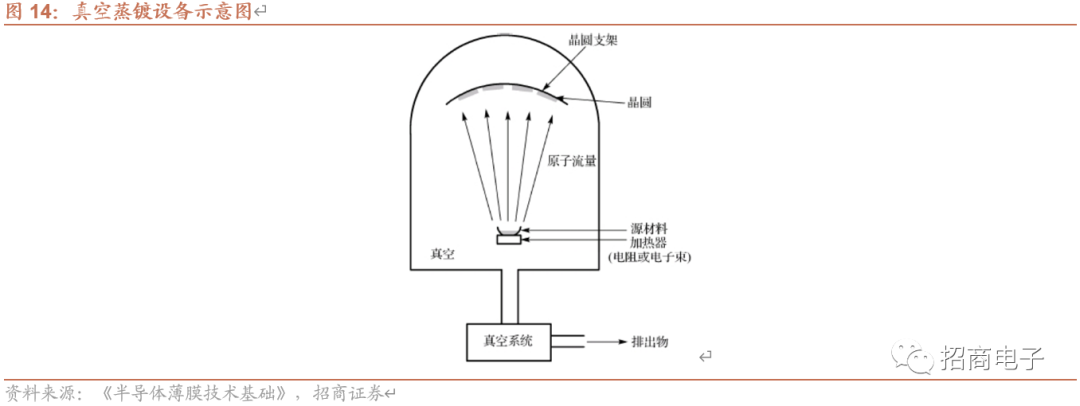

芯片是由一系列有源和无源电路元件堆叠而成的3D结构,薄膜沉积是芯片前道制造的核心工艺之一。从芯片截取横截面来看,芯片是由一层层纳米级元件堆叠而成,所有有源电路元件(例如晶体管、存储单元等)集中在芯片底部,另外的部分由上层的铝/铜互连形成的金属层及各层金属之间的绝缘介质层组成。芯片前道制造工艺包括氧化扩散、薄膜沉积、涂胶显影、光刻、离子注入、刻蚀、清洗、检测等,薄膜沉积是其中的核心工艺之一,作用是在晶圆表面通过物理/化学方法交替堆叠SiO2、SiN等绝缘介质薄膜和Al、Cu等金属导电膜等,在这些薄膜上可以进行掩膜版图形转移(光刻)、刻蚀等工艺,最终形成各层电路结构。由于制造工艺中需要薄膜沉积技术在晶圆上重复堆叠薄膜,因此薄膜沉积技术可视为前道制造中的“加法工艺”。  薄膜沉积是决定薄膜性能的关键,相关工艺和设备壁垒很高。芯片制造的关键在于将电路图形转移到薄膜上这一过程,薄膜的性能除了与沉积材料有关,最主要受到薄膜沉积工艺的影响。薄膜沉积工艺/设备壁垒很高,主要来自:第一,芯片由不同模块工艺集成,薄膜沉积是大多数模块工艺的关键步骤,薄膜本身在不同模块/器件中的性能要求繁多且差异化明显;第二,薄膜沉积工艺需要满足不同薄膜性能要求,新材料出现或器件结构的改变要求不断研发新的工艺或设备;第三,更严格的热预算要求更低温的生长工艺,薄膜性能不断提升要求设备具备更好集成度,另外,沉积过程还要考虑沉积速率、环境污染等指标。下面几节,我们从薄膜种类与应用、芯片制造模块工艺、性能指标等角度来阐释薄膜沉积行业的高壁垒。2、薄膜主要分为半导体、介质、金属三大类,薄膜种类针对不同场景有不同侧重常见的薄膜主要分为半导体、介质、金属/金属化合物薄膜三大类,特点在于沉积材料与不同场景下应用的复杂多样,并且材料的进步伴随制程等的演变,推动薄膜沉积工艺/设备不断研发。1)半导体薄膜:应用范围有限,主要用于制备源/漏极的沟道区、单晶外延层和MOS栅极等。分为单晶硅、多晶硅、非晶硅等,其中多晶硅(Poly-Si)主要用于MOS的栅极等,单晶硅一般采用外延法制备,在单晶表面生长出完全排列有序的单晶体层,非晶硅/锗硅(α-Si/SiGe)主要用于光伏领域和填充半导体前段工艺源/漏的沟道区。2)介质薄膜:应用范围最广泛,主要用于前段的浅槽隔离、栅氧化层、侧墙、阻挡层、金属层前介质层,后段的金属层间介质层、刻蚀停止层、阻挡层、抗反射层、钝化层等,也可以用于硬掩膜。介质薄膜是一类具备绝缘性质的薄膜,主要用来掩蔽芯片任何器件/金属间杂质相互扩散,因此应用范围最为广泛。介质薄膜沉积主要需要考虑薄膜厚度、台阶覆盖率、致密性等。最常见的介质薄膜包括氧化硅、氮化硅、低/高介电常数材料等。①掺杂的/不掺杂的SiO2:应用最广泛的介质薄膜,最主要用于浅槽隔离(Shallow Trench Isolation,STI)、多晶硅栅的栅氧化层与侧墙、层间介质层、阻挡层、硬掩膜等。由于Si元素丰富且SiO2拥有高熔点,允许更宽的工作温度范围,因此SiO2应用最广泛。沉积过程中,SiO2要求足够薄,防止应力作用产生裂纹,同时要满足一定台阶覆盖率要求,尤其是在电极引线和元件互连时的覆盖率。SiO2可以通入硅烷与氧气制备,也可以通入TEOS(Si(OC2H5)4,四乙氧基硅烷)与氧气/臭氧制备,TEOS-SiO2的薄膜性能更好;而在SiO2中掺入杂质可以形成例如对特定离子更好的隔离效果、使薄膜具备更好的填孔能力等特性,常见的如在SiO2中掺入磷杂质形成磷硅玻璃(Phospho-silicate Glass,PSG)或者同时掺入磷杂质和硼杂质形成硼磷硅玻璃(Boro-phospho-silicate Glass,BPSG),一般用于金属前介质层(Pre-metal dielectric,PMD);也可以掺入N元素形成氮氧化物,可用于栅氧化层、硬掩膜、抗反射涂层等;②SiN/Si3N4:绝缘性能好,用于钝化层、刻蚀停止层、硬掩膜、侧墙等工艺。Si3N4的特点是相较SiO2的结构更致密、化学稳定性高,因此更适合用于钝化层和刻蚀停止层等用于掩蔽离子扩散,制备难点在于颗粒的控制;但Si3N4的介电常数很高,一般不作为层间介质(intern-metal dielectric,ILD),否则会导致导体之间产生大的电容;③低介电常数(k)介质:在后段PMD中用来替代传统SiO2。后段金属层级金属层间介质中,电路导线电阻用R表示,寄生电容用C表示,由于R与导体的横截面积呈反比,C与电容极板的距离呈反比,因此随着制程微缩,布线之间的距离减小,电容与电阻均变大,产生RC信号延迟造成信号失真,影响芯片工作速度。因此需要降低R与C,R=ρL/S,ρ是电阻率,L是导线长度,S是横截面积,由于增大导体横截面积不利于制程微缩,因此降低R的办法是选取电阻率更低的导体,比如用Cu替换Al,而在Cu布线之后,很难选择其他导体替代Cu来继续降低电阻;C=kA/d,A是横截面积,d是电介质膜层厚度,降低横截面积会导致电阻R增加,增加电介质膜层厚度会导致间隙填充更加困难,因此降低C的办法通常是降低k值,采用低k材料(例如掺杂氟元素等形成的有机材料)替代SiO2,低k介质的工艺壁垒在于保证薄膜较薄同时实现足够的机械强度、高均匀性等;④高k介质(HFO2、HfSiOx、HfSiON等):用于在栅极氧化层中替代多晶硅栅中的SiO2。晶体管尺寸不断减小,需要维持足够栅电容来保证栅控能力,因此要求栅氧化层厚度继续减薄,然而在栅氧化层物理厚度减薄到低于1.5nm时,器件漏电流大幅增加,因此需要用高介电常数k的介质替代SiO2来维持栅极保持高电容,这样可以在等效栅氧厚度(Equvalent Oxide Thickness,EOT)持续缩小的前提下,使栅介质的物理厚度相对较大,来减少栅介质漏电流;3)金属及金属化合物薄膜:金属薄膜主要用于金属栅极、金属层、焊盘,金属化合物薄膜主要用于阻挡层、硬掩膜等。金属薄膜包括Al、Cu等,具备良好导电性,用于制作电极、导线、超导器件等,关键在于保证沉积速率同时沉积的金属薄膜满足较好的导电性;金属化合物薄膜包括TaN、TiN等。①Al/Cu导线:用于金属籽晶层与金属导线,Al也可以作为金属栅极。0.13um以上的制程普遍使用Al作为导线,但在0.13um以下制程,由于Cu电导率更高,为了减小RC延迟,用Cu替代Al作为导线,既可以保证较高的电导率,同时还能通过减薄厚度降低电容;②钨(W):主要用于接触孔和通孔,也可以用于金属栅极。接触孔(Contact)用于将前段工艺制备的晶体管和后段工艺的第一层金属层连接,通孔(Via)用于将相邻金属层之间的连接,由于PVD制备的Al和Cu台阶覆盖率较低,而采用CVD方法沉积的W台阶覆盖率高,具有填充高深宽比通孔的能力,但是W的电阻率较高,因此W不能用于金属互连层,专门用来填充接触孔和通孔;③TiN/TaN/Ta/Ti等金属化合物:主要用于阻挡层和金属栅极。在前段接触孔和后段通孔外部需要沉积一层阻挡层,用于阻挡W的扩散,在后段Al/Cu金属层外侧也需要制备一层阻挡层来阻止Al/Cu向介质层扩散;④WSi2、TiSi2、CoSi2、NiSi等金属硅化物:主要用于在栅/源/漏极上层的硅化物层。在前段工艺源极、栅极、漏极上面沉积一层金属硅化物,可以降低各电极的电阻,也可以降低栅极对金属层的电阻。 薄膜沉积是决定薄膜性能的关键,相关工艺和设备壁垒很高。芯片制造的关键在于将电路图形转移到薄膜上这一过程,薄膜的性能除了与沉积材料有关,最主要受到薄膜沉积工艺的影响。薄膜沉积工艺/设备壁垒很高,主要来自:第一,芯片由不同模块工艺集成,薄膜沉积是大多数模块工艺的关键步骤,薄膜本身在不同模块/器件中的性能要求繁多且差异化明显;第二,薄膜沉积工艺需要满足不同薄膜性能要求,新材料出现或器件结构的改变要求不断研发新的工艺或设备;第三,更严格的热预算要求更低温的生长工艺,薄膜性能不断提升要求设备具备更好集成度,另外,沉积过程还要考虑沉积速率、环境污染等指标。下面几节,我们从薄膜种类与应用、芯片制造模块工艺、性能指标等角度来阐释薄膜沉积行业的高壁垒。2、薄膜主要分为半导体、介质、金属三大类,薄膜种类针对不同场景有不同侧重常见的薄膜主要分为半导体、介质、金属/金属化合物薄膜三大类,特点在于沉积材料与不同场景下应用的复杂多样,并且材料的进步伴随制程等的演变,推动薄膜沉积工艺/设备不断研发。1)半导体薄膜:应用范围有限,主要用于制备源/漏极的沟道区、单晶外延层和MOS栅极等。分为单晶硅、多晶硅、非晶硅等,其中多晶硅(Poly-Si)主要用于MOS的栅极等,单晶硅一般采用外延法制备,在单晶表面生长出完全排列有序的单晶体层,非晶硅/锗硅(α-Si/SiGe)主要用于光伏领域和填充半导体前段工艺源/漏的沟道区。2)介质薄膜:应用范围最广泛,主要用于前段的浅槽隔离、栅氧化层、侧墙、阻挡层、金属层前介质层,后段的金属层间介质层、刻蚀停止层、阻挡层、抗反射层、钝化层等,也可以用于硬掩膜。介质薄膜是一类具备绝缘性质的薄膜,主要用来掩蔽芯片任何器件/金属间杂质相互扩散,因此应用范围最为广泛。介质薄膜沉积主要需要考虑薄膜厚度、台阶覆盖率、致密性等。最常见的介质薄膜包括氧化硅、氮化硅、低/高介电常数材料等。①掺杂的/不掺杂的SiO2:应用最广泛的介质薄膜,最主要用于浅槽隔离(Shallow Trench Isolation,STI)、多晶硅栅的栅氧化层与侧墙、层间介质层、阻挡层、硬掩膜等。由于Si元素丰富且SiO2拥有高熔点,允许更宽的工作温度范围,因此SiO2应用最广泛。沉积过程中,SiO2要求足够薄,防止应力作用产生裂纹,同时要满足一定台阶覆盖率要求,尤其是在电极引线和元件互连时的覆盖率。SiO2可以通入硅烷与氧气制备,也可以通入TEOS(Si(OC2H5)4,四乙氧基硅烷)与氧气/臭氧制备,TEOS-SiO2的薄膜性能更好;而在SiO2中掺入杂质可以形成例如对特定离子更好的隔离效果、使薄膜具备更好的填孔能力等特性,常见的如在SiO2中掺入磷杂质形成磷硅玻璃(Phospho-silicate Glass,PSG)或者同时掺入磷杂质和硼杂质形成硼磷硅玻璃(Boro-phospho-silicate Glass,BPSG),一般用于金属前介质层(Pre-metal dielectric,PMD);也可以掺入N元素形成氮氧化物,可用于栅氧化层、硬掩膜、抗反射涂层等;②SiN/Si3N4:绝缘性能好,用于钝化层、刻蚀停止层、硬掩膜、侧墙等工艺。Si3N4的特点是相较SiO2的结构更致密、化学稳定性高,因此更适合用于钝化层和刻蚀停止层等用于掩蔽离子扩散,制备难点在于颗粒的控制;但Si3N4的介电常数很高,一般不作为层间介质(intern-metal dielectric,ILD),否则会导致导体之间产生大的电容;③低介电常数(k)介质:在后段PMD中用来替代传统SiO2。后段金属层级金属层间介质中,电路导线电阻用R表示,寄生电容用C表示,由于R与导体的横截面积呈反比,C与电容极板的距离呈反比,因此随着制程微缩,布线之间的距离减小,电容与电阻均变大,产生RC信号延迟造成信号失真,影响芯片工作速度。因此需要降低R与C,R=ρL/S,ρ是电阻率,L是导线长度,S是横截面积,由于增大导体横截面积不利于制程微缩,因此降低R的办法是选取电阻率更低的导体,比如用Cu替换Al,而在Cu布线之后,很难选择其他导体替代Cu来继续降低电阻;C=kA/d,A是横截面积,d是电介质膜层厚度,降低横截面积会导致电阻R增加,增加电介质膜层厚度会导致间隙填充更加困难,因此降低C的办法通常是降低k值,采用低k材料(例如掺杂氟元素等形成的有机材料)替代SiO2,低k介质的工艺壁垒在于保证薄膜较薄同时实现足够的机械强度、高均匀性等;④高k介质(HFO2、HfSiOx、HfSiON等):用于在栅极氧化层中替代多晶硅栅中的SiO2。晶体管尺寸不断减小,需要维持足够栅电容来保证栅控能力,因此要求栅氧化层厚度继续减薄,然而在栅氧化层物理厚度减薄到低于1.5nm时,器件漏电流大幅增加,因此需要用高介电常数k的介质替代SiO2来维持栅极保持高电容,这样可以在等效栅氧厚度(Equvalent Oxide Thickness,EOT)持续缩小的前提下,使栅介质的物理厚度相对较大,来减少栅介质漏电流;3)金属及金属化合物薄膜:金属薄膜主要用于金属栅极、金属层、焊盘,金属化合物薄膜主要用于阻挡层、硬掩膜等。金属薄膜包括Al、Cu等,具备良好导电性,用于制作电极、导线、超导器件等,关键在于保证沉积速率同时沉积的金属薄膜满足较好的导电性;金属化合物薄膜包括TaN、TiN等。①Al/Cu导线:用于金属籽晶层与金属导线,Al也可以作为金属栅极。0.13um以上的制程普遍使用Al作为导线,但在0.13um以下制程,由于Cu电导率更高,为了减小RC延迟,用Cu替代Al作为导线,既可以保证较高的电导率,同时还能通过减薄厚度降低电容;②钨(W):主要用于接触孔和通孔,也可以用于金属栅极。接触孔(Contact)用于将前段工艺制备的晶体管和后段工艺的第一层金属层连接,通孔(Via)用于将相邻金属层之间的连接,由于PVD制备的Al和Cu台阶覆盖率较低,而采用CVD方法沉积的W台阶覆盖率高,具有填充高深宽比通孔的能力,但是W的电阻率较高,因此W不能用于金属互连层,专门用来填充接触孔和通孔;③TiN/TaN/Ta/Ti等金属化合物:主要用于阻挡层和金属栅极。在前段接触孔和后段通孔外部需要沉积一层阻挡层,用于阻挡W的扩散,在后段Al/Cu金属层外侧也需要制备一层阻挡层来阻止Al/Cu向介质层扩散;④WSi2、TiSi2、CoSi2、NiSi等金属硅化物:主要用于在栅/源/漏极上层的硅化物层。在前段工艺源极、栅极、漏极上面沉积一层金属硅化物,可以降低各电极的电阻,也可以降低栅极对金属层的电阻。 3、逻辑/存储芯片由多重模块堆叠,模块复杂性构筑薄膜沉积工艺技术高壁垒芯片工艺分为前道制造和后道封装两个部分,其中前道制造工艺又分为前、中、后三段工艺,前段和后段工艺分别形成晶体管等器件和金属布线,中段工艺用于将二者连接。1)前段工艺(Front end of line,FEOL):形成芯片底层晶体管等有源MOS器件的过程,主要包括浅槽隔离、源漏极、栅极、侧墙等。在其中,薄膜沉积的主要壁垒在于实现浅槽隔离中薄膜的填充和栅氧化层的厚度减薄等。①浅槽隔离(STI):使用薄膜主要为SiO2,薄膜沉积的壁垒在于填充过程中不会在沟道内部残留孔隙。STI目的是在Si衬底上划分出制备晶体管的区域,保证不同晶体管工作过程中不会相互干扰。STI的角度和深度不同对器件特性造成很大影响,同时随着制程进步,要求沟槽深宽比逐渐增大,因此要求刻蚀能够精准控制沟道深度,也需要保证沉积之后被填充的沟道内部不会残留孔隙而影响隔离效果。另外,由于沟槽区域尺寸差异较大,对CMP工艺也有所挑战;②源漏沟道工艺:使用非晶硅/锗硅填充沟道区,使用TEOS-SiO2和Si3N4等形成侧墙。沟道工艺是IC的核心工艺之一,确定了晶体管的基本性质,主要工艺是在离子注入形成源极/漏极;在1980s,为了改善短沟道效应(沟道缩小引起的载流子速度饱和,器件性能减弱)而引入侧墙,需要在栅极侧面形成并靠近源漏,防止源漏区的离子对栅极造成污染,关键在于对侧墙厚度精确控制,同时要求侧墙保持较好的隔离效果;对于40nm以下的工艺,通过外延法制备α-Si/SiGe可以对沟道区施加应力,可以提高MOSFET的开关速度;③栅极工艺:集成电路工艺中最关键的步骤,直接影响IC性能,主要用多晶硅/金属作为栅极,用SiO2、SiON、高k介质(HFO2、HfSiOx、HfSiON等)作为栅氧化层,其中薄膜沉积的壁垒在于保证栅氧化层尽可能薄。栅极制作中需要用到最先进的光刻、刻蚀与薄膜沉积工艺及设备,一般在45nm以上制程中,使用氧化方法制备SiO2作为栅氧化层,在栅氧化层上通过CVD方法沉积多晶硅并经过刻蚀形成多晶硅栅;制程进步要求栅氧化层不断减薄来维持栅电容,但在45nm以下制程之后,栅氧化层厚度低于1.5nm,器件漏电流大幅增加,不得不选用介电常数更高的高k介质替代传统SiO2作为栅氧化层,相当于在维持同样栅电容同时增加了等效栅氧化层厚度,同时,由于金属/金属化合物可以降低电阻率等,避免多晶硅栅的耗尽效应,在45nm制程之后逐渐替代多晶硅作为栅极;④硅化物层:使用WSi2、TiSi2、CoSi2、NiSi等。在源漏沟道区或者多晶硅栅极上沉积一层硅化物层,可以降低接触电阻,最早发展起来的是WSi2,后来在0.25um以上IC中主要使用TiSi2,在0.25um-65/45nm制程中使用CoSi2替代TiSi2,在65/45-14nm和14nm以下制程中分别用NiSi和低温Ti-Si作为硅化物层;2)中段工艺:包括金属前电介质层(PMD)、阻挡层、接触孔等。中段工艺主要作用是连接前段器件与后段第一层金属,主要壁垒在于对接触孔钨栓塞的刻蚀和沉积。①PMD:使用TEOS-SiO2、PSG/BPSG等填充。用CVD方法沉积一层PMD,防止前后段工艺间杂质相互扩散;②阻挡层和接触孔:使用Ti/TiN等作为阻挡层,使用钨填充接触孔。先刻蚀出接触孔的形状,为了防止刻蚀过程中对接触孔底层材料的损伤,需要在介质层中加入Ti/TiN等作为阻挡层;最后生长钨填充接触孔,钨栓塞的形成是实现前段后段导通的最关键步骤,形成质量较差会导致互连电阻增大,影响器件性能,所以关键是刻蚀的高选择比(保证刻蚀完而不损伤下层材料)和薄膜沉积的上下均匀性,防止由于上层沉积速率比下层快而形成孔洞。 3、逻辑/存储芯片由多重模块堆叠,模块复杂性构筑薄膜沉积工艺技术高壁垒芯片工艺分为前道制造和后道封装两个部分,其中前道制造工艺又分为前、中、后三段工艺,前段和后段工艺分别形成晶体管等器件和金属布线,中段工艺用于将二者连接。1)前段工艺(Front end of line,FEOL):形成芯片底层晶体管等有源MOS器件的过程,主要包括浅槽隔离、源漏极、栅极、侧墙等。在其中,薄膜沉积的主要壁垒在于实现浅槽隔离中薄膜的填充和栅氧化层的厚度减薄等。①浅槽隔离(STI):使用薄膜主要为SiO2,薄膜沉积的壁垒在于填充过程中不会在沟道内部残留孔隙。STI目的是在Si衬底上划分出制备晶体管的区域,保证不同晶体管工作过程中不会相互干扰。STI的角度和深度不同对器件特性造成很大影响,同时随着制程进步,要求沟槽深宽比逐渐增大,因此要求刻蚀能够精准控制沟道深度,也需要保证沉积之后被填充的沟道内部不会残留孔隙而影响隔离效果。另外,由于沟槽区域尺寸差异较大,对CMP工艺也有所挑战;②源漏沟道工艺:使用非晶硅/锗硅填充沟道区,使用TEOS-SiO2和Si3N4等形成侧墙。沟道工艺是IC的核心工艺之一,确定了晶体管的基本性质,主要工艺是在离子注入形成源极/漏极;在1980s,为了改善短沟道效应(沟道缩小引起的载流子速度饱和,器件性能减弱)而引入侧墙,需要在栅极侧面形成并靠近源漏,防止源漏区的离子对栅极造成污染,关键在于对侧墙厚度精确控制,同时要求侧墙保持较好的隔离效果;对于40nm以下的工艺,通过外延法制备α-Si/SiGe可以对沟道区施加应力,可以提高MOSFET的开关速度;③栅极工艺:集成电路工艺中最关键的步骤,直接影响IC性能,主要用多晶硅/金属作为栅极,用SiO2、SiON、高k介质(HFO2、HfSiOx、HfSiON等)作为栅氧化层,其中薄膜沉积的壁垒在于保证栅氧化层尽可能薄。栅极制作中需要用到最先进的光刻、刻蚀与薄膜沉积工艺及设备,一般在45nm以上制程中,使用氧化方法制备SiO2作为栅氧化层,在栅氧化层上通过CVD方法沉积多晶硅并经过刻蚀形成多晶硅栅;制程进步要求栅氧化层不断减薄来维持栅电容,但在45nm以下制程之后,栅氧化层厚度低于1.5nm,器件漏电流大幅增加,不得不选用介电常数更高的高k介质替代传统SiO2作为栅氧化层,相当于在维持同样栅电容同时增加了等效栅氧化层厚度,同时,由于金属/金属化合物可以降低电阻率等,避免多晶硅栅的耗尽效应,在45nm制程之后逐渐替代多晶硅作为栅极;④硅化物层:使用WSi2、TiSi2、CoSi2、NiSi等。在源漏沟道区或者多晶硅栅极上沉积一层硅化物层,可以降低接触电阻,最早发展起来的是WSi2,后来在0.25um以上IC中主要使用TiSi2,在0.25um-65/45nm制程中使用CoSi2替代TiSi2,在65/45-14nm和14nm以下制程中分别用NiSi和低温Ti-Si作为硅化物层;2)中段工艺:包括金属前电介质层(PMD)、阻挡层、接触孔等。中段工艺主要作用是连接前段器件与后段第一层金属,主要壁垒在于对接触孔钨栓塞的刻蚀和沉积。①PMD:使用TEOS-SiO2、PSG/BPSG等填充。用CVD方法沉积一层PMD,防止前后段工艺间杂质相互扩散;②阻挡层和接触孔:使用Ti/TiN等作为阻挡层,使用钨填充接触孔。先刻蚀出接触孔的形状,为了防止刻蚀过程中对接触孔底层材料的损伤,需要在介质层中加入Ti/TiN等作为阻挡层;最后生长钨填充接触孔,钨栓塞的形成是实现前段后段导通的最关键步骤,形成质量较差会导致互连电阻增大,影响器件性能,所以关键是刻蚀的高选择比(保证刻蚀完而不损伤下层材料)和薄膜沉积的上下均匀性,防止由于上层沉积速率比下层快而形成孔洞。 3)后段工艺(Back end of line,BEOL):主要壁垒在于保证层间介质、钝化层等薄膜的致密性、均匀性等。后段工艺指形成能将电信号传输到芯片各个器件的互联线,包括金属间介质层沉积、金属线条形成、引出焊盘等工艺,按照功能不同,分类如下:①金属间介质层(IMD)/阻挡层/钝化层等:一般用SiO2及低k介质制作IMD,使用Ti/TiN/TaN/Ta等作为阻挡层,使用Si3N4等作为阻挡层,要求沉积的薄膜致密性好,隔离能力强。IMD/阻挡层薄膜主要防止不同金属层或者导线与介质层之间杂质的相互扩散,钝化层用来防止最后一层金属在封测过程中受到污染,因此要求薄膜的致密性好,隔离和绝缘能力强,其中阻挡层还要求厚度很薄(8nm)并且与铜和介质材料的粘附性都很好;②金属籽晶层与金属层:使用W/Al/Cu作为籽晶层,Al/Cu作为金属布线,要求沉积的导线电阻率低、导电能力强。在创建金属互连层过程中,沉积扩散阻挡层是第一步,用于防止层间介质层的金属污染;电镀方法沉积的金属较PVD法具有更低的电阻率和更好的填充特性,因此一般用电镀沉积后段金属层,但是电镀不能在高电阻的阻挡层上面成核,需要先使用PVD方法在阻挡层上沉积的一层W/Cu,用作电镀Cu等金属前的种子层;最后采用电镀方法在籽晶层上面填充Al/Cu等金属核,起到金属互连的作用;③硬掩膜(Hardmask):使用SiO2、Si3N4、TiN、非晶碳(ACHM)等,主要用于多重曝光工艺等。在制程进步到90nm以下时,光刻尺寸越来越小,需要在晶圆表面形成硬掩膜层配合光刻胶形成掩膜图形,之后通过刻蚀将其去除。传统的硬掩膜层为SiO2、Si3N4等,硬度比较有限,逐渐被金属硬掩膜例如TiN、掺杂碳的非晶硅(ACHM)等替代;④焊盘(pad):主要使用Al/Cu/合金,要求沉积的薄膜硬度足够高。焊盘位于钝化层的上方,用于将芯片中最后一层金属层和PCB板键合起来。焊盘一般为Al/Cu/合金衬垫(pad),需要承受住检测或者键合带来的机械压力。 3)后段工艺(Back end of line,BEOL):主要壁垒在于保证层间介质、钝化层等薄膜的致密性、均匀性等。后段工艺指形成能将电信号传输到芯片各个器件的互联线,包括金属间介质层沉积、金属线条形成、引出焊盘等工艺,按照功能不同,分类如下:①金属间介质层(IMD)/阻挡层/钝化层等:一般用SiO2及低k介质制作IMD,使用Ti/TiN/TaN/Ta等作为阻挡层,使用Si3N4等作为阻挡层,要求沉积的薄膜致密性好,隔离能力强。IMD/阻挡层薄膜主要防止不同金属层或者导线与介质层之间杂质的相互扩散,钝化层用来防止最后一层金属在封测过程中受到污染,因此要求薄膜的致密性好,隔离和绝缘能力强,其中阻挡层还要求厚度很薄(8nm)并且与铜和介质材料的粘附性都很好;②金属籽晶层与金属层:使用W/Al/Cu作为籽晶层,Al/Cu作为金属布线,要求沉积的导线电阻率低、导电能力强。在创建金属互连层过程中,沉积扩散阻挡层是第一步,用于防止层间介质层的金属污染;电镀方法沉积的金属较PVD法具有更低的电阻率和更好的填充特性,因此一般用电镀沉积后段金属层,但是电镀不能在高电阻的阻挡层上面成核,需要先使用PVD方法在阻挡层上沉积的一层W/Cu,用作电镀Cu等金属前的种子层;最后采用电镀方法在籽晶层上面填充Al/Cu等金属核,起到金属互连的作用;③硬掩膜(Hardmask):使用SiO2、Si3N4、TiN、非晶碳(ACHM)等,主要用于多重曝光工艺等。在制程进步到90nm以下时,光刻尺寸越来越小,需要在晶圆表面形成硬掩膜层配合光刻胶形成掩膜图形,之后通过刻蚀将其去除。传统的硬掩膜层为SiO2、Si3N4等,硬度比较有限,逐渐被金属硬掩膜例如TiN、掺杂碳的非晶硅(ACHM)等替代;④焊盘(pad):主要使用Al/Cu/合金,要求沉积的薄膜硬度足够高。焊盘位于钝化层的上方,用于将芯片中最后一层金属层和PCB板键合起来。焊盘一般为Al/Cu/合金衬垫(pad),需要承受住检测或者键合带来的机械压力。  在3D NAND中,底层采用氧化物-氮化物重复堆叠形成ON Stack,薄膜壁垒较高,要求厚度和组分均匀,沟道-介质界面缺陷密度低。在20nm工艺节点之后,传统的平面浮栅NAND因受到邻近浮栅-浮栅的耦合电容干扰而达到微缩的极限,为了实现更高的存储容量,NAND工艺开始向三维堆叠方向发展。在3D NAND FEOL工艺中,在完成CMOS的源漏极之后,开始重复沉淀多层氧化硅/氮化硅形成ON叠层(ON Stack),接下来进行光刻和沟道超深孔刻蚀(深宽比至少大于30:1),沉淀高质量的多晶硅薄膜和沟道深孔填充并形成栅衬垫阵列(Gate Pad),然后进行一系列的光刻、刻蚀、离子注入、沉积栅介质层、沉积栅极等工艺,最后进行BEOL工艺。 在3D NAND中,底层采用氧化物-氮化物重复堆叠形成ON Stack,薄膜壁垒较高,要求厚度和组分均匀,沟道-介质界面缺陷密度低。在20nm工艺节点之后,传统的平面浮栅NAND因受到邻近浮栅-浮栅的耦合电容干扰而达到微缩的极限,为了实现更高的存储容量,NAND工艺开始向三维堆叠方向发展。在3D NAND FEOL工艺中,在完成CMOS的源漏极之后,开始重复沉淀多层氧化硅/氮化硅形成ON叠层(ON Stack),接下来进行光刻和沟道超深孔刻蚀(深宽比至少大于30:1),沉淀高质量的多晶硅薄膜和沟道深孔填充并形成栅衬垫阵列(Gate Pad),然后进行一系列的光刻、刻蚀、离子注入、沉积栅介质层、沉积栅极等工艺,最后进行BEOL工艺。 在DRAM中,槽式/堆叠存储单元(Cell capacitor)向高深宽比发展,提高沉积难度。当前DRAM每个存储单元为1T1C(1 Transistor+1 Capacitor)结构,即由1个晶体管和1个电容构成,按照电容在晶体管之前和之后形成(即电容分别位于晶体管的下方和上方)可分为堆叠式电容(Stacked Capacitor)和沟槽式电容(Trench Capacitor)。1)沟槽式DRAM:先在基板上刻蚀出沟槽,然后在沟槽中沉积出介电层以形成电容器,然后在电容器上方制造出栅极,构成完整的DRAM cell。由于沟槽式DRAM不会影响CMOS晶体管特性,因此适合将DRAM和逻辑电路集成在一起,形成eDRAM。在沉积工艺时,由于沟槽的开口越来越细,要在沟槽里面沉积足够的介电材料,形成容值足够高的电容也更难;2)堆叠式DRAM:存储单元在前段工艺(FEOL)之后形成,主要用于制造独立式的高密度DRAM。电容结构逐渐从圆柱形变为柱形,需要对高深宽比进行构图,同样提高了沉积难度。 在DRAM中,槽式/堆叠存储单元(Cell capacitor)向高深宽比发展,提高沉积难度。当前DRAM每个存储单元为1T1C(1 Transistor+1 Capacitor)结构,即由1个晶体管和1个电容构成,按照电容在晶体管之前和之后形成(即电容分别位于晶体管的下方和上方)可分为堆叠式电容(Stacked Capacitor)和沟槽式电容(Trench Capacitor)。1)沟槽式DRAM:先在基板上刻蚀出沟槽,然后在沟槽中沉积出介电层以形成电容器,然后在电容器上方制造出栅极,构成完整的DRAM cell。由于沟槽式DRAM不会影响CMOS晶体管特性,因此适合将DRAM和逻辑电路集成在一起,形成eDRAM。在沉积工艺时,由于沟槽的开口越来越细,要在沟槽里面沉积足够的介电材料,形成容值足够高的电容也更难;2)堆叠式DRAM:存储单元在前段工艺(FEOL)之后形成,主要用于制造独立式的高密度DRAM。电容结构逐渐从圆柱形变为柱形,需要对高深宽比进行构图,同样提高了沉积难度。  4、沉积设备注重工艺稳定性以保证膜质性能,未来向低温、更高集成度方向发展评价薄膜性能指标包括均匀度、厚度、台阶覆盖率、成膜速率等,同时还要考虑反射率、颗粒情况等。1)良好的台阶覆盖能力。台阶覆盖能力指在硅片表面各个方向上厚度一致,实际工艺中,容易在尖角处以及沿着垂直侧壁到底部的方向出现厚度不均的情况,造成台阶底部断裂;2)填充高深宽比间隙的能力。深宽比被定义为间隙的深度和宽度的比值,典型的高深宽比是金属层之间介质中的通孔,难于形成厚度均匀的膜,并且容易产生夹断和空洞,降低芯片可靠性和良率;3)良好的厚度均匀性。要求硅片表面各处薄膜厚度一致,材料的电阻会随薄膜厚度的变化而变化,但是膜层越薄,膜本身机械强度降低等;4)高纯度和高密度。需要避免沾污物和颗粒,要求洁净的薄膜沉积过程和高纯度的材料;膜密度表示膜层中针孔和空洞的密度,反映薄膜致密性;5)高度的结构完整性和低的膜应力。沉积中要控制晶粒的尺寸,同时确保沉积的薄膜较薄,防止薄膜间的应力导致硅片衬底变形、开裂、分层等;6)对衬底材料或者下层薄膜保持良好的粘附性。粘附性为了避免薄膜分层和开裂,防止因开裂导致杂质的进入。粘附性主要由表面洁净程度、薄膜及合金的材料等决定。 4、沉积设备注重工艺稳定性以保证膜质性能,未来向低温、更高集成度方向发展评价薄膜性能指标包括均匀度、厚度、台阶覆盖率、成膜速率等,同时还要考虑反射率、颗粒情况等。1)良好的台阶覆盖能力。台阶覆盖能力指在硅片表面各个方向上厚度一致,实际工艺中,容易在尖角处以及沿着垂直侧壁到底部的方向出现厚度不均的情况,造成台阶底部断裂;2)填充高深宽比间隙的能力。深宽比被定义为间隙的深度和宽度的比值,典型的高深宽比是金属层之间介质中的通孔,难于形成厚度均匀的膜,并且容易产生夹断和空洞,降低芯片可靠性和良率;3)良好的厚度均匀性。要求硅片表面各处薄膜厚度一致,材料的电阻会随薄膜厚度的变化而变化,但是膜层越薄,膜本身机械强度降低等;4)高纯度和高密度。需要避免沾污物和颗粒,要求洁净的薄膜沉积过程和高纯度的材料;膜密度表示膜层中针孔和空洞的密度,反映薄膜致密性;5)高度的结构完整性和低的膜应力。沉积中要控制晶粒的尺寸,同时确保沉积的薄膜较薄,防止薄膜间的应力导致硅片衬底变形、开裂、分层等;6)对衬底材料或者下层薄膜保持良好的粘附性。粘附性为了避免薄膜分层和开裂,防止因开裂导致杂质的进入。粘附性主要由表面洁净程度、薄膜及合金的材料等决定。  设备更多考虑工艺稳定性,未来发展趋势是低温反应、高集成度等。①工艺稳定性:评价薄膜性能除了均匀度、厚度、台阶覆盖率、成膜速率等之外,还要考虑反射率、颗粒情况等。薄膜沉积设备首先要关注工艺稳定性,要保证设备在同一高水准下生产,同时设备开机率保持高位,例如AMAT等海外巨头的CVD设备开机率高达90%以上(即工作寿命内一年仅有10%的时间停机检修),同时在各个腔体间的匹配度保持一致;对于国内设备厂商来说,由于国内产线大多仍使用海外设备,因此国内设备厂在还要考虑各个维度上和国际设备厂商设备进行匹配,才能达到量产的标准;②未来薄膜设备趋向于低温反应与更高集成度:薄膜越来越严格的热预算限制要求更低温的薄膜生长工艺;同时,为了更好控制不同薄膜的生长,设备平台的系统集成度会更高,例如金属互连层的制备需要将不同的工艺腔室集成在一个平台上,对设备平台自动化控制等提出更高要求,例如通过多反应腔室沉积不同材料,通过冷却腔冷却加工后的硅片,实现不同薄膜的连续沉积;三维器件结构要求薄膜具备更好的台阶覆盖率、更强的沟槽填充能力和更精确的膜厚度控制等。 设备更多考虑工艺稳定性,未来发展趋势是低温反应、高集成度等。①工艺稳定性:评价薄膜性能除了均匀度、厚度、台阶覆盖率、成膜速率等之外,还要考虑反射率、颗粒情况等。薄膜沉积设备首先要关注工艺稳定性,要保证设备在同一高水准下生产,同时设备开机率保持高位,例如AMAT等海外巨头的CVD设备开机率高达90%以上(即工作寿命内一年仅有10%的时间停机检修),同时在各个腔体间的匹配度保持一致;对于国内设备厂商来说,由于国内产线大多仍使用海外设备,因此国内设备厂在还要考虑各个维度上和国际设备厂商设备进行匹配,才能达到量产的标准;②未来薄膜设备趋向于低温反应与更高集成度:薄膜越来越严格的热预算限制要求更低温的薄膜生长工艺;同时,为了更好控制不同薄膜的生长,设备平台的系统集成度会更高,例如金属互连层的制备需要将不同的工艺腔室集成在一个平台上,对设备平台自动化控制等提出更高要求,例如通过多反应腔室沉积不同材料,通过冷却腔冷却加工后的硅片,实现不同薄膜的连续沉积;三维器件结构要求薄膜具备更好的台阶覆盖率、更强的沟槽填充能力和更精确的膜厚度控制等。 二、物理与化学沉积设备相互补充,薄膜沉积设备细分品类不断迭代薄膜的制备需要不同技术原理,因此导致薄膜沉积设备也需要不同技术原理,物理/化学等不同沉积方法相互补充。薄膜沉积工艺主要分为物理和化学方法两类,1)物理方法:指利用热蒸发或受到粒子轰击时物质表面原子的溅射等物理过程,实现物质原子从源物质到衬底材料表面的物质转移。物理方法包括物理气相沉积(Physical Vapor Deposition,PVD)、旋涂、电镀(Electrondeposition/Electroplating,ECD/ECP)等,其中PVD又分为真空蒸镀、溅射两大方法;2)化学方法:把含有构成薄膜元素的气态反应剂或液态反应剂的蒸汽,以合理的气流引入工艺腔室,在衬底表面发生化学反应并在衬底表面上沉积薄膜。化学方法包括化学气相沉积(Chemical Vapor Deposition,CVD)和外延(Epitaxy,EPI)等,CVD按照反应条件(压强、温度、反应源等)不同又可分为常压CVD(APCVD)、低压CVD(LPCVD)、等离子增强CVD(PECVD)、次常压CVD(SACVD)、高密度等离子体CVD(HDP-CVD)、流体CVD(FCVD)、原子层沉积(ALD)、外延等。物理和化学方法相互补充,物理方法主要用于沉积金属导线及金属化合物薄膜等,而一般的物理方法无法实现绝缘材料的转移,需要化学方法通过不同气体间的反应来沉积,另外部分化学方法也可以用来沉积金属薄膜。 二、物理与化学沉积设备相互补充,薄膜沉积设备细分品类不断迭代薄膜的制备需要不同技术原理,因此导致薄膜沉积设备也需要不同技术原理,物理/化学等不同沉积方法相互补充。薄膜沉积工艺主要分为物理和化学方法两类,1)物理方法:指利用热蒸发或受到粒子轰击时物质表面原子的溅射等物理过程,实现物质原子从源物质到衬底材料表面的物质转移。物理方法包括物理气相沉积(Physical Vapor Deposition,PVD)、旋涂、电镀(Electrondeposition/Electroplating,ECD/ECP)等,其中PVD又分为真空蒸镀、溅射两大方法;2)化学方法:把含有构成薄膜元素的气态反应剂或液态反应剂的蒸汽,以合理的气流引入工艺腔室,在衬底表面发生化学反应并在衬底表面上沉积薄膜。化学方法包括化学气相沉积(Chemical Vapor Deposition,CVD)和外延(Epitaxy,EPI)等,CVD按照反应条件(压强、温度、反应源等)不同又可分为常压CVD(APCVD)、低压CVD(LPCVD)、等离子增强CVD(PECVD)、次常压CVD(SACVD)、高密度等离子体CVD(HDP-CVD)、流体CVD(FCVD)、原子层沉积(ALD)、外延等。物理和化学方法相互补充,物理方法主要用于沉积金属导线及金属化合物薄膜等,而一般的物理方法无法实现绝缘材料的转移,需要化学方法通过不同气体间的反应来沉积,另外部分化学方法也可以用来沉积金属薄膜。  1、物理气相沉积设备:主要沉积金属等薄膜,用于籽晶层、阻挡层、硬掩膜、焊盘等PVD主要用来沉积金属及金属化合物薄膜,最主要用于金属互连籽晶层、阻挡层、硬掩膜、焊盘等。普通真空蒸镀和直流溅射方法只能沉积金属或导电薄膜,而不适用制备绝缘体薄膜,原因在于当正离子轰击绝缘体靶材表面时,会把动能传递给靶面,但正离子本身却留在了靶材表面聚集,这些正离子产生的电荷产生的电场会对射向靶材表面的离子产生排斥,从而迫使溅射过程停止。一些高频溅射,例如射频溅射,也可以实现溅射绝缘材料。评价PVD工艺的主要参数包括尘埃数量,以及形成薄膜的电阻值、均匀性、反射率、厚度和应力等。PVD分为蒸镀和溅射两大类,初期真空蒸镀占据主流,后来由于不能蒸发一些难熔金属和氧化物材料,因此逐步被溅射取代,同时由于薄膜性能要求等不断升高,溅射PVD不断改进或迭代,目前应用最广泛的是磁控溅射PVD。真空蒸镀和溅射方法分别采用热蒸发或受到粒子轰击时物质表面原子的溅射等物理过程,实现物质原子从源物质到衬底材料表面的物质转移,这一过程不涉及化学反应。磁控PVD按照激励源及溅射方式的不同也分为直流溅射DCPVD、射频溅射RFPVD、磁控溅射PVD、离子化PVD等。 1、物理气相沉积设备:主要沉积金属等薄膜,用于籽晶层、阻挡层、硬掩膜、焊盘等PVD主要用来沉积金属及金属化合物薄膜,最主要用于金属互连籽晶层、阻挡层、硬掩膜、焊盘等。普通真空蒸镀和直流溅射方法只能沉积金属或导电薄膜,而不适用制备绝缘体薄膜,原因在于当正离子轰击绝缘体靶材表面时,会把动能传递给靶面,但正离子本身却留在了靶材表面聚集,这些正离子产生的电荷产生的电场会对射向靶材表面的离子产生排斥,从而迫使溅射过程停止。一些高频溅射,例如射频溅射,也可以实现溅射绝缘材料。评价PVD工艺的主要参数包括尘埃数量,以及形成薄膜的电阻值、均匀性、反射率、厚度和应力等。PVD分为蒸镀和溅射两大类,初期真空蒸镀占据主流,后来由于不能蒸发一些难熔金属和氧化物材料,因此逐步被溅射取代,同时由于薄膜性能要求等不断升高,溅射PVD不断改进或迭代,目前应用最广泛的是磁控溅射PVD。真空蒸镀和溅射方法分别采用热蒸发或受到粒子轰击时物质表面原子的溅射等物理过程,实现物质原子从源物质到衬底材料表面的物质转移,这一过程不涉及化学反应。磁控PVD按照激励源及溅射方式的不同也分为直流溅射DCPVD、射频溅射RFPVD、磁控溅射PVD、离子化PVD等。 1)真空蒸镀(Vacuum Evaporator)工艺真空蒸镀是最早用于金属薄膜制造的主流工艺,技术应用距今超100年历史,一般用于中小规模半导体集成电路。真空蒸镀原理是对金属材料进行加热使之沸腾后蒸发并沉积到硅片表面。该方法优点在于工艺简单、操作容易,所以制备的薄膜纯度较高,生长机理简单,但是形成的薄膜台阶覆盖率和粘附能力都较差,所以热蒸发法只限于早期的中小规模集成电路制造。 1)真空蒸镀(Vacuum Evaporator)工艺真空蒸镀是最早用于金属薄膜制造的主流工艺,技术应用距今超100年历史,一般用于中小规模半导体集成电路。真空蒸镀原理是对金属材料进行加热使之沸腾后蒸发并沉积到硅片表面。该方法优点在于工艺简单、操作容易,所以制备的薄膜纯度较高,生长机理简单,但是形成的薄膜台阶覆盖率和粘附能力都较差,所以热蒸发法只限于早期的中小规模集成电路制造。 针对真空蒸镀方法改进的电子束蒸镀可以实现超大规模集成电路(ULSI)上的金属薄膜等沉积。电子束蒸镀工艺的优点是蒸发速度快、无污染、可精确控制膜厚等,可以实现ULSI上的金属薄膜沉积,但是在ULSI工艺中的通孔、接触孔等,使用电子束蒸发无法进行孔内的金属覆盖。2)溅射工艺①直流溅射DCPVD:靶材只能是导体,主要用于沉积金属栅。DCPVD是利用电场加速带电离子,使离子和靶材表面原子碰撞,将后者溅射出来射向衬底,从而实现薄膜的沉积。使用DCPVD溅射绝缘材料时会导致正电荷在靶材表面积累,靶材的负电性减弱直至消失,导致溅射终止,因此不适用绝缘材料沉积,解决该问题的办法是使用RFPVD或者CVD;另外,DCPVD启辉电压高,电子对衬底的轰击强,解决该问题的办法是使用磁控溅射PVD。②射频溅射RFPVD:适合各种金属和非金属材料。RFCVD采用射频电源作为激励源,轰击出的靶材原子动能较DCPVD更小,因此既可以沉积金属也可以沉积非金属材料,但由于台阶覆盖率能力不如CVD,一般多用CVD沉积绝缘材料;RFPVD在改变薄膜特性和控制粒子沉积对衬底损伤方面有独特优势,因此可以用来配合直流磁控PVD使用,来降低DCPVD对圆片上的器件的损伤。在实际应用中,RFPVD主要沉积金属栅或者配合磁控溅射PVD使用来降低器件损伤。AMAT的Endura AVENIR RFPVD集成了PVD和PECVD的功能,主要用于22nm以下的金属栅极和高k栅氧化层和接触硅化物,在金属栅极应用中,可以实现可控的高均匀度连续薄膜沉积( 针对真空蒸镀方法改进的电子束蒸镀可以实现超大规模集成电路(ULSI)上的金属薄膜等沉积。电子束蒸镀工艺的优点是蒸发速度快、无污染、可精确控制膜厚等,可以实现ULSI上的金属薄膜沉积,但是在ULSI工艺中的通孔、接触孔等,使用电子束蒸发无法进行孔内的金属覆盖。2)溅射工艺①直流溅射DCPVD:靶材只能是导体,主要用于沉积金属栅。DCPVD是利用电场加速带电离子,使离子和靶材表面原子碰撞,将后者溅射出来射向衬底,从而实现薄膜的沉积。使用DCPVD溅射绝缘材料时会导致正电荷在靶材表面积累,靶材的负电性减弱直至消失,导致溅射终止,因此不适用绝缘材料沉积,解决该问题的办法是使用RFPVD或者CVD;另外,DCPVD启辉电压高,电子对衬底的轰击强,解决该问题的办法是使用磁控溅射PVD。②射频溅射RFPVD:适合各种金属和非金属材料。RFCVD采用射频电源作为激励源,轰击出的靶材原子动能较DCPVD更小,因此既可以沉积金属也可以沉积非金属材料,但由于台阶覆盖率能力不如CVD,一般多用CVD沉积绝缘材料;RFPVD在改变薄膜特性和控制粒子沉积对衬底损伤方面有独特优势,因此可以用来配合直流磁控PVD使用,来降低DCPVD对圆片上的器件的损伤。在实际应用中,RFPVD主要沉积金属栅或者配合磁控溅射PVD使用来降低器件损伤。AMAT的Endura AVENIR RFPVD集成了PVD和PECVD的功能,主要用于22nm以下的金属栅极和高k栅氧化层和接触硅化物,在金属栅极应用中,可以实现可控的高均匀度连续薄膜沉积( |

【本文地址】

公司简介

联系我们