|

SMIC13工艺版图设计规则

术语: Width:宽度,最小边长度  Space:一个形状外部到另一个形状外部的距离 Space:一个形状外部到另一个形状外部的距离  Extension:外延,从外边缘到内边缘的距离 Extension:外延,从外边缘到内边缘的距离  Enclosure:外壳 Enclosure:外壳  overlap:重叠 overlap:重叠  length:长度 length:长度

规则描述

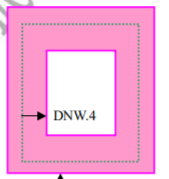

先写一些常用的 DNW区:Deep N-Well design minnima 1、最小宽度 3um 2、两个DNW之间最小space 6um 3、DNW和NW外壳最小距离 2um  4、NW和DNW重叠最小距离 2um 4、NW和DNW重叠最小距离 2um  5、NW和DNW之间最小space 4.1um AA区:Active Area design minima 1、AA宽度对于NMOS和PMOS来说最小是0.15um 2、AA用于相互连接最小宽度也是0.15um 3、两块AA间的最小距离0.21um 4、N+AA和NW外边沿之间距离最小0.23um 5、两块NW和N+AA的最小space0.3um 6、NW和其中的P+AA的enclosure最小0.3um 7、在PW里面的NW到P+AA的最小space 0.23um 8、AA的面积最小0.1um^2 9、DNW中的N+AA和NW到外沿最小距离0.4um 5、NW和DNW之间最小space 4.1um AA区:Active Area design minima 1、AA宽度对于NMOS和PMOS来说最小是0.15um 2、AA用于相互连接最小宽度也是0.15um 3、两块AA间的最小距离0.21um 4、N+AA和NW外边沿之间距离最小0.23um 5、两块NW和N+AA的最小space0.3um 6、NW和其中的P+AA的enclosure最小0.3um 7、在PW里面的NW到P+AA的最小space 0.23um 8、AA的面积最小0.1um^2 9、DNW中的N+AA和NW到外沿最小距离0.4um  NW:N-Well design minima 1、NW最小宽度0.6um 2、NW用于电阻最小宽度1.6um 3、两个1.2V NW之间距离(相同电势)0.6um 4、两个1.2V NW之间距离(不同电势)1um 6、1.2VNW和2.5/3.3VNW之间距离 1.2um 7a、2.5/3.3VNW之间距离(相同电势)0.6um 7b、2.5/3.3VNW之间距离(不同电势)1.2um 8、NW最小面积0.92um^2 NW:N-Well design minima 1、NW最小宽度0.6um 2、NW用于电阻最小宽度1.6um 3、两个1.2V NW之间距离(相同电势)0.6um 4、两个1.2V NW之间距离(不同电势)1um 6、1.2VNW和2.5/3.3VNW之间距离 1.2um 7a、2.5/3.3VNW之间距离(相同电势)0.6um 7b、2.5/3.3VNW之间距离(不同电势)1.2um 8、NW最小面积0.92um^2  GT:Poly design minima 1a、GT对于1.2V MOS的最小宽度 0.13um 1b、GT对于2.5V MOS的最小宽度 0.28um 1c、GT对于3.3V MOS的最小宽度 0.35/0.3um 2、用于连接的宽度0.13um 3、两个GT之间的宽度0.18um 4、场氧化物上AA与GT之间的space 0.07um 5、AA内GT与外沿最小距离 0.23um 6、GT内AA与外边沿最小距离 0.17um 7、GT的密度要达到15%(防止层无法用金属研磨均匀) 8、不允许在AA上弯曲GT。所有的GT模式在AA必须是 垂直于AA边。 9、NLL, NLH, SN, PLL,PLH, SP延伸在外的poly电阻 0.18um NLL, NLH, SN, PLL,PLH, SP的电阻外壳 10、NLL, NLH, SN和P型多晶硅电阻之间的space 0.18um PLL,PLH, SP到N型多晶硅电阻 11、GT由SN和/或SP封装 12、GT上不允许SN和SP重叠(确定单一掺杂,计算电阻) GT:Poly design minima 1a、GT对于1.2V MOS的最小宽度 0.13um 1b、GT对于2.5V MOS的最小宽度 0.28um 1c、GT对于3.3V MOS的最小宽度 0.35/0.3um 2、用于连接的宽度0.13um 3、两个GT之间的宽度0.18um 4、场氧化物上AA与GT之间的space 0.07um 5、AA内GT与外沿最小距离 0.23um 6、GT内AA与外边沿最小距离 0.17um 7、GT的密度要达到15%(防止层无法用金属研磨均匀) 8、不允许在AA上弯曲GT。所有的GT模式在AA必须是 垂直于AA边。 9、NLL, NLH, SN, PLL,PLH, SP延伸在外的poly电阻 0.18um NLL, NLH, SN, PLL,PLH, SP的电阻外壳 10、NLL, NLH, SN和P型多晶硅电阻之间的space 0.18um PLL,PLH, SP到N型多晶硅电阻 11、GT由SN和/或SP封装 12、GT上不允许SN和SP重叠(确定单一掺杂,计算电阻)  SN:N+S/D implantation design minima 1、SN最小宽度0.3um 2、两块SN之间的最小距离0.3um 3、SN和P+AA在NW之间的最小距离0.16um 4、SN和P+pick-up AA在PW之间的最小距离 0.03um 5、对于NMOS,SN在Poly硅外的距离0.4um 6、对于PMOS,SN在Poly硅外的距离0.4um 7、SN延伸到N+AA外,如果到相关的poly的距离大于0.25um 0.16um 8、SN延伸到N+AA外,如果到相关的poly的距离 小于0.25um 0.3um 9、N+AA在NW中距离SN外边沿距离 0.03um 10、SN和AA重叠 0.16um 11、SN最小面积0.23um SN:N+S/D implantation design minima 1、SN最小宽度0.3um 2、两块SN之间的最小距离0.3um 3、SN和P+AA在NW之间的最小距离0.16um 4、SN和P+pick-up AA在PW之间的最小距离 0.03um 5、对于NMOS,SN在Poly硅外的距离0.4um 6、对于PMOS,SN在Poly硅外的距离0.4um 7、SN延伸到N+AA外,如果到相关的poly的距离大于0.25um 0.16um 8、SN延伸到N+AA外,如果到相关的poly的距离 小于0.25um 0.3um 9、N+AA在NW中距离SN外边沿距离 0.03um 10、SN和AA重叠 0.16um 11、SN最小面积0.23um  SP:P+S/D implantation design minima 1、SP最小宽度0.3um 2、两块SP之间的最小距离0.3um 3、SP和N+AA在PW之间的最小距离0.16um 4、SP和N+AA在NW之间的最小距离 0.03um 5、SP和 N-channel Poly硅的最小距离0.4um 6、对于PMOS,SP在Poly硅外的距离0.4um 7、SP延伸到P+AA外,如果到相关的poly的距离大于0.25um 0.16um 8、SP延伸到P+AA外,如果到相关的poly的距离 小于0.25um 0.3um 9、P+AA在PW中距离SP外边沿距离 0.03um 10、SP和AA重叠 0.16um 11、SP最小面积0.23um 12、不允许SP和SN重叠 13、SN的反调不能产生SP SP:P+S/D implantation design minima 1、SP最小宽度0.3um 2、两块SP之间的最小距离0.3um 3、SP和N+AA在PW之间的最小距离0.16um 4、SP和N+AA在NW之间的最小距离 0.03um 5、SP和 N-channel Poly硅的最小距离0.4um 6、对于PMOS,SP在Poly硅外的距离0.4um 7、SP延伸到P+AA外,如果到相关的poly的距离大于0.25um 0.16um 8、SP延伸到P+AA外,如果到相关的poly的距离 小于0.25um 0.3um 9、P+AA在PW中距离SP外边沿距离 0.03um 10、SP和AA重叠 0.16um 11、SP最小面积0.23um 12、不允许SP和SN重叠 13、SN的反调不能产生SP  CT:Contact design minima 1、固定触点尺寸(方形孔边) 0.16um 2、两个CT之间距离 0.18um 3、AA和在Poly硅上的Contact最小距离 0.12um 4a、poly硅和AA上的Contact对于1.2V和2.5V 0.11um 4b、poly硅和AA上的Contact对于3.3V 0.13um 5、在AA上的Contact和AA外沿距离 0.06um 6、在Poly上的Contact和Poly外沿距离 0.06um 7、CT和M1的外沿距离 0um 8、M1线末端延伸至CT外 0.05um 9、CT不被允许放到Gate上(滑稽表情) 10、CT放在自对准多晶硅表面 CT:Contact design minima 1、固定触点尺寸(方形孔边) 0.16um 2、两个CT之间距离 0.18um 3、AA和在Poly硅上的Contact最小距离 0.12um 4a、poly硅和AA上的Contact对于1.2V和2.5V 0.11um 4b、poly硅和AA上的Contact对于3.3V 0.13um 5、在AA上的Contact和AA外沿距离 0.06um 6、在Poly上的Contact和Poly外沿距离 0.06um 7、CT和M1的外沿距离 0um 8、M1线末端延伸至CT外 0.05um 9、CT不被允许放到Gate上(滑稽表情) 10、CT放在自对准多晶硅表面  M1:Metal1 design minima 1、M1最小宽度 0.16um 2、两个M1之间的最小距离 0.17um 3a、如果两个M1之间有一个宽度大于0.4um的建议两者之间的距离为 0.2um 3b、如果两个M1之间有一个宽度大于2um的建议两者之间的距离为 0.4um 3c、如果两个M1之间有一个宽度大于10um的建议两者之间的距离为 0.5um 4、M1的最小面积 0.08um 5、由M1包围的电介质面积 0.17um 6、M1的金属面积最小16%,最大82% 7、金属线与宽度超过0.5um的45度金属线之间距离 0.2um 8、最大宽度14um M1:Metal1 design minima 1、M1最小宽度 0.16um 2、两个M1之间的最小距离 0.17um 3a、如果两个M1之间有一个宽度大于0.4um的建议两者之间的距离为 0.2um 3b、如果两个M1之间有一个宽度大于2um的建议两者之间的距离为 0.4um 3c、如果两个M1之间有一个宽度大于10um的建议两者之间的距离为 0.5um 4、M1的最小面积 0.08um 5、由M1包围的电介质面积 0.17um 6、M1的金属面积最小16%,最大82% 7、金属线与宽度超过0.5um的45度金属线之间距离 0.2um 8、最大宽度14um

|