| 极小尺寸扇出封装解决方案 : 长电科技 ECP技术(下篇) | 您所在的位置:网站首页 › 半导体WLCSP流程 › 极小尺寸扇出封装解决方案 : 长电科技 ECP技术(下篇) |

极小尺寸扇出封装解决方案 : 长电科技 ECP技术(下篇)

|

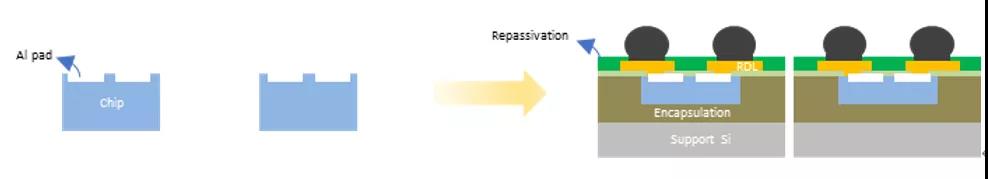

目前,由于5G通信,安全雷达,无人机等领域的迅猛发展,市场对于通信模块小型化、轻量化、高性能和低成本的需求日益增长,这为半导体制造商带来了复杂的技术和制造挑战。 先进封装技术在这股产业革新的趋势中正扮演着越来越重要的角色,也成为推动集成电路产业不断发展的关键所在。本篇文章我们就将为大家介绍长电科技的ECP封装的技术优势和应用范围。 长电科技先进的ECP封装可实现芯片的五面封装保护,有效地克服了晶圆曲翘问题,并实现小尺寸芯片、大扇出比扇出封装。可应用于集成封装,光屏蔽,机械保护及可靠性增强,小尺寸封装和多芯片封装等。 ECP封装技术优势 来料芯片减薄后划成单颗,通过芯片键合工艺将芯片面朝下置于贴双面胶膜的载体硅上,然后使用包覆膜对芯片进行包覆整平,此时已实现芯片的5面包覆。 紧接着需要在包覆膜背面键合支撑硅片,随后去掉载体硅片便得到重构晶圆。在重构晶圆上完成重新布线和金属凸块工艺后,通过磨划便得到最终封装体。在整个制造过程中,键合的硅片作为支撑体一直存在直至磨片,可以有选择地通过磨片来去掉支撑硅或者保留在封装体中。图1分别为来料芯片及最终实现扇出型ECP工艺封装体。

图1:扇出型ECP来料芯片(左)和最终封装体(右) ECP工艺最终可以实现200μm厚度而无需背露芯片的超薄型五面封装,而封装体背面键合支撑硅,也可以有效地提高封装体的弯曲强度和板上机械热循环可靠性。 运用该技术可以实现增强型WLCSP扇入封装,扇入型封装工艺可以实现最小封装尺寸解决方案,降低晶圆生产制造及测试成本,同时满足便携产品短小轻薄的特点,主要可应用于I/O接点数不多的工艺。侧壁及底部实现包覆膜保护,可以有效提高封装体对抗机械应力及外部环境变化。

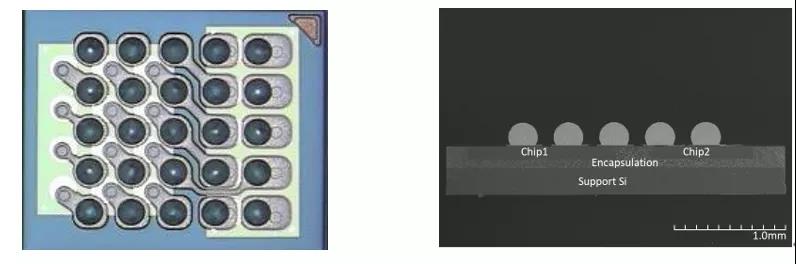

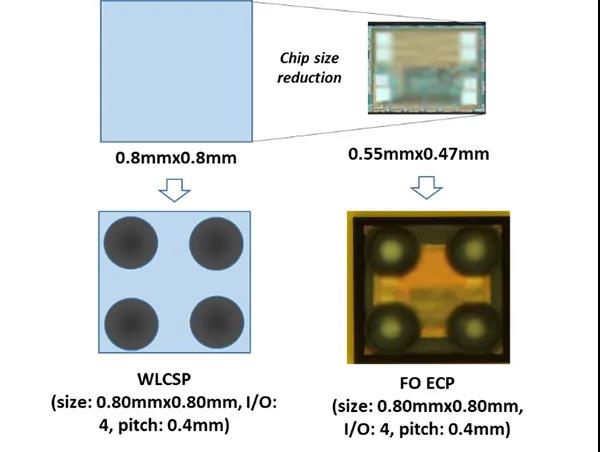

图2:扇出型ECP封装体 ECP封装应用范围 ECP技术主要实现在以下方面的应用,集成封装,光屏蔽,机械保护及可靠性增强,小尺寸封装和多芯片封装等。针对单芯片扇出型封装技术,可以降低 有效成本。 如图3所示,受限于I/O数量及引脚间距,采用WLCSP封装的芯片尺寸需0.8mm*0.8mm,但是通过扇出型ECP封装技术并在保持引脚数目和间距的要求下,可以将芯片尺寸设计降低至0.55mm*0.47mm,晶圆上的有效芯片数量便可达到一倍以上的提升。

图3:小尺寸WLCSP与扇出型封装对比 相比起WLCSP,ECP在该方面的应用可以有效地降低客户成本。而芯片周围的包覆膜材料起到了机械保护的作用,避免了WLCSP芯片因后续工艺操作转移而造成的碎裂风险,该尺寸也是扇出型ECP封装在小尺寸芯片封装的应用。 图4为采用扇出型ECP技术实现的射频模块封装体,通过将不同功能和数量的芯片集成在一个封装体内,在芯片的周围制作电路布线,实现芯片间的互连,进而制备具有系统功能的封装体。

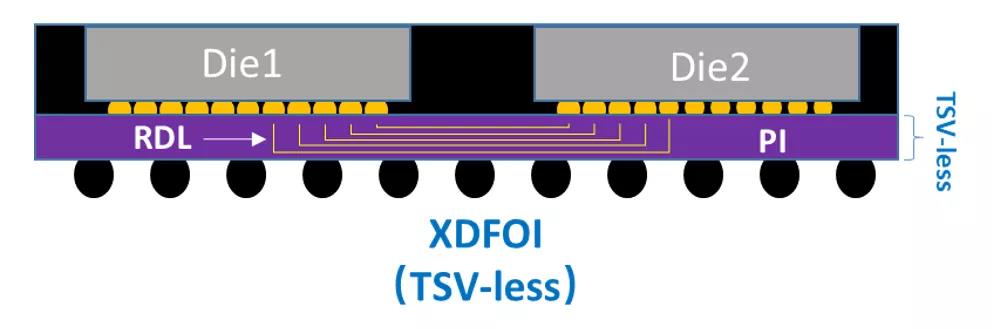

图4:多芯片扇出ECP封装体 继ECP封装技术,长电科技还深耕多维扇出集成技术XDFOITM(X-Dimensional Fan-out Integration, XDFOITM)。 XDFOI为一种以2.5D TSV-less为基本技术平台的封装技术,在线宽/线距可达到2um/2um的同时,还可以实现多层布线层、 2D,2.5D和3D多种异构封装。 相比2.5D TSV封装,具有更低的有效成本、更灵活的架构设计, 更好的性能、更佳的可靠性,是一种适用于FPGA、CPU、GPU、ASIC、APU、AI、网络通讯和5G互联芯片等高端产品,同时也提供小芯片(Chiplet)及异构封装 (HIP Heterogeneous Integration Package)的系统封装的解决方案。

图5: 多芯片XDFOITM封装体 展望未来,在芯片行业不断向精益化发展的过程中,长电科技也将继续研发新的技术,优化自己的产品,不断提升自身的创新能力和服务能力并促进整个行业的发展。 |

【本文地址】