| 【计算机组成原理】基础知识汇总(必背) | 您所在的位置:网站首页 › 医学基础知识简答题重点必背 › 【计算机组成原理】基础知识汇总(必背) |

【计算机组成原理】基础知识汇总(必背)

|

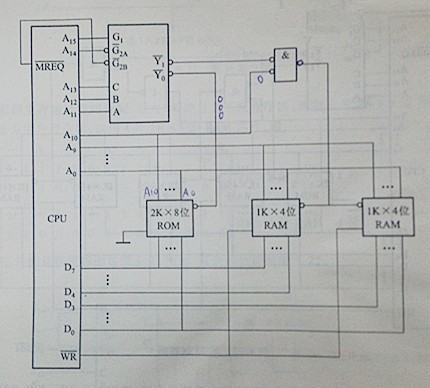

设CPU共有16根地址线,8根数据线,存储器与CPU的连线如下图所示:

8000H—87FFH 和 8800H—8BFFH 若使用汉明纠错码(Hamming Code)来确定512位数据字中单个错误,需要(10)位校验码。 主存贮器和CPU之间增加cache的目的是(解决CPU和主存之间的速度匹配问题)。 设有一个四体低位交叉存储器中,每个体的容量为256K×64位,总线传送周期为100ns,存取周期为400ns,四个存储体流水线工作,CPU连续读4个字所需的最多时间是(700ns)。 某计算机的cache共有16块,采用二路组相联映射方式(即每组2块)、每个主存块大小为32字节,按字节编址。主存129号单元所在主存块应该装入到cache的组号是(4)。 解:cache 一共 8 组,每组 2 块。主存按字节编址,129 号单元位于第 5 块上,该块编号为4(从 0 开始)(129 / 32 = 4)。主存块号 i 与 Cache 组号 j 映射关系为:j=i mod 8,所以 j=4 mod 8 = 4,即 129 号单元装入到第 5 组,组号为 4 。 存取周期是指(存储器进行连续读或写操作允许的最短间隔时间) 在程序的执行过程中,Cache与主存的地址映射是由(由硬件自动完成的)。 若主存每个存储单元为16位,则(其数据线是16根)。 下列有关RAM和ROM得叙述中正确的是(仅I和II)。 I RAM是易失性存储器,ROM是非易失性存储器 II RAM和ROM都是采用随机存取方式进行信息访问 III RAM和ROM都可用做Cache IV RAM和ROM都需要进行刷新 III:Cache 一般是 SRAM IV :动态RAM需要进行刷新 某SRAM芯片,存储容量为64K×16位,该芯片的地址线和数据线数目为(16,16)。 存储容量 = 2^地址线数 * 数据线位数 |

【本文地址】

请推测系统程序区和用户程序区的地址空间。

请推测系统程序区和用户程序区的地址空间。