| STA静态时序分析 | 您所在的位置:网站首页 › 分析和综合的关系是什么 › STA静态时序分析 |

STA静态时序分析

|

STA静态时序分析——学习笔记

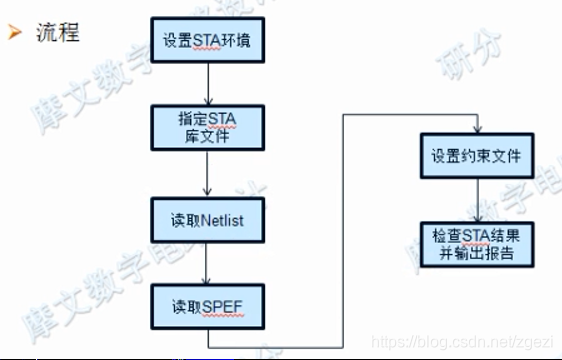

静态时序分析简介及基本知识PT流程以及分步骤讲解2.1 设计STA环境2.2 指定STA库文件2.3 读取Netlist文件2.4 读取SPEF文件2.5 设置约束文件2.6 输出报告并保存数据文件PT基础使用

PT其他使用PT实操输出文件和报告

静态时序分析简介及基本知识

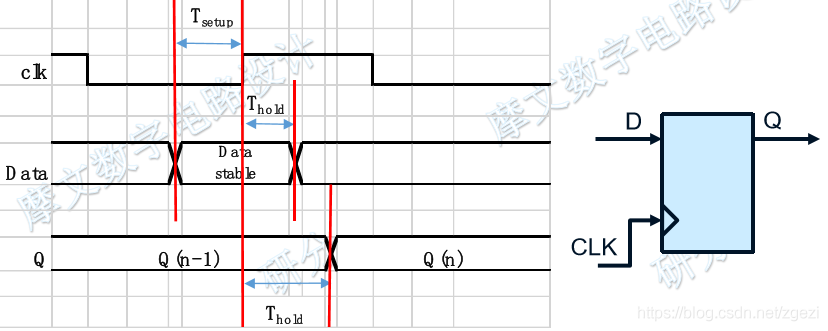

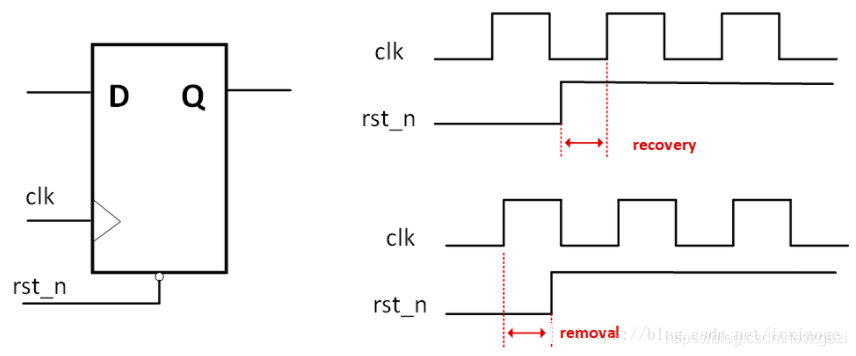

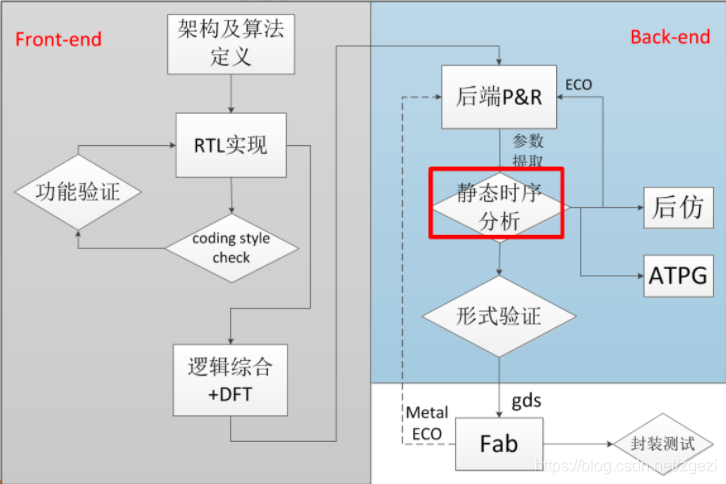

PT和综合的过程和命令都是十分相似的; !!与综合过程中对时序检查的区别:PT使用的是更加精准的时序模型,并且使用PT做STA会扫描所有的corner,而综合一般只做一两个corner 静态时序分析具有以下功能 STA可分析电路最高时钟频率;STA可检查设计在所有corner下均能时序收敛(综合通常只跑个别corner,但跑STA资源小速度快,可以遍历各种corner);分析时钟的偏移,不平衡等各种因素对电路时序的影响补充知识:PVT:Process、Voltage、tempreture Process:由于fab制造过程的工艺掺杂不均匀,分为ff, ss, tt等(电子、空穴掺杂不均匀);Voltage:芯片工作电压,由于电源的不稳定,以及后端的IR-drop(压降)等因素导致。(可分为0.9 * VDD, 1.1 * VDD);tempreture:芯片工作时的温度,一般分为-40,-10, 70 ,125几个温度;常用的工具 Synopsys: Prime Time(用的更多)Cadence: Tempus时序单元的相关约束 Setup time建立时间Tsetup:数据在时钟沿之前必须有效的时间;Hold time保持时间Thold:数据在时钟沿之后必须稳定的时间;recover time恢复时间:低电平复位信号或者高电平清零信号在时钟有效沿之前保持有效的最小时间长度;removal time移除时间:低电平复位信号或者高电平清零信号在时钟有效沿之后保持有效的最小时间长度;最小脉冲宽度:脉冲波形从开始到结束之间的最小时间间隔;

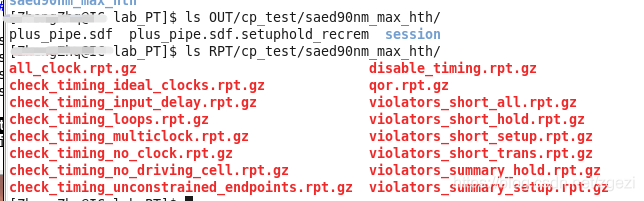

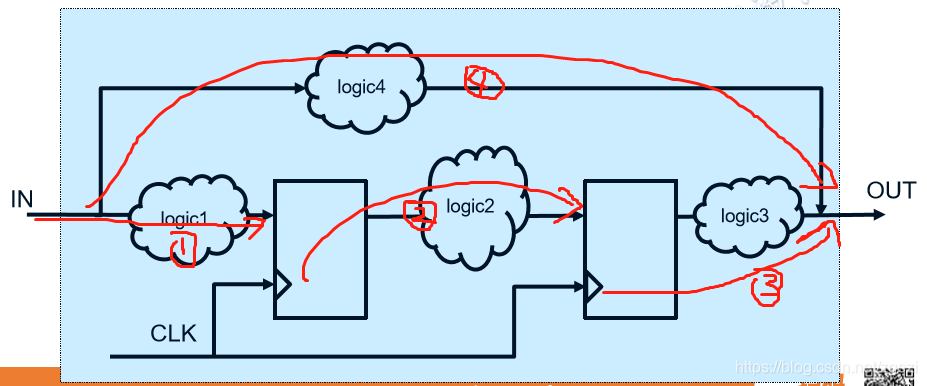

时序路径: 时序路径(timing path)指设计中数据信号传播过程中所经过的逻辑路径。每一条时序路径都存在与之对应的一个始发点和一个终止点。 始发点:组合逻辑输入端、时序单元输入端; 终止点:组合逻辑输出端、时序单元输入端; 这样就有4种时序路径的组合: 1、输入端到触发器; 2、触发器到触发器; 3、触发器到输出端; 4、出入端到输出端;(需要虚拟时钟??) 输出文件: 带延时的SDF文件(主要!!!,做后仿使用)各种报告以及保留结果的session文件;Timing eco文件(有时序违例时重复迭代此步(给后端进一步优化版图,修完后会重新给一个SDF文件和session文件)直到时序违例消除,) PT流程以及分步骤讲解

set_propagated_clock [all_clocks]设计成propagate后是一个实际的延时(实际的线网延时),这步是必不可少的。(没设置的话clock默认是理想的具有无穷大的驱动能力,时序就不准确) 时钟的创建,需要知道在哪一个端口创建时钟,以及时钟的频率,相位等。还要知道时钟之间的相互关系 设置内部transition约束,输入输出的延时控制,输入输出的驱动能力/负载; 设置时钟的不确定性。设置的值可以比DC时的小,因为skew和latency已经确定了。主要是预防jitter以及预留一些余量; 设置约束文件——OCV(on chip variation) 早期的工艺没有OCV,直接BC_WC(Bset_coner,Worst_coner)分别检查hol/setup时序;进入深压微米后,芯片内部不同位置的PVT情况不同,更差情况是同一条时序路径上launch path和capture path的PVT不同 假设date path(Launch path)处在WC,clock path(capture path)处在BC,有少量的偏差。通过引入OCV用derate来模拟实际的这种情况,并保留一定的余量,按一定的系数放大或者缩小,来模拟OCV的情况。比如Launtch的正常的延时是A,系数是0.95,则现在的延时是0.95A,Capture path正常的延时是B,系数是1.03则现在的延时是1.03B 一般有专门CAD team的人确定这个sign-off标准计算setup时,launch path * late(>1), capture path * early( read_parasitic -keep_capacitive_coupling $SPEF_FILE -verbose complete_net_parasitics report_annotated_parasitics -check -constant_arcs -list_not_annotated -max_nets 100000 } ############################################################### ###### 设置约束文件 ###### ############################################################### source -echo ./${SCRIPT_FILE}/read_constraints.tcl update_timing -full set_timing_derate -early [expr 1 - 0.05] set_timing_derate -late [expr 1 + 0.03] # write sdf write_sdf -context verilog -significant 4 $OUT_PATH/${WORKING_DESIGN}.sdf.setuphold_recrem -version 3.0 -include {SETUPHOLD RECREM} write_sdf -context verilog -significant 4 $OUT_PATH/${WORKING_DESIGN}.sdf -version 3.0 ######################### save session ################### if {$SAVE_SESSION == 1} { save_session $DATA_OUT/$CORNER/session set f [open "restore_session_${CORNER}.csh" w] puts $f "\ #!/bin/csh pt_shell -sgq normal:1c:4m -x \"restore_session $OUT_PATH/session\" " close $f exec chmod +x "restore_session_${CORNER}.csh" } ############################################### ############################################################### ###### 输出报告 ###### ############################################################### source -echo ./${SCRIPT_FILE}/report.tcl # get fanout number #sizeof_collection [get_pins -leaf -of [get_nets x_stdblk_rtl/inst_sif/ADDR1[1] ] -filter "direction==in" ]set_env.tcl: ### file :set_env.tcl set WORKING_DESIGN plus_pipe set SOURCE_FILE source_file set NETLIST ./${SOURCE_FILE}/${WORKING_DESIGN}.v set SPEF_FILE ./${SOURCE_FILE}/${WORKING_DESIGN}.spef set file_version cp_test set RPT_DIR RPT set OUT_DIR OUT ### 设置的控制变量 set SAVE_SESSION 1 set REPORT_GEN 1 set EXIST_SPEF 0 set RPT_OUT [format "%s%s" $RPT_DIR/ $file_version] set DATA_OUT [format "%s%s" $OUT_DIR/ $file_version] set REPORT_PATH [format "%s%s" $RPT_OUT/ $CORNER] set OUT_PATH [format "%s%s" $DATA_OUT/ $CORNER]file_create.tcl :创建目录结构 ### file : file_create.tcl if {[file exist $RPT_DIR]} { echo "File $RPT_DIR already exist" } else { exec mkdir $RPT_DIR echo "Creating $RPT_DIR !!!" } if {[file exist $RPT_DIR/$file_version]} { echo "File $file_version already exist" #exec rm $RPT_DIR/$file_version -r #exec mkdir $RPT_DIR/$file_version #echo "Re-create $file_version files" } else { exec mkdir $RPT_DIR/$file_version echo "Creating $file_version in $RPT_DIR !!!" } if {[file exist $RPT_DIR/$file_version/$CORNER]} { echo "File $file_version/$CORNER already exist" exec rm $RPT_DIR/$file_version/$CORNER -r exec mkdir $RPT_DIR/$file_version/$CORNER echo "Re-create $file_version files" } else { exec mkdir $RPT_DIR/$file_version/$CORNER echo "Creating $file_version/$CORNER in $RPT_DIR !!!" } if {[file exist $OUT_DIR]} { echo "File $OUT_DIR already exist" } else { exec mkdir $OUT_DIR echo "Creating $OUT_DIR !!!" } if {[file exist $OUT_DIR/$file_version]} { echo "File $file_version already exist" # exec rm $OUT_DIR/$file_version -r # exec mkdir $OUT_DIR/$file_version # echo "Re-create $file_version files" } else { exec mkdir $OUT_DIR/$file_version echo "Creating $file_version in $OUT_DIR !!!" } if {[file exist $OUT_DIR/$file_version/$CORNER]} { echo "File $file_version/$CORNER already exist" exec rm $OUT_DIR/$file_version/$CORNER -r exec mkdir $OUT_DIR/$file_version/$CORNER echo "Re-create $file_version files" } else { exec mkdir $OUT_DIR/$file_version/$CORNER echo "Creating $file_version/$CORNER in $OUT_DIR !!!" }执行以上内容得到新的目录结构 OUT:存放输出文件 RPT:存放报告 report.tcl puts "### reporting started" if {$REPORT_GEN == 1} { update_timing -full redirect -tee -compress -file $REPORT_PATH/all_clock.rpt.gz {report_clock -skew} #check multiple clocks pe$REPORT_PATH redirect -tee -compress -file $REPORT_PATH/check_timing_multiclock.rpt.gz {check_timing -over {data_check_multiple_clock}} #check no clocks redirect -tee -compress -file $REPORT_PATH/check_timing_no_clock.rpt.gz {check_timing -over {no_clock} -verbose} #check ideal clocks redirect -tee -compress -file $REPORT_PATH/check_timing_ideal_clocks.rpt.gz {check_timing -over {ideal_clocks} -verbose} #check input delay redirect -tee -compress -file $REPORT_PATH/check_timing_input_delay.rpt.gz {check_timing -over {no_input_delay partial_input_delay} -verbose} #check no driving cell redirect -tee -compress -file $REPORT_PATH/check_timing_no_driving_cell.rpt.gz {check_timing -over {no_driving_cell} -verbose} #check loops redirect -tee -compress -file $REPORT_PATH/check_timing_loops.rpt.gz {check_timing -over {loops} -verbose} #check unconstrained endpoints (clock-domain crossing may be included). redirect -tee -compress -file $REPORT_PATH/check_timing_unconstrained_endpoints.rpt.gz {check_timing -over {unconstrained_endpoints} -verbose} #check disbled timing arcs redirect -tee -compress -file $REPORT_PATH/disable_timing.rpt.gz {report_disable_timing -nosplit} #constraints violations redirect -tee -compress -file $REPORT_PATH/violators_short_all.rpt.gz {report_constraint -all_violators -nosplit} #setup timing redirect -tee -compress -file $REPORT_PATH/violators_short_setup.rpt.gz {report_constraint -all_violators -max_delay -nosplit -recovery} #hold timing redirect -tee -compress -file $REPORT_PATH/violators_short_hold.rpt.gz {report_constraint -all_violators -min_delay -nosplit -removal} #report_timing alias report_timing_summary report_timing -path summary -nosplit -slack_lesser_than 0.0 -max_paths 1000 redirect -tee -compress -file $REPORT_PATH/violators_summary_setup.rpt.gz {report_timing_summary -delay max} redirect -tee -compress -file $REPORT_PATH/violators_summary_hold.rpt.gz {report_timing_summary -delay min} #transition redirect -tee -compress -file $REPORT_PATH/violators_short_trans.rpt.gz {report_constraint -all_violators -max_transition -min_transition -nosplit} #qor puts "##### reporting qor #####" redirect -tee -compress -file $REPORT_PATH/qor.rpt.gz {report_qor} } 输出文件和报告

|

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |

静态时序分析(STA)是通过工具对同步电路中所有存在的时序路径进行分析,检查是否存在时序违例。是标准的timing sign-off(时序签字)的工具。

静态时序分析(STA)是通过工具对同步电路中所有存在的时序路径进行分析,检查是否存在时序违例。是标准的timing sign-off(时序签字)的工具。 PT的输入输出文件: 输入文件(【】表示非必须):

PT的输入输出文件: 输入文件(【】表示非必须): 过程可寻求帮助:

过程可寻求帮助:

read_constrains.tcl:

read_constrains.tcl: