| 数字电子时钟Multisim仿真设计 | 您所在的位置:网站首页 › 仿真电路软件multisim教程 › 数字电子时钟Multisim仿真设计 |

数字电子时钟Multisim仿真设计

|

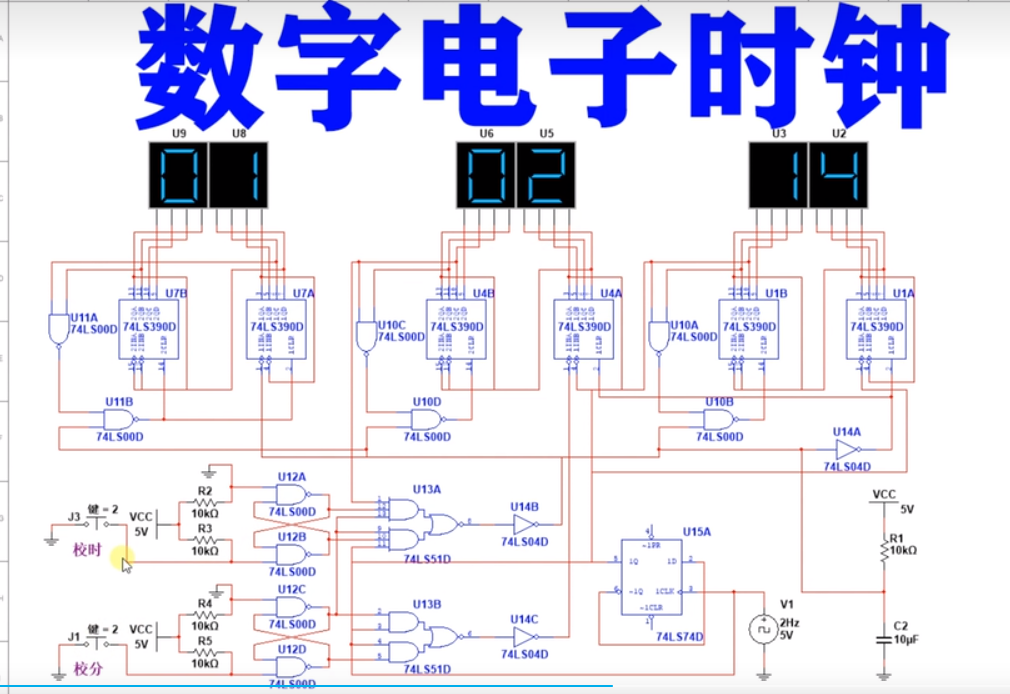

仿真图:

具有6个数码管用于显示系统的时、分、秒 采用6片计数器芯片74LS390分别驱动6个数码管 采用触发器74LS74和多个逻辑门配合可以实现分钟和小时的校准,校准方式是通过两个按键 采用标准的信号发生器作为系统芯片的时钟源 芯片介绍74LS390芯片的特点如下: 计数功能:74LS390可以进行两个独立的4位二进制计数,可以按照正向递增(上升计数)或反向递减(下降计数)的方式进行计数。同步操作:它采用同步逻辑,确保在时钟信号触发时进行计数,并且所有输出都在同一时刻更新。可调初值:该计数器具有可调节的初值设置功能,通过设置预置(preset)和清零(clear)输入引脚上的数据来指定开始计数的起始值。异步复位:74LS390具有异步复位功能,可以通过外部引脚接收复位信号,将计数器清零并恢复到初始状态。锁存功能:该芯片具有锁存功能,可以通过设置锁存使能(enable)引脚来冻结当前计数状态,并阻止进一步的计数。输入和输出缓冲器:该芯片配备了输入和输出缓冲器,提供对输入和输出信号的增强驱动和抗干扰能力。74LS74芯片的特点如下: 双D触发器:74LS74包含两个独立的D触发器,可以进行数据存储和时序控制操作。异步清零:该芯片具有异步复位功能,可以通过外部引脚接收清零信号,将触发器的状态清零并恢复到初始状态。同步操作:触发器采用同步逻辑,确保在时钟信号触发时进行数据存储,并根据触发器类型(上升沿触发或下降沿触发)更新输出。数据输入:每个触发器具有一个数据输入引脚(D),用于输入要存储的数据。时钟输入:每个触发器具有一个时钟输入引脚(CLK),用于控制数据存储的时机。输出:每个触发器都有一个输出引脚(Q),以提供已存储的数据作为输出。非反转输出:某些型号的74LS74还具有一个额外的非反转输出引脚(\Q),提供与输出引脚相反的数据。设计文件: 链接:https://pan.baidu.com/s/1hK4Q1ESQzdQiTUKZC9nlHw?pwd=yyle 提取码:yyle |

【本文地址】

公司简介

联系我们

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |