| 【沧小海笔记】之基于FPGA的以太网设计相关知识 | 您所在的位置:网站首页 › 以太网需要钱吗 › 【沧小海笔记】之基于FPGA的以太网设计相关知识 |

【沧小海笔记】之基于FPGA的以太网设计相关知识

|

总目录在这里哦~

https://blog.csdn.net/z123canghai/article/details/114649502 Xilinx为我们提供了一个叫做“Tri-Mode Ethernet MAC”的IP核,简称TEMAC核,三种模式的以太网介质访问控制层器,支持全双工半双工的千兆、百兆、十兆和2.5G的传输速率,支持MII、GMII、RGMII、SGMII和TBI接口。在PG051当中为我们进行了详细的介绍。但光看这文档效率太低,我们还是在应用种去理解吧。该模块可以是对协议的具体解析了,需要我们了解TCP/IP协议栈。 3.1 IP核的配置对于该核的配置相对来说还是比较简单的,如下: 1、data Rate

设置最大的通讯速率,1Gb/s支持高达1Gb/s的以太网速度。支持四种类型的物理接口,即GMII,MII,RGMII和内部接口均可用。2.5 Gb / s 指的是以太网速度设置为2.5Gb/s。物理接口设置为“内部”,所有其他类型均被禁用。所有默认即可

2、Interface

物理接口: 主要配置与MAC接口的类型,该核四种物理接口类型,均有IEEE802.3规范定义 (1)GMII可以支持以太网以10 Mb/s,100 Mb / s和1Gb/s的速度运行; (2)MII可以支持以10 Mb/s和100 Mb / s的速度运行以太网; (3)RGMII是GMII的双倍数据速率模式,也就是双沿采样,支持以太网以10Mb/s,100Mb/s和1Gb/s的速度运行。 (4)Internal是生成内核时,没有物理接口可用于连接到内部PHY,例如以太网1G / 2.5G PCS / PMA或SGMII LogiCORE。物理接口的选择决定了随核心提供的示例设计的内容,其中HDL中描述了外部GMII,MII或RGMII。RGMII,GMII或内部之间的核心HDL不变。如果选择了MII,则物理接口数据路径将减少为4位。默认为使用GMII。当我们选择2.5G时就是这种模式。 MAC Speed TEMAC解决方案可支持2.5Gb/s和1Gb/s速度运行,10Mb/s和100Mb/s速度运行以及全三速运行(10Mb/s,100Mb/s和1Gb/s速度能力)。可用于速度支持选择的选择取决于所选的物理接口: 当MAC数据速率设置为2.5 Gb / s时,仅内部模式可用。如果MAC数据速率设置为1 Gb / s,并且选择了GMII,RGMII或Internal,则可以选择三速操作和1 Gb / s操作。若MAC数据速率设置为1Gb/s并且选择了MII,则仅10Mb/s和100Mb/s的操作可用。Management Type(管理类型) 选择“ AXI4-Lite”选项以包括用于TEMAC配置的可选管理接口。如果未选择此选项,则会使用替换配置向量生成核心。如果未选择AXI4-Lite管理界面,则AVB选项不可用。默认设置是选择AXI4-Lite管理接口。 启用管理接口后,选择“管理数据输入/输出接口(MDIO)”选项以包括可选的MDIO接口。如果未选择此选项,则生成的内核不具有管理物理层中的对象所需的MDIO逻辑。 如果启用了MDIO,请选择“为MDIO接口端口添加IO缓冲区”选项以为MDIO接口端口插入I / O缓冲区。这将创建双向I / O总线mdio,并为mdc插入输出缓冲区。如果未选择此选项,则将使用mdio_i,mdio_o和mdio_t端口生成内核。 AXI4-Lite Frequency (AXI4-Lite频率) 这指定了AXI4-Lite接口的频率(以MHz为单位)。它用于提供综合的默认值,并且会根据系统中的连接性进行覆盖。 3、Shared Logic 没啥可说的

4、Features

MAC选项 TEMAC解决方案始终提供对全双工以太网的支持。但是,为了提供半双工操作,需要更多的FPGA逻辑资源。由于许多应用程序只需要全双工支持,因此半双工逻辑是可选的。 使用半双工逻辑生成内核时,可以使用TEMAC配置选择全双工或半双工操作。默认设置是不包括半双工支持。 AVB(Audio Video Bridging)选件 如果希望包含可选的AVB端点前端逻辑,请选择Enable_AVB选项。 如果数据速率设置为2.5 Gb / s,或者选择了半双工,则AVB选项被禁用。如果未选择AXI4-Lite管理界面,则AVB选项被禁用。如果选择此选项,则除了三模式以太网MAC许可证以外,还需要收费的以太网AVB端点许可证来启用内核生成。默认设置是不包括AVB端点。帧过滤器选项(Frame Filter Options) 可以使用帧过滤器生成内核,从而阻止接收与此MAC不匹配的帧。这最常用于识别专门针对此MAC的数据包。默认为使用帧过滤器。 表条目数(Number of Table Entries) 可以使用查找表来生成帧过滤器,该查找表最多可以包含16个其他有效MAC帧匹配模式。您可以选择0到16之间的整数来定义表中存在的匹配模式的数量。默认值为使用四个表条目。 启用优先流控制(Enable Priority Flow Control) 选择此选项可在核心中包括Priority Flow Control支持。如果包括在内,则包括在发送时生成PFC帧并在接收时解释PFC帧的电路,以及对IEEE 802.3暂停请求的增强XON / XOFF支持。默认设置为禁用。 统计计数器(Statistics Counters) 可以使用内置的统计计数器生成内核。可用的计数器数量取决于内核的双工设置,全双工需要34个计数器,半双工需要41个计数器。仅当内核配置有AXI4-Lite管理接口时,才能选择此选项。默认值为包括统计信息计数器 统计宽度(Statistics Width) 统计信息计数器可以是32位或64位宽。这使您可以控制必须轮询计数器的频率,以避免由于溢出而导致信息丢失。默认值为使用64位宽的计数器。 统计重置(Statistics Reset) 当包括统计计数器时,可以包括逻辑以确保在硬件复位时将计数器清除为零。没有此逻辑,计数器值将在复位后保持不变,并且仅在设备配置时清除。默认值为包括计数器重置功能 3.2 IP核的接口说明例化的IP核的用户接口如下表所示那些,已经封装为axis接口了,而且人家给了IP读写fifo及相关的状态标识,我们只需要用就可以。 名称 方向 位宽 含义 gtx_clk IN 1 核的全局时钟,1Gbps是125M,2.5Gbps是312.5M gtx_clk_out OUT 1 该时钟相对于gtx_clk输入具有0°相移,并用于RGMII数据传输。 gtx_clk90_out OUT 1 该时钟相对于gtx_clk输入具有90°相移,用于RGMII发送器时钟转发。 refclk IN 1 仅适用于GMII或RGMI,空闲控制需要,200M到300M, 对于UltraScale需要到300至1333M rx_enable OUT 1

rx_statistics_vector Out 28 接收侧逻辑状态信息的集合(Table 2-8:) rx_mac_aclk 时钟域 rx_statistics_valid Out 1 表示接收侧逻辑状态信息的集合内容的有效信号 rx_mac_aclk Out 1 用于在物理接口上接收数据的时钟,该时钟应用于为物理接口接收电路和RX AXI4-Stream接收电路提供时钟。 312.5MHz对应2.5 Gb/s 125MHz对应1 Gb/s 25MHz对应100 Mb/s 2.5MHz对应10Mb/s rx_reset Out 1 高电平有效 RX部分的软复位 rx_axis_mac_tdata Out 8 核收到的用户数据 rx_mac_aclk

rx_axis_mac_tvalid Out 1 rx_axis_mac_tdata的数据有效信号 rx_axis_mac_tlast Out 1 rx_axis_mac_tdata端口的控制信号。 表示帧中的最后一个字节。 rx_axis_mac_tuser Out 1 rx_axis_mac_tdata的控制信号。 在帧接收结束时置位,表示帧有错误。 rx_axis_filter_tuser Out X+1 每帧滤波器调谐器输出。可用于仅发送特定帧过滤器传递的数据。有关详细信息,请参阅帧过滤器 tx_enable Out 1 对于RGMII, 若为1Gbps,则一直高电平; 若为100Mbps,则十个周期中1个周期为高电平 若为10Mbps,则一百个周期中1个周期为高电平

tx_ifg_delay IN 8 用于可配置帧间间隙的控制信号 tx_mac_aclk tx_statistics_vector Out 32 状态收集统计

tx_statistics_valid Out 1 tx_statistics_vector数据的有效信号

tx_mac_aclk Out 1 用于在物理接口上传输数据的时钟,该时钟应用于为物理接口发送电路和TX AXI4-Stream发送电路提供时钟。 312.5MHz对应2.5 Gb/s 125MHz对应1 Gb/s 25MHz对应100 Mb/s 2.5MHz对应10Mb/s tx_reset Out 1 高有效,发送端模块的复位信号 tx_axis_mac_tdata IN 8 要传输的帧数据 tx_mac_aclk tx_axis_mac_tvalid IN 1 tx_axis_mac_tdata的数据有效信号,高电平有效 tx_axis_mac_tlast IN 1 tx_axis_mac_tdata的最后一个有效数据高电平 tx_axis_mac_tuser IN 1 tx_axis_mac_tdata端口的控制信号。表示允许MAC向PHY发送错误的帧中的错误情况,例如FIFO欠载。 tx_axis_mac_tready OUT 1 握手信号。当tx_axis_mac_tdata上的当前数据已被接受且tx_axis_mac_tvalid为High时,置位。在10/100 Mb / s时,这用于以正确的速率将数据计量到核心。 pause_req IN 1 暂停请求:根据请求,MAC在当前数据包完成时发送暂停帧 pause_val IN 16 暂停值:插入到传输的暂停帧的参数字段中。 speedis100 OUT 1 当内核以100Mb/s运行时,此输出有效。它来自MAC速度配置寄存器的位[13:12]。如果不存在可选的管理接口,则这是从配置向量位[13:12]派生的。 speedis10100 OUT 1 当内核以10 Mb / s或100 Mb / s运行时,此输出有效。它来自MAC速度配置寄存器的位[13:12]。如果管理接口不存在,则从配置向量位[13:12]导出 rgmii_txd OUT 4 传输数据到PHY,与PHY接口数据 tx_mac_aclk rgmii_tx_ctl OUT 1 到PHY的控制信号 rgmii_txc OUT 1 到PHY的时钟信号 rgmii_rxd IN 4 接收PHY的数据 rgmii_rxc rgmii_rx_ctl IN 1 来自PHY的控制信号 rgmii_rxc IN 1 来自PHY的时钟 inband_link_status OUT 1 来自PHY的链路状态 rgmii_rxc inband_clock_speed OUT 2 来自PHY的链路速度,这个是PHY硬件配置的 inband_duplex_status OUT 1 来自PHY的双工状态 mdio OUT 1 用于与PHY配置和状态通信的数据信号。若未使用则绑定高。 IN 1 输出数据信号,用于与PHY配置和状态进行通信 mdc OUT 1 MDIO管理时钟:使用可选的管理接口时,根据提供的配置数据从s_axi_aclk派生。 s_axi_aclk IN 1 AXI4-Lite的时钟,用与对MAC和PHY芯片进行初始化和相应配置工作。时钟频率应在10-300M s_axi_resetn IN 1 复位,低有效 s_axi_awaddr IN 12 写入地址,AVB端点时禁用。 s_axi_awvalid IN 1 写地址有效 s_axi_wdata IN 32 写数据 s_axi_wready OUT 1 写数据就绪 s_axi_bresp OUT 2 写响应 s_axi_bvalid OUT 1 写响应有效 s_axi_araddr IN 12 读地址,AVB端点时禁用。 3.3 MDIO管理接口设计实例中的“tri_mode_ethernet_mac_0_axi_lite_sm.v”模块,该模块主要功能是对PHY的配置和对核的配置。配置方式是写寄存器,具体映射关系可看IP使用文档pg051。 这三个状态机通过start_access、start_mdio来驱动具体的步骤。 写有三个操作,这三个操作都是在状态机“axi_access_sm == WRITE”下执行的。 如图所示,首先,在写的过程中中会将s_axi_bready置位高电平表示,这是个响应准备信号,这个信号表明主设备要准备接受写的数据了。与之同时将数据、地址在分别对应的有效信号下发送出去。当收到s_axi_awready脉冲信号表示写地址完成,当收到s_axi_wready信号表示写数据完成。当收到s_axi_bvalid信号表示写事务完成。这三个操作的状态会用axi_status来表示,某位=1表示该事务执行完成,当三个是事务均执行完成,则可进入下一个状态机

状态机的逻辑如下图,其实,知道了其中原理,具体细节和在研究。

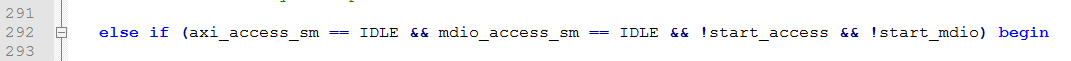

这个模块有三个状态机。 1、axi_state: 控制该模块配置管理的整个进程,可以说是指导操作步骤,是主动工作的,这个状态机执行的首要条件是两个“从状态机”在IDLE状态,且没有启动相关进程。

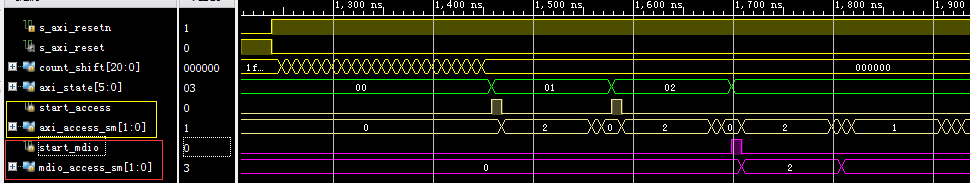

由下图可知“start_access”信号启动“axi_access_sm”状态机,“start_mdio”信号启动“mdio_access_sm”状态机。 这里的设计思想是: “axi_state”状态机控制进程,到了一个新的进程,将“start_access”或“start_mdio”拉高,让另外两个模块执行具体的操作。由于这两个信号拉高,“if”条件不满足,跳出该状态机锁存状态。等相对应状态机执行完成后有满足了条件继续下一个进程。

2、mdio_access_sm: “axi_state”状态机进程中有些数据是对核的配置,有些是对PHY芯片配置寄存器操作的。这个状态机主要是描述对PHY芯片操作的相关逻辑。是由“start_mdio”启动的。具体的读写数据还是由“axi_access_sm”状态机完成,本状态机主要是做发送数据的组合。状态机的执行有个限制条件,如下图,所以该状态机和“axi_state”一样,执行一个周期锁存了,等待数据或读或写完成后再根据条件来启动。

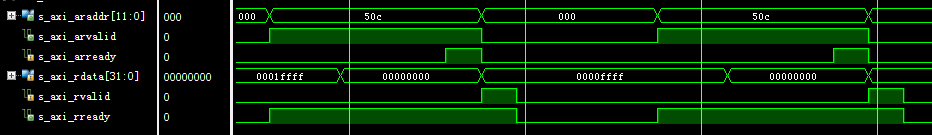

3、axi_access_sm: 该状态机是控制aix4_lite接口的读写操作,无论是对核配置还是对PHY芯片的寄存器读写,都是根据这个状态机来完成的。 写操作时序如下图所示: “axi_status[2]”表示写数据操作,“axi_status[3]”表示写地址操作,均是收到从器件响应完成对应操作置一,“axi_status[4]”置一表示收到本次写数据完成标识。这2bit为1表示一次写完成。该状态机回到IDLE状态。

读操作时序如下图所示:

该模块的具体执行步骤: (STARTUP)启动状态机,配置MIDO时钟,对核操作输入的复位信号“s_axi_resetn”是低电平复位,在本模块首先做了取反操作。

在复位结束后延时21个时钟周期启动状态机,并对配置MDIO寄存器(0x500)写入0x58对核支持的MIDO进行配置

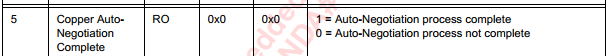

2.(UPDATE_SPEED)配置以太网速率,对核操作 对寄存器地址“17'h410”写入“{speed, 30'h0}”, 3.(MDIO_RD)读MDIO,对PHY操作 读寄存器地址1的内容,具体内容可见88E111数据手册的131页介绍。 4、(MDIO_POLL_CHECK)对读PHY数据进行检查 如果均是1,则认为没有管理接口,直接开始对MAC进行复位操作否则认为有MIDO管理接口,进行对相应配置我们这里认为是有管理接口的 5、(MDIO_1G)写MIDO寄存器,对PHY的管理接口操作 写MDIO地址9的地址空间,具体内容可见88E111数据手册的155页介绍,是对1000M全半双工的配置。 其中,bit9 = 1表示1000M全双工 6、(MDIO_10_100)写MIDO寄存器,对PHY的管理接口操作 由于PHY芯片的MIDO管理接口的寄存器堆网口速率的配置是在不同地址,对于FPGA用一个2bit的speed即可配置三种速率(00=10Mb/s,01=100Mb/s,10 =1Gb/s)。但对于MIDO则需要写两个地址的寄存器。 又由于事先并不知“speed”的值,或者说不对该值进行判断。故还需要对配置10M或100M的寄存器写值,当然写入的值是与写入1000M的内容是互斥的,并不会混淆。 写MDIO的PAGE0的地址4的地址空间,具体内容可见88E111数据手册的137页介绍,是对10M、100M全半双工的配置。 7、(MDIO_PAGE2)换页,写MIDO寄存器,对PHY的管理接口操作 8、(MDIO_DELAY_RD)换页,读MIDO寄存器,对PHY的管理接口操作 写MDIO地址15的地址空间,具体内容可见88E111数据手册的158页介绍, 9、(MDIO_DELAY_RD)换页,读MIDO寄存器,对PHY的管理接口操作 10、(MDIO_DELAY_RD_POLL) 锁存读出的数据,为下一周期的写做准备。 11、(MDIO_DELAY) 没看懂 12、(MDIO_RESTART)写MIDO寄存器,对PHY的管理接口操作 这个模块可以选择回环模式,通过“phy_loopback”来设置,目前先不考虑 对MIDO的地址0写数据,数据内容跳过 13、(MDIO_STATS)读MIDO寄存器,对PHY的管理接口操作 读寄存器地址1的内容,用来得到自动协商完成的信号 14、(MDIO_STATS_POLL_CHECK)读MIDO寄存器,对PHY的管理接口操作 如果自动协商操作完成则进入下一个状态,否则等待

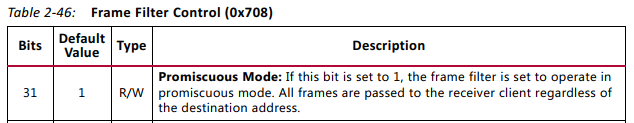

15、(RESET_MAC_RX)对核操作 对地址(0x404)写入32'h90000000;//bit 28:Receiver Enable **** bit31:rest 16、(RESET_MAC_TX)对核操作 对地址(0x408)写入32'h90000000;//bit 28:Receiver Enable **** bit31:rest 17、(CNFG_MDIO)对核操作 配置管理寄存器,对地址(500)写入“68”。使能MDIO及配置其速率。 18、(CNFG_FLOW) 配置管理寄存器,对地址(40C)写入“0”。这是流控制配置字。 19、(CNFG_FILTER) “design_on_board”是个标志位,由(4)来决定的,如果没有管理接口则为0 这里我们设置为1,故将核心设置为混杂模式。对地址“708”写入1

混杂模式:如果此位设置为1,则帧过滤器将设置为混杂模式。无论目标地址如何,所有帧都将传递到接收方客户端。 20、(CNFG_FRM_FILTER_1) 配置管理寄存器,对地址(701)写入“32'h040302DA”。 21、(CNFG_FRM_FILTER_MASK_1) 配置管理寄存器,对地址(750)写入“32' hFFFFFFFF“。帧过滤器掩码值 22、(CNFG_FRM_FILTER_2) 配置管理寄存器,对地址(714)写入“32' h025A0605 “。帧过滤器相关 23、(CNFG_FRM_FILTER_MASK_2) 配置管理寄存器,对地址(754)写入“32' hFFFFFFFF“。帧过滤器相关 24、(CNFG_FRM_FILTER_3) 配置管理寄存器,对地址(758)写入“32'h06050403“。帧过滤器相关 25、(CNFG_FRM_FILTER_MASK_3) 配置管理寄存器,对地址(750)写入“32' hFFFFFFFF“。帧过滤器相关 26、(CHECK_SPEED) 如果收到“update_speed_reg”信号后进入“(2)UPDATE_SPEED”状态更新以太网速率。 “serial_command”这个先不考虑,大致流程是搞懂了 通过管理接口访问MDIO接口完全是寄存器映射。表2-37显示了MDIO寄存器列表。有关详细信息,请参阅MDIO接口。仅当使用可选MDIO接口生成内核时,这些寄存器才可用。

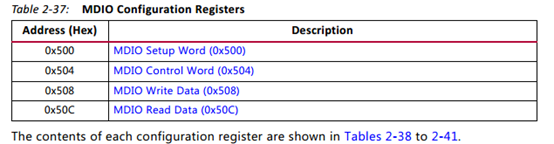

表4.1 MDIO配置寄存器释义 映射地址为0x500,设定 位 默认值 类型 描述 31:7 N/A Ro 保留 6 0 R/W MDIO启用: 此位为1时,MDIO接口可用于访问连接的PHY设备。 该位为0时,MDIO接口被禁用,MDIO信号保持无效。 只有将Clock Divide设置为非零值时,才允许写入该位。 5:0 0 R/W 这个是配置mdc频率的,规范要求mdc频率不能大于2.5M,为了防止超出规范,Clock Divide值默认为0,也就不启用。 例如例子,s_axi_aclk=100M,Clock Divide为24,mdc = 2M

映射地址为0x504,Mido的控制字 位 默认值 类型 描述 31:29 N/A Ro 保留 28:24 0 R/W TX_PHYAD:这可以控制正在访问的PHY地址。 23:21 N/A Ro 保留 20:16 0 R/W TX_REGAD:它控制被访问的寄存器地址。 15:14 0 R/W TX_OP:该字段控制写入1以启动时执行的访问类型。 01写访问 10读访问 13:12 N/A Ro 保留 11 0 WO 启动:向此位写入1将启动MDIO传输 10:8 N/A Ro 保留 7 0 RO MDIO就绪:设置后,MDIO已启用并准备好进行新传输。这也用于识别先前的事务何时完成(例如,读取数据有效)。 6:0 N/A Ro 保留 映射地址为0x508,Mido的写数据 31:16 N/A Ro 保留 15:0 0 R/W 写数据 映射地址为0x50C,Mido的读数据 31:17 N/A RO 保留 16 0 RO MDIO Ready:这是MDIO控制字的位[7]的副本 15:0 0 RO 读数据 映射地址为0x410,MAC波特率的配置 31:30 10 R/W MAC的速率配置 00:10Mb/s 01:100Mb/s 10:1Gb/s 当为1Gb/s或2.5Gb/s的速度支持生成TEMAC解决方案时,位[31:30]被硬编码为值10。 当生成TEMAC解决方案以支持10Mb/s和100Mb/s的速度时,位[31:30]仅接受值00来配置10Mb/s的操作,或者接受01来配置100Mb/s的操作 操作。 29:0 N/A RO 读数据 欢迎关注“沧小海的FPGA”微信公众号,回复“eth”可获取相关资料和官方例程的仿真时序整理 开发软件为vivado2016.3,打开工程点击“Flow”选择“open static simulation”打开静态仿真可直接查看信号波形

|

【本文地址】