| 计算机系统基础(五)之RISC | 您所在的位置:网站首页 › 什么是risc指令集 › 计算机系统基础(五)之RISC |

计算机系统基础(五)之RISC

|

RISC-V指令集

本文主要介绍RISC-V指令集,简单总结一些重点信息,其中参考了《RISC-V 手册》和《计算机组成与设计 硬件与软件接口 RISC V 版》,如果学习过程中有问题,欢迎指正。 提示:写完文章后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 RISC-V指令集前言一、RISC-V诞生的意义二、RISC-V ISA 命名规范三、 模块化3.1RISC-V的基础指令模块3.1.1 R 类型指令3.1.2 I类型指令3.1.3 S类型指令3.1.4 B类型指令3.1.5 U类型指令3.1.6 J类型指令 3.2 RV32I 寄存器3.3 RISC-V的寻址方式 总结 前言提示:以下是本篇文章正文内容,下面案例可供参考 一、RISC-V诞生的意义RISC-V要成为一个指令集,他必须要符合一下这些特征。 要能适应包括从最袖珍的嵌入式控制器,到最快的高性能计算机等各种规模的处理器 应该能兼容各种流行的软件栈和编程语言 应该适应所有实现技术,包括现场可编程门阵列(FPGA)、专用集成电路 (ASIC)、全定制芯片,甚至未来的设备技术。 应该对所有微体系结构样式都有效 应该支持广泛的专业化,成为定制加速器的基础 应该是稳定的,基础的指令集架构不应该改变 RISC-V相对于以前传统的指令集,它的优点在于: 一个最近诞生的指令集架构是一个开源的指令集架构模块化社区化稳定清晰的分层设计 二、RISC-V ISA 命名规范RISC-V的命名规范:RV[###][abc……xyz]。例如:RV32IMA,RV64GC RV:用于标识 RISC-V 体系架构的前缀,即 RISC-V 的缩写。[###]:{32, 64, 128} 用于标识处理器的字宽,也就是 处理器的寄存器的宽度(单位为 bit)。[abc…xyz]:标识该处理器支持的指令集模块集合。 三、 模块化RISC-V的模块化是以一个名为RV32I的基础ISA作为核心模块,RV32I是固定的,永远不会改变,但根据应用程序的需要可以选择扩展模块。 扩展模块指令集: RISC-V 允许在实现中以可选的形式实现其他 标准化和非标准化的指令集扩展。特定组合“IMAFD”被称为 “通用(General)” 组合,用英文字母 G 表示。这种模块化特性使得RISC-V具有了袖珍化、低能耗的特点,而这对于嵌入式应用可能至关重要。惯例是把代表扩展的字母附加到指令集名称之后作为指示。例如,RV32IMFD将乘法(RV32M),单精度浮点(RV32F)和双精度浮点(RV32D)的扩展添加到了基础指令集(RV32I)中。 用一个公式简单表达,即: RISC ISA = 1 个基本整数指令集 + 多个可选的扩展指令集 3.1RISC-V的基础指令模块

RISC-V有六种基本指令格式: R 类型指令,用于寄存器-寄存器操作I 型指令,用于短立即数和访存 load 操作S 型指令,用于访存 store 操作B 类型指令,用于条件跳转操作U 型指令,用于长立即数J 型指令,用于无条件跳转以RV32为例 如下图所示: R类型指令将32位划分成6个区域: opcode是操作码,占了7bit,在指令格式的0-6bit位上rd (Destination Register)是目的寄存器,占了5bit,在指令格式的7-11bit位上funct3+funct7是两个操作字段。funct3占了3bit,在指令格式的12-14bit位上;funct7占了7bit,在指令格式的25-31bit位上。rs1 (Source Register #1)是第一个源操作数寄存器,占了5bit,在指令格式的15-19bit位上。rs2 (Source Register #2)是第二个源操作数寄存器,占了5bit,在指令格式的25-31bit位上。

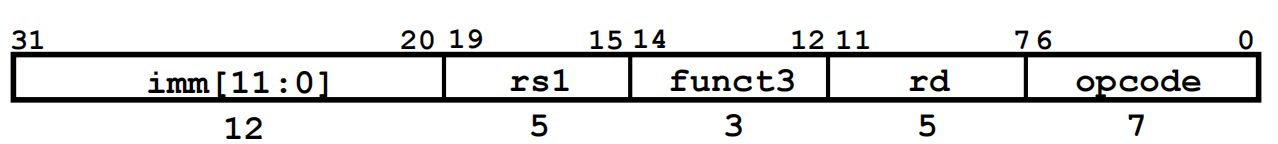

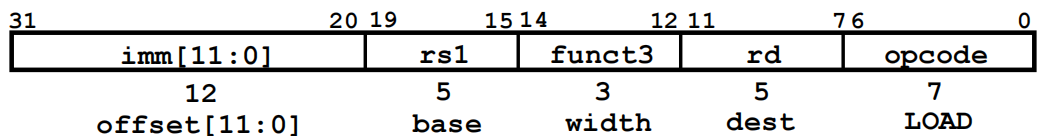

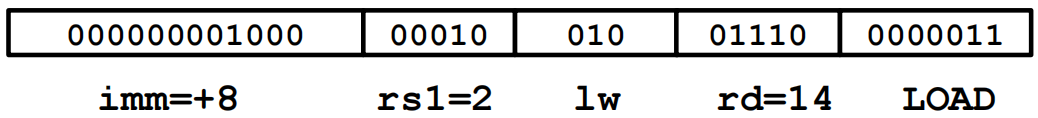

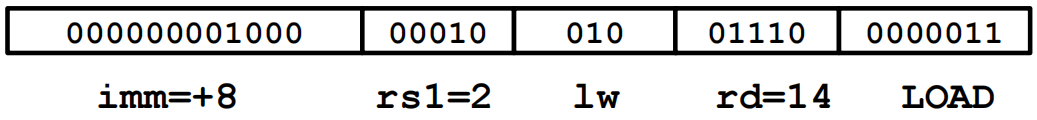

I类型指令将32位划分成5个区域: opcode是操作码,占了7bit,在指令格式的0-6bit位上rd (Destination Register)是目的寄存器,占了5bit,在指令格式的7-11bit位上funct3是操作字段。funct3占了3bit,在指令格式的12-14bit位上。rs1 (Source Register #1)是第一个源操作数寄存器,占了5bit,在指令格式的15-19bit位上。存放12位的立即数——imm[11:0],在指令格式的20-31bit位上。I类型指令可以用于: 寄存器-立即数的运算加载指令格式上只有一个字段不同于r格式,rs2和funct7替换为12位符号立即数(immediate字)imm[11:0]。immediate字段为补码值,所以它可以表示从-2"到2"-1之间的整数。当I型格式用于加载指令时,immediate字段表示一个字节偏移量,所以加载双字指令可以取相对于基址寄存器rd中基地址偏移±(2"或2048)字节(±(2或256)个双字)的任何双字。 指令格式展示: 寄存器-立即数的运算 I类型的指令算术展示:  注:RV32I 支持加载有符号和无符号字节和半字(lb,lbu,lh,lhu) 注:RV32I 支持加载有符号和无符号字节和半字(lb,lbu,lh,lhu)

举例: addi x15,x1,-50

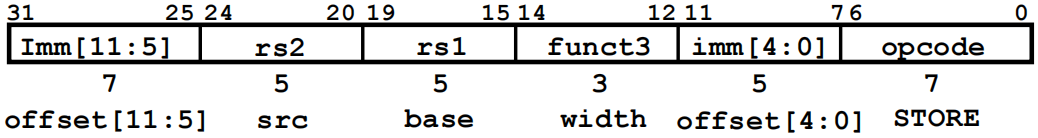

S类型指令将32位划分成6个区域: opcode是操作码,占了7bit,在指令格式的0-6bit位上imm[4:0]+imm[11:5]:立即数分成两个:存放前5位的立即数——imm[4:0],在指令格式的7-11bit位上;存放后7位立即数——imm[11:5],在指令格式的25-31bit位上。funct3是操作字段。funct3占了3bit,在指令格式的12-14bit位上。rs1 (Source Register #1)是第一个源操作数寄存器,占了5bit,在指令格式的15-19bit位上。rs2 (Source Register #2)是第二个源操作数寄存器,占了5bit,在指令格式的25-31bit位上。S型格式的12位 immediate字段分成了两个字段,低5位和高7位。RISC-V体系结构设计师选择这种设计是因为它能够在所有指令格式中保持rs1和 rs2字段在相同的位置。保持尽可能相似的指令格式降低了硬件的复杂性。同样,opcode和 funct3字段也总是保持同样的大小并在同一个位置。 指令格式展示:

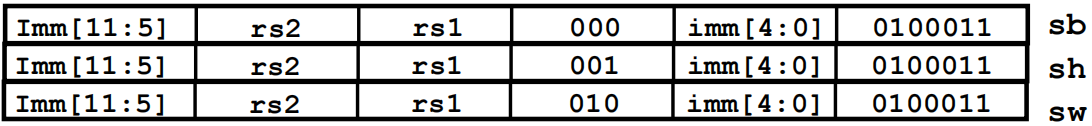

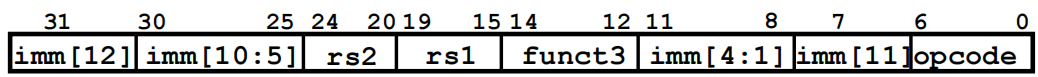

B类型指令将32位划分成6个区域: opcode是操作码,占了7bit,在指令格式的0-6bit位上imm[4:1]+imm[11]+imm[10:5]+imm[12]:立即数分成四个: 存放第11位的立即数——imm[11],在指令格式的第7bit位上;存放第1位到第5位的立即数——imm[4:1],在指令格式的8-11bit位上;存放后6位的立即数——imm[11:5],在指令格式的25-30bit位上;存放第12位的立即数——imm[12],在指令格式的31bit位上。 注:imm[0]被丢弃,因为它始终为零。 funct3是操作字段。funct3占了3bit,在指令格式的12-14bit位上。rs1 (Source Register #1)是第一个源操作数寄存器,占了5bit,在指令格式的15-19bit位上。rs2 (Source Register #2)是第二个源操作数寄存器,占了5bit,在指令格式的25-31bit位上。B类型指令属于有条件的分支。RV32I 可以比较两个寄存器并根据比较结果上进行分支跳转。比较可以是:相等(beq),不相等 (bne),大于等于(bge),或小于(blt)。最后两种比较有符号比较,RV32I 也提供相应的无符号版本比较的:bgeu 和 bltu。剩下的两个比较关系(大于和小于等于)可以通过简单地交换两个操作数,即可完成比较。因为 x < y 表示 y > x 且 x ≥ y表示 y ≤ x。 该指令表示如果寄存器rs1中的值等于寄存器rs2中的值,则转到标签为L1的语句执行。助记符beq代表相等则分支。 第二条指令是: bne rs1, rs2, Ll该指令表示如果寄存器rs1中的值不等于寄存器rs2中的值,则转到标签为L1的语句执行。助记符bne代表不等则分支。 这两条指令通常称作条件分支指令。 注:PC 相对寻址在后续补充

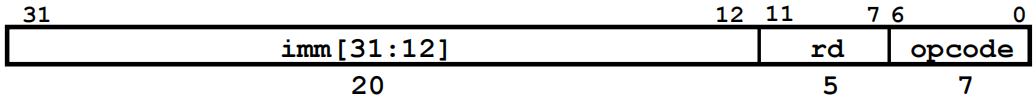

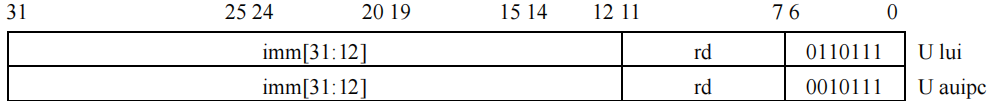

U类型指令将32位划分成3个区域: opcode是操作码,占了7bit,在指令格式的0-6bit位上rd (Destination Register)是目的寄存器,占了5bit,在指令格式的7-11bit位上imm[31:12]:存放高20位的立即数——imm[31:12],在指令格式的12-31bit位上

U类型指令包含两种指令 LUI – 加载高位立即数AUIPC – 立即数地址添加到PC寄存器中

注:由于ADDI的12位立即数最高位是符号位。例如: 如何利用LUI加载0xDEADBEEF LUI x10, 0xDEADB # x10 = 0xDEADB000 ADDI x10, x10, 0xEEF # x10 = 0xDEADAEEF由上可知 0xDEADAEEF不等于0xDEADBEEF 所以当ADDI 的12位立即数为负,也就是最高位bit位为1时,得到而结果是高20为减1再和低12位拼接起来。(减1是和补码有关) 解决方法:当数值的低12位的符号为1时,将利用lui装入的高20为的立即数值预先加1,而ADDI写入的低12位不变。如下 LUI x10, 0xDEADB # x10 = 0xDEADB000 ADDI x10, x10, 0xEEF # x10 = 0xDEADAEEF在汇编语言中还可以使用li伪指令,直接装入32位的数值,但时它在编译时还是会编译成LUI和ADDI这两条指令。 li x10, 0xDEADBEEFAUIPC指令加载一个20bit的的立即数,取值范围为0-1048575,但是该指令rd中保存的数据是(pc)+(立即数 |

【本文地址】

R类型的全部指令

R类型的全部指令  例子:

例子:

加载指令 同样格式的I类型指令也可以用作加载指令

加载指令 同样格式的I类型指令也可以用作加载指令

注:其中画圈表示位移方向0表示向左移,1表示向右移

注:其中画圈表示位移方向0表示向左移,1表示向右移 加载:

加载:

S类型的指令算术展示:

S类型的指令算术展示:  注:sb = Store byte,sh = Store halfword, sw = Store word 举例

注:sb = Store byte,sh = Store halfword, sw = Store word 举例

RISC-V汇编语言包含两个决策类指令,类似于带go to的if语句。

RISC-V汇编语言包含两个决策类指令,类似于带go to的if语句。 举例

举例

之前的类型指令中,已经有了12位的立即数作为表示常量。虽然常量通常很短并且适合12位,但有时它们也会更大。RISC-V指令系统包括指令 load upper immediate(取立即数高位,lui),用于将高20位常数加载到寄存器的第31位到第12位。将寄存器的低12位用0填充。该指令会与ADDI指令一起使用,目的是将低12位写入目标寄存器,以实现对32位的寄存器数值设置。 LUI x10 0x87654 # x10 = 0x87654000 ADDI x10,x10,0x321 # x10 = 0x87654321

之前的类型指令中,已经有了12位的立即数作为表示常量。虽然常量通常很短并且适合12位,但有时它们也会更大。RISC-V指令系统包括指令 load upper immediate(取立即数高位,lui),用于将高20位常数加载到寄存器的第31位到第12位。将寄存器的低12位用0填充。该指令会与ADDI指令一起使用,目的是将低12位写入目标寄存器,以实现对32位的寄存器数值设置。 LUI x10 0x87654 # x10 = 0x87654000 ADDI x10,x10,0x321 # x10 = 0x87654321