| 数电实验 | 您所在的位置:网站首页 › 二进制钟表怎么看时间图解图片 › 数电实验 |

数电实验

|

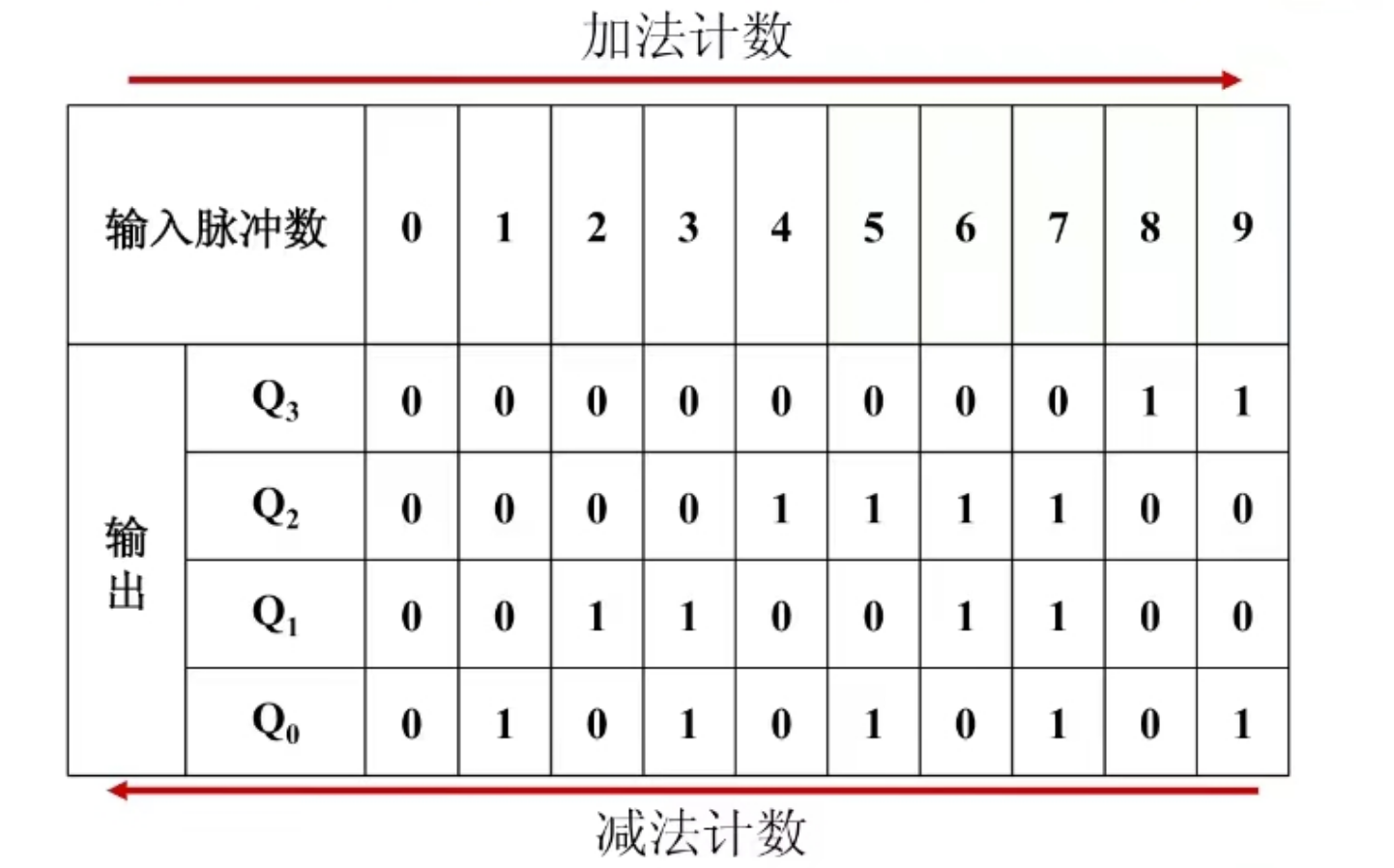

目录 一、74LS192芯片介绍 管脚图 编辑逻辑图与功能表 工作原理 二、任意进制计数器的实现 1.复位清零法 2.外部反馈置数法 一、74LS192芯片介绍74LS192是一种二进制同步上升计数器芯片,可以用于数字计数和时序控制等应用。它是TTL逻辑家族中的一员,采用了低功耗,高噪声抑制特性以及快速反应时间的优点,广泛应用于各种电子设备和系统中。

逻辑图与功能表 逻辑图与功能表

74LS192是一个同步计数器,每一次时钟信号(CLK, CLK')到达时它会产生一个计数,并根据实现方式进行输出。它可以按照二进制位数(4位)从0000到1111计数,并提供异步清零功能(MR)。当CLR引脚接地时,输出会自动清零到0000。在计数器工作时,可以通过使能引脚(ENABLE)进行控制,使计数器的输出停止,并锁定在当前状态。 二、任意进制计数器的实现平时我们用的都是十进制数,也就是0~9这样的数字,当计数到10的时候,就清零进位。然后就重新计数。同样的这里我们,可以去通过74ls192芯片去实现计数器的功能,比如N=6,即6进制计数器,那么计数范围就是0~5之间,74ls192芯片有多种计数方法,一般情况我们用加法计数比较多,那下面我就主要去讲通过加法计数去实现任意进制计数器的功能,其方式分为复位清零法和外部置数法。(74ls192芯片加法计数器输入脉冲端是高电平有效) 1.复位清零法同步复位就是非常专业,不留一点马虎,和他的名字一样,只在时钟的有效沿发生,所以一个有效的同步信号,至少要维持一个时钟周期(把你叫不醒,是不会停的)。由于仅仅在时钟的有效沿有效,所以可以滤除复位信号上的毛刺,电路可靠性好很多 这里我展示一个示例: 我们要用74ls192芯片去设计一个七进制的计数器(4个输入),也就是N=7的时候,0~6为有效范围,数到7的时候就清零,实现我们先画出状态转换图:

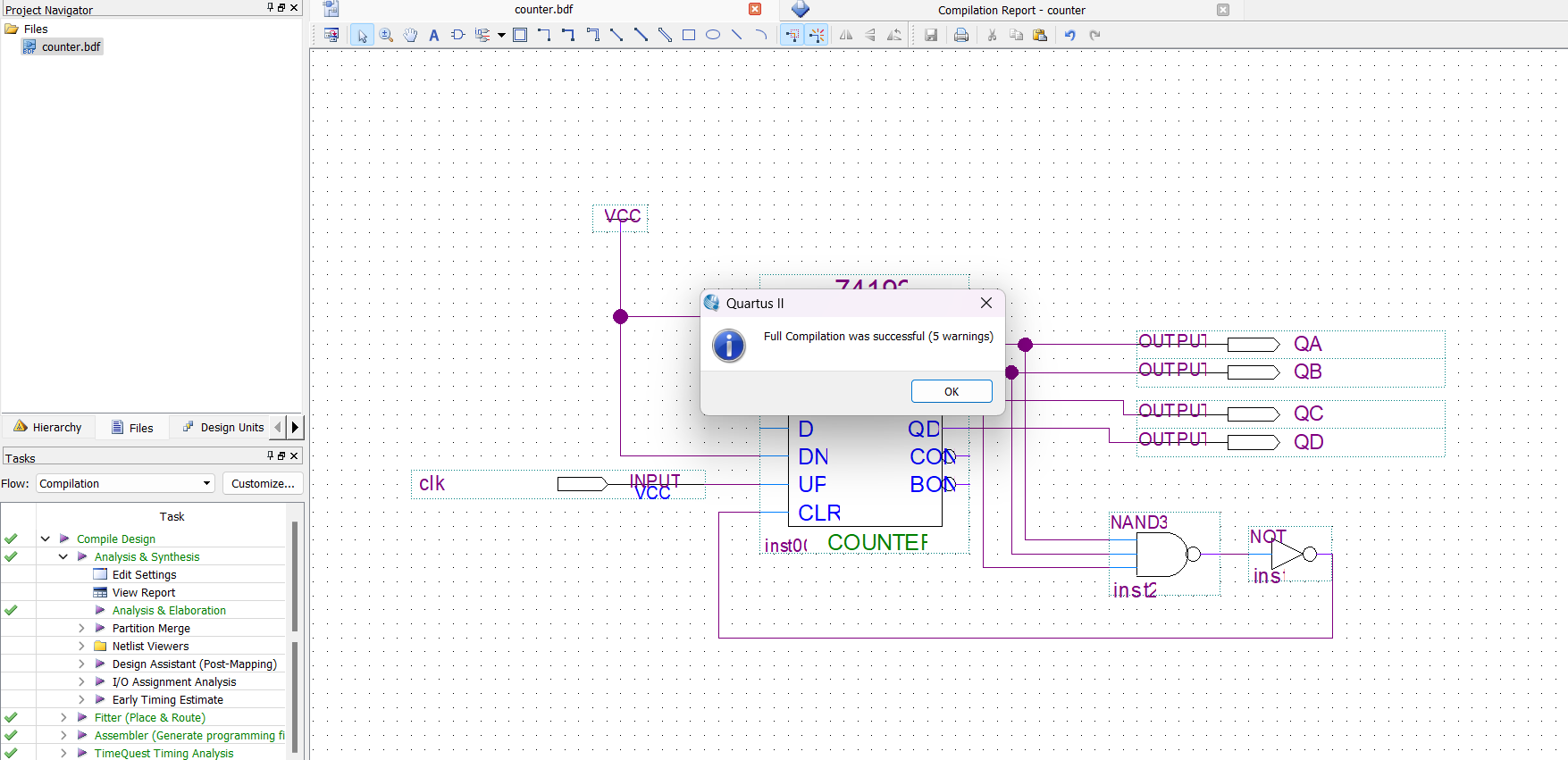

通过状态转换图我们可以知道,当计数到7的时候也就是 0111时候,我们就进行复位操作,回到0然后重新开始计数。 也就是说在74ls192芯片计数端口Q3Q2Q1Q0为 0111 的时候就进行复位,下面是基于Quartus II上的电路连接图:

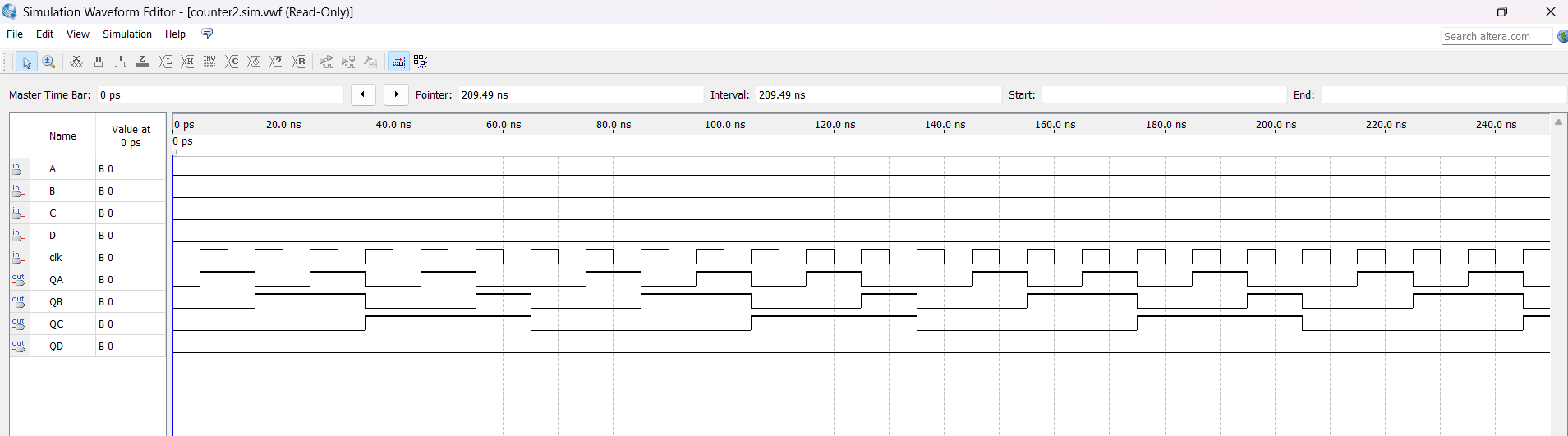

编译运行无误后进行仿真 仿真结果如下:

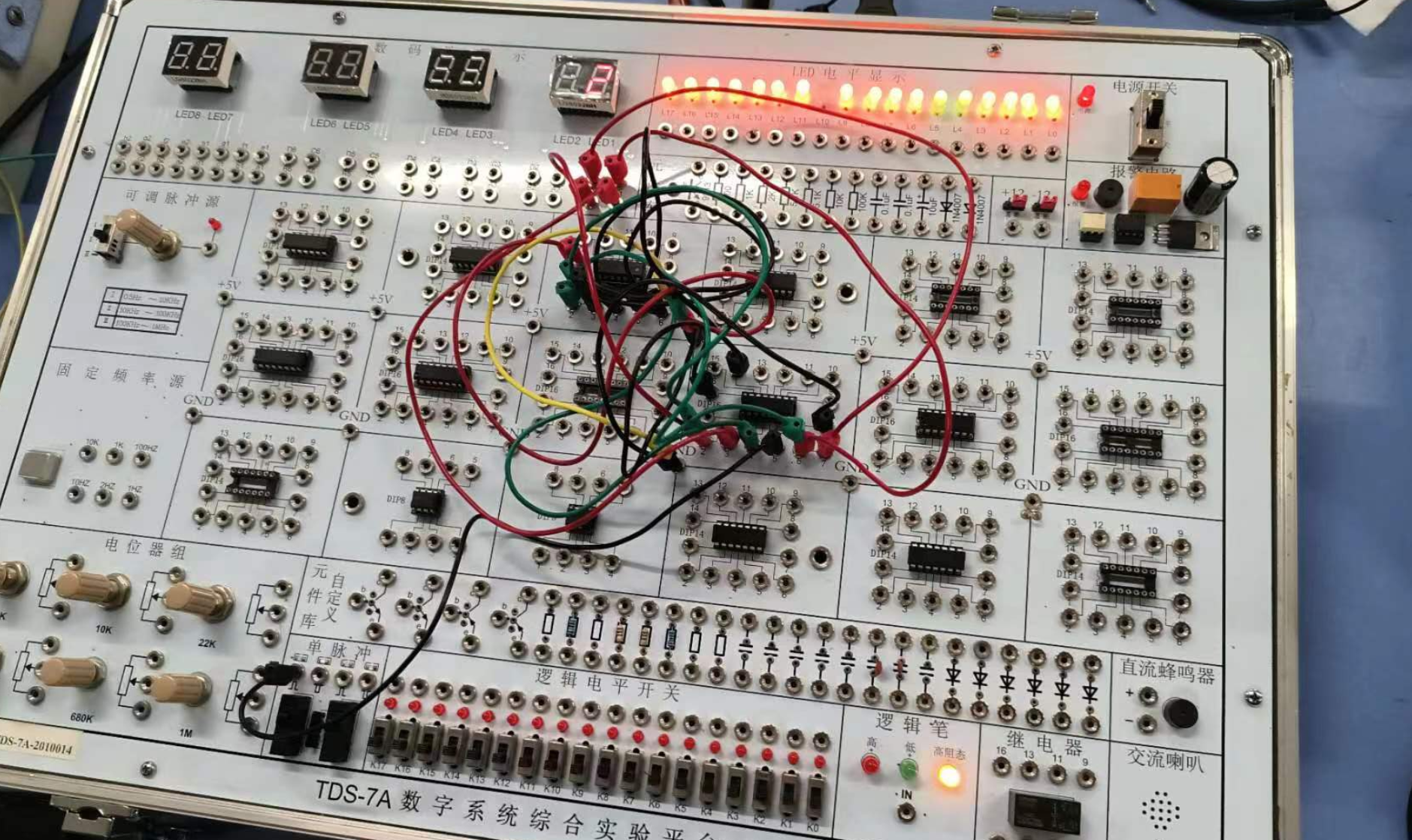

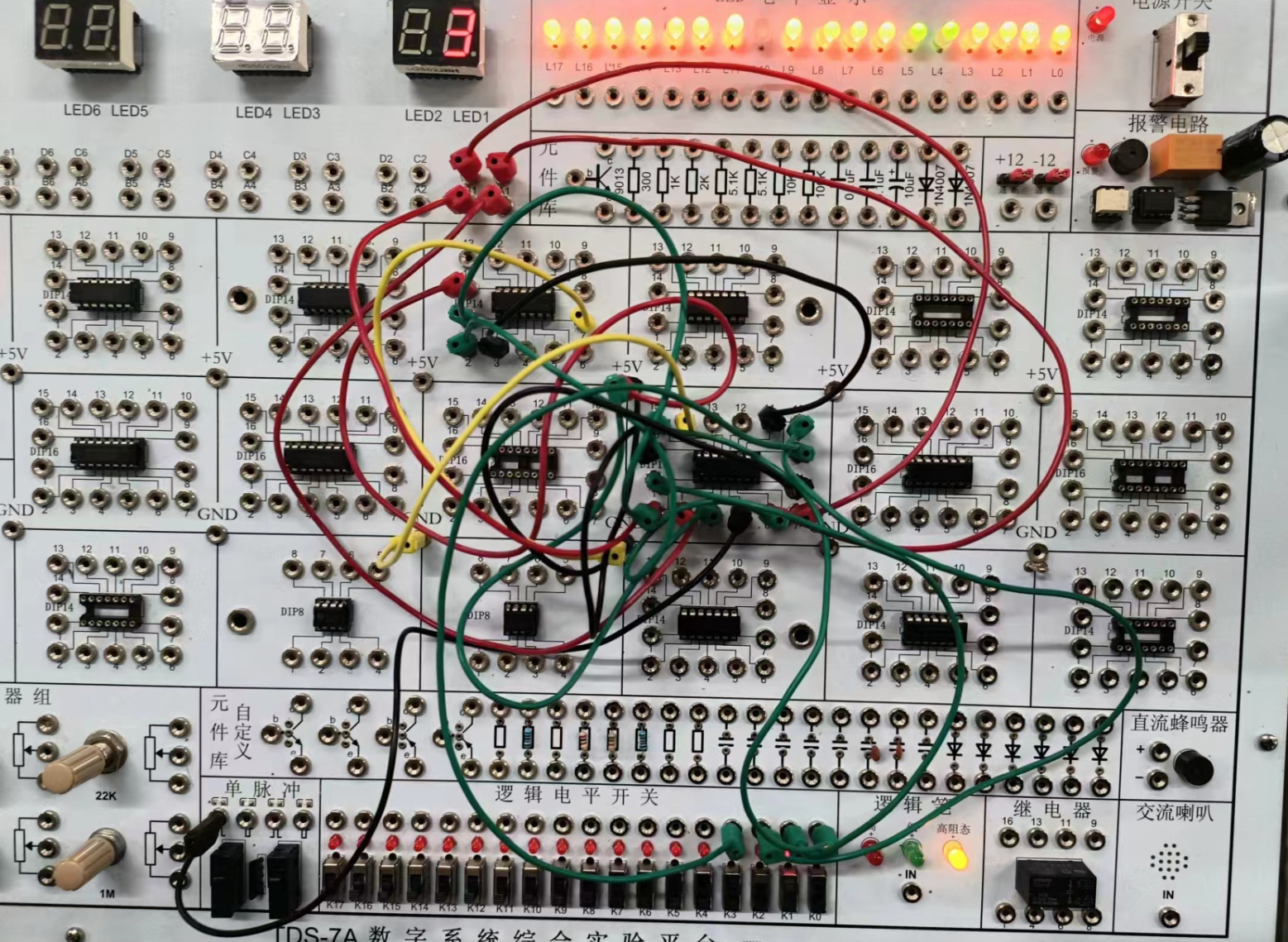

从仿真结果我们可以看出,clk输入频率每输入到第七次的时候,QA,QB,QC,QD就回归到了零,然后重新开始计数。仿真结果与理论无误。 实际电路连接图: 反馈置数法是利用计数器的同步置数控制端的数据输入端,把计数器状态置到某个数值来实现任意进制计数器。 置入的数值可以是0000到1111之间的任意数值。 当置入0000时,和复位或者清零的作用是相同的,因此这种方法比第一种反馈复位法灵活性要大。 这么说吧,外部反馈置数法也就是我们可以去通过手动设置开始计数的数字,也就是说相较于前面的复位清零法只能从零开始走到结尾,再重新回到零,而外部反馈置数法是可以直接跳到从零开始到结尾之间的任意位置作为起始点,其灵活性大大的提高了许多。 下面是基于Quartus II上的电路连接图:

仿真结果如下: 置数端DCBA为 0000,也就是初始化置数为0的时候:

这里我们可以看出,其输出结果跟上一个复位法的仿真结果是一样的,因为初始化的数值都是为0,也就是从0数到6,到7的时候就再次复位为0. 置数端DCBA为 0010,也就是初始化置数为2的时候:

这里我们可以看出除了第一次的是从0数到6,其他结果都是每次回归到2然后开始数数到6,然后再次回归到2,结果跟上面的是不同的。这就是外部置数反馈法。当然我们可以去输入其他置数数据,每次回归的结果是不同的。这里我们就可以去通过置数法来去实现任意进制的计数器,可以看出外部反馈置数法是非常灵活的。 实际电路连接图: 以上就是本期的全部内容,我们下次见! 分享一张壁纸: |

【本文地址】