| 一文读懂:什么是RISC | 您所在的位置:网站首页 › 中国自主cpu发展了解 › 一文读懂:什么是RISC |

一文读懂:什么是RISC

|

各位ICT的小伙伴们大家好呀。 提到CPU, 大家首先就会想到"卡脖子"事件。

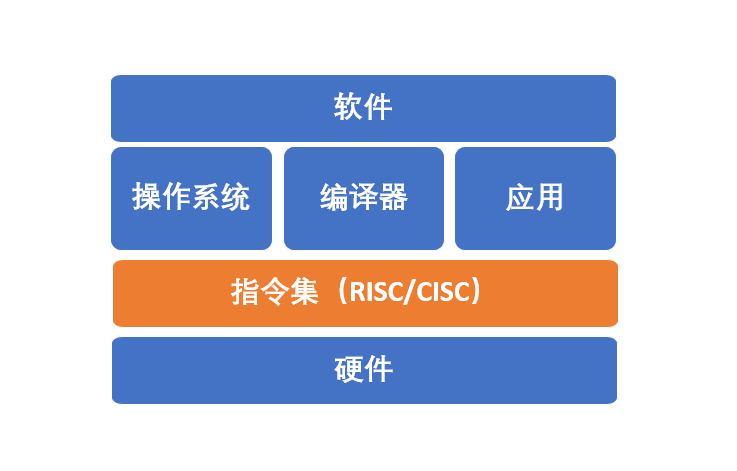

X86和ARM的IP授权虽然方便,但是不自主和不可控, 一被限制就可能导致国内一夜间"无芯"可用。 今天我们就来聊聊一个解决芯片卡脖子的有效方式--开源RISC-V芯片。 ▉ 聊芯片前我们先聊聊什么是指令集? 要想了解CPU,那不可避免的要了解指令集。 我们平常说的X86、ARM芯片,都是指的芯片的指令集架构。 指令集是软件和硬件之间的接口,简单来说指令集就是软件与硬件之间沟通的"翻译官",是芯片产业中不可或缺的基础部分。

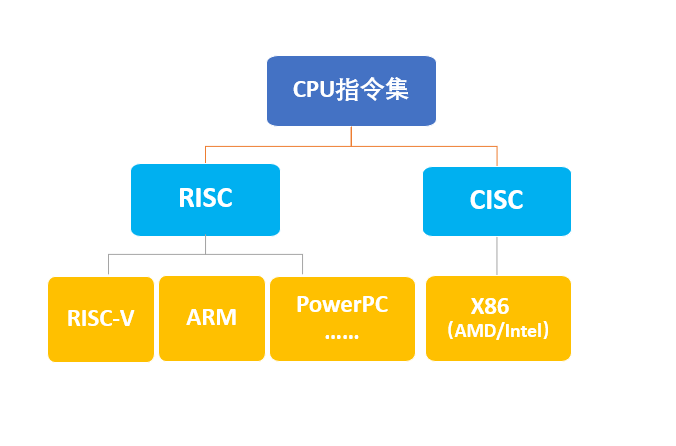

使用不同的指令集,代表着不同的CPU。目前市面上的CPU分类主要分有两大阵营,一个是Intel、AMD为首的复杂指令集(CISC)CPU,另一个是以IBM、ARM、RISC-V为首的精简指令集(RISC)CPU。

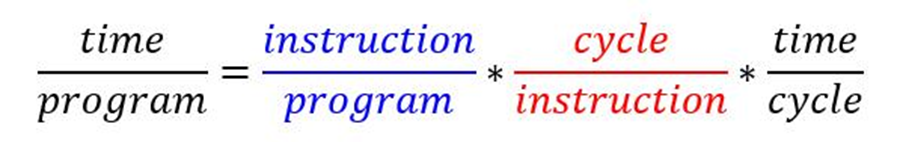

不同品牌的CPU,其产品的架构也不相同,例如,Intel、AMD的CPU是X86架构的,而IBM公司的CPU是PowerPC架构,ARM公司是ARM架构。同时,不同的芯片厂商按照指令集的设计情况分为精简指令集和复杂指令集。 那么不同的指令集有啥不同的? 不同的指令集决定着CPU的处理方式。从指令集角度来看,CPU的效率主要通过两种思路来提升:要不通过降低每个程序所需的指令数来提升效率,要不通过降低每条指令所需的时间周期数来提升效率。

CISC更偏重前者,而RISC更侧重后者。目前来看,CISC指令集较为复杂,提供了丰富的指令,能够减少程序员的编程工作量。 然而,随着计算机科学的发展,人们发现这种复杂性会导致处理器的性能和能效下降。因此,RISC应运而生,它采用了一种更简单、更高效的设计理念,通过优化指令集,提高处理器的性能和能效,成为21世纪以来所有新兴领域的绝对主流。 说了这么多,大家可能云里雾里,下面我们通过让大家了解下举例来说明下不同指令集的工作原理: 拿做饭来说,要完成做饭这个动作。

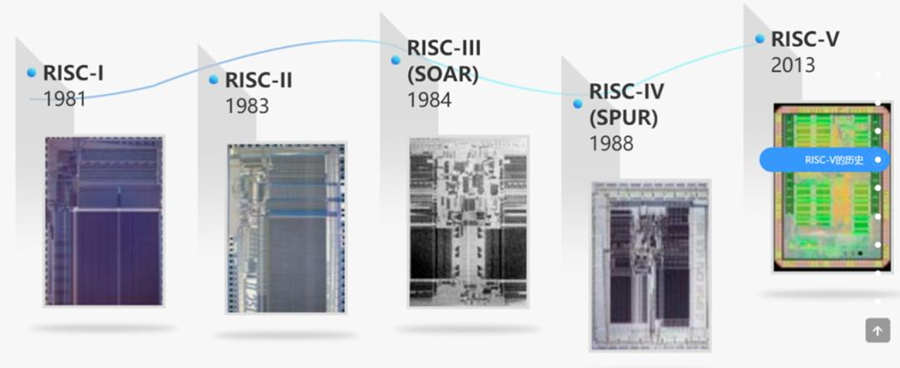

精简指令集需要定义做饭中的每个动作,需要包含拿钱、拿篮子、买菜、买面、烧水、和面、炒菜等指令。程序要完成做饭这个指令,需要下达这些指令来合成做饭这个动作,否则程序不知道该怎么做。对于CPU来说,每条指令都很简单 复杂指令集则不需要知道这么多指令,只需要下达做饭这个指令即可,很简单。下单完做饭指令,程序会直接完成全部的动作。但是对于CPU来说,每条指令都很复杂。 那么为啥我们不都用复杂指令集呢?一条命令就可以轻松完成一整套动作?因为,有一些时候,人们只想完成"和面"这一个步骤,我只想"和面",那么在复杂指令集中则没有这个指令,你必须来一套这样的动作,这也导致复杂指令集的CPU在一些专用的领域的性能和能效下降。 所以不同指令集的的指令是不可以通用的,即使是相同阵营的指令集,每家的指令也是不同的。例如英特尔可能用"111"表示做饭,AMD则可能用"666"表示买菜。因此,CPU和指令集不同,导致相关产业生态不同。 ▉ RISC-V的诞生 聊完指令集,我们了解到,不同的架构反映了设计者对同一功能的不同实现思路。在之前,X86、ARM芯片架构一直是用户采用最多的两种芯片架构。 但是X86被英特尔和AMD封闭使用、ARM要收取高昂的授权费用…… 因此,20世纪80年代初,加州大学伯克利分校的David Patterson、斯坦福大学的John L. Hennessy等学者开始尝试对传统的CISC进行精简, RISC便由此诞生,信息技术史上浩浩荡荡的CISC与RISC之争拉开帷幕。 第一代处理器 RISC-I是1980年在伯克利 Dave Patterson 教授主导Berkeley RISC项目中设计而成,就是今天RISC架构的基础。随后,Dave Patterson 教授又在1983年发布RISC-II原型架构,在1984年发布RISCI-III架构,在1988年发布RISC-IV架构。 在这个过程中,RISC的设计理念催生一系列新架构如MIPS、IBM PowerPC以及现在统治嵌入式市场的ARM。 在21世纪初期,受当时开源运动在操作系统和应用软件领域取得了巨大成功(如Linux和Mozilla)的影响,为开源芯片设计带来了崭新的前景。

时间来到2010年,当时加州大学伯克利分校的科研团队正在为一个新项目做准备,在调研了x86,ARM等现有指令集后,于是决定重新设计了一套全新的指令集。在这样的背景下,RISC-V(即第五代精简指令集计算机)作为开源芯片的代表,正式诞生了。

RISC-V 这个名字,代表了 UC Berkeley 大学设计的第五代RISC芯片。同时罗马数字"V"也暗示 了"变种(Variations)"和"向量(Vectors)",以支持各种体系结构研究,包括各种数据并行加速器,也是这个 ISA 设计的明确目标。 起初,学术界对于RISC-V的技术创新性持怀疑态度,学者们认为这不属于伯克利分校的教授们的工作,所以,RISC-V在一级学术会议上并不受到关注。直到伯克利团队将RISC-V从概念推进到原型芯片,并在2015年成立了非盈利组织--RISC-V基金会,历经大量的技术研讨会后,于是,RISC-V慢慢受到大众的关注和认可。 ▉ RISC-V哪里不一样? 那么RISC-V具有什么显著特点和优势呢?今天我们就来看下:

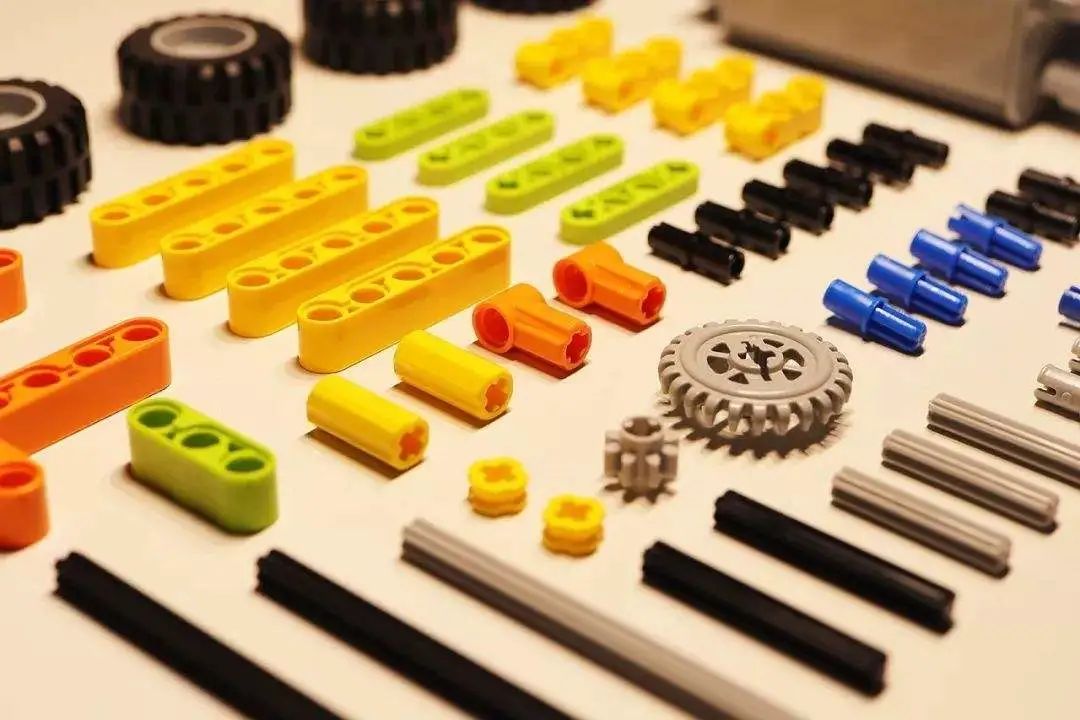

(1)完全开源(自由、免费、可控) 开源意味着自由、免费、可控。对于 RISC-V 指令集的使用,RISC-V基金会不收取高额的授权费。开源采用宽松的BSD 协议,企业可以完全自由免费使用,同时也允许企业添加自有指令集,而不必开放共享,实现差异化发展。而且不必担心某一天像X86、ARM芯片架构一样,很容易被限。 (2)架构简单(没有历史包袱) 与X86和ARM这两大成熟架构相比,RISC-V架构具备显著的后发优势。计算机架构经过多年演进,更趋于成熟,许多问题已被研究透彻,作为后来者的RISC-V架构可以自然而然的加以规避。同时,没有向后兼容的历史包袱。直观地说,X86和ARM架构的指令多达数千条,而RISC-V架构仅需100余条指令。此外,简洁的架构方案还可有效减少错误发生(毕竟CPU流片成本是极高的)。 (3)模块化设计(像乐高一样灵活选择)

RISC-V 架构不仅短小精悍,其不同的部分还能以模块化的方式组成在一起,从而试图通过一套统一的架构满足各种不同的应用场景。用户能够灵活选择不同的模块组合,来实现自己定制化设备的需要,比如针对小面积低功耗嵌入式场景,用户可以选择RV32IC 组合的指令集,仅使用Machine Mode(机器模式);而高性能应用操作系统场景则可以选择RV32IMFDC 指令集,使用 Machine Mode(机器模式)与User Mode()户模式)两种模式。 ▉ RISC-V的应用场景有哪些? 由于不同指令集的特点。精简指令集的RISC-V和ARM都有很好的低功耗特性,适合用于嵌入式系统、物联网设备、移动设备等低能耗场景。X86则比较高功耗,适合用于高性能计算、云计算、大数据分析等高能耗场景。 目前,市场上RISC-V已经在多个领域和场景中得到广泛应用: 物联网(IoT) 物联网设备通常对功耗和成本有严格的要求,而RISC-V凭借其高能效和灵活性成为了这一领域的理想选择。在今年6 月 27 日,中国移动正式发布全球首颗纯自研 RISC-V 架构的 LTE-Cat.1 芯片和移动首颗纯自研量产的蜂窝物联网通信芯片,他们分别是CM8610 LTE-Cat.1和CM6620 NB-IoT,两者在功耗,计算性能,射频性能上都非常优异。

往后RISC-V架构会被广泛应用于物联网时代,其内置的模块化设计可以很好地满足低功耗嵌入式设备需求。再加上开源免费的优势,让RISC-V成为未来潜力无限的物联网架构平台。 人工智能(AI): RISC-V架构提供人工智能需要的高性能处理器,同时也可以被设计为支持向量处理器(Vector Processor),提供更高的并行计算能力,优化不同的机器学习算法和应用程序。

边缘计算(Edge) 边缘计算需要在设备端进行实时数据处理,对处理器的性能和能效有较高要求。RISC-V的简洁高效设计使其成为边缘计算的理想选择。 移动设备: RISC-V处理器可被优化为节能模式,以延长移动设备的电池寿命。同时,基于RISC-V架构的灵活性,处理器可以被定制以满足特定的应用需求,提供高性能和低功耗的优点。 服务器: RISC-V架构提高性能和改善能效比,从而降低数据中心的能源和运营成本。其也可以被设计为多核处理器,提供更高的并行计算能力和更好的负载均衡。RISC-V的开放性和灵活性也使得处理器可以满足不同的特定的服务器应用需求。 开发者社区与教育 由于RISC-V的开放性,全球的开发者和研究人员都可以参与到其生态建设中来。许多大学和研究机构已经将RISC-V纳入教学和研究计划,培养下一代硬件工程师。同时,也有越来越多的开发者社区和活动围绕RISC-V展开,推动技术交流和创新。 不仅如此,由于RISC-V架构的开放性、灵活性和适应性使它成为全球芯片设计者的首选之一。研究机构Counterpoint Research的数据显示,到2025年,RISC-V在IoT市场占有率将达到28%,在工业市场的占有率将达到12%,在汽车市场的占有率将达到10%。 ▉ RISC-V的挑战 当然,要实现广泛的市场应用,目前RISC-V还有许多挑战需要面对: 首先是生态建设。尽管RISC-V已经取得了一定的进展,但其生态系统仍然相对落后于其他主流指令集架构,如ARM和x86。要实现广泛的市场应用,RISC-V需要在软件兼容性、开发工具、操作系统等方面加强生态建设。

其次是技术成熟度。虽然RISC-V在部分领域已经取得了一定的成功,但在一些高性能计算场景下,其技术成熟度仍然不足。要在更激烈的市场竞争中取得优势,RISC-V需要在性能、功耗和成本等方面进一步优化。 第三,在商业模式与合作方面。由于RISC-V的开放性,企业在使用和发布RISC-V产品时需要面临一定的商业挑战。要实现可持续发展,RISC-V需要探索适合自身的商业模式,并与全球的合作伙伴共同推进技术创新和市场应用。 ▉ 国内RISC-V机遇与挑战 在中国政府芯片自主可控战略的推动下,许多中国企业已开始研发和生产基于RISC-V架构的芯片,RISC-V架构将逐渐成为中国芯片设计和制造领域的重要一步,帮助中国在芯片开发和生态建设方面取得成就。

目前,国产芯片制造商对RISC-V架构的积极参与已经取得了一系列显著的进展。华为、阿里巴巴、等知名企业都在积极研发RISC-V芯片,他们的加入为RISC-V架构的发展带来了更多的可能性和机遇。 例如,华为自主研发的麒麟处理器中就使用了RISC-V指令集架构。这种积极投入不仅提升了中国芯片制造商在国际舞台上的竞争力,也加速了RISC-V生态系统的形成和完善。相信随着更多中国芯片厂商的加入,RISC-V架构将在未来发展趋势中展现出更为蓬勃的生机与潜力。

下面我们来看下RISC-V芯片对国内发展有一定影响重要事件: 2018 年9 月 中国RISC-V 产业联盟宣布成立,截至2020 年5 月,拥有123 家会员单位。 2018 年11 月 中国开放指令生态(RISC-V)联盟宣布成立,由倪光南院士担任联盟理事长。 2018 年11月 RISC-V 基金会中国顾问委员会宣布成立。 2019 年7月 阿里巴巴平头哥发布高性能玄铁910 RISC-V 处理器。 2019 年8月 兆易创新发布全球首个基于RISC-V 内核32 位通用MCU。兆易创新携手本土RISC-V 处理器内核IP 芯来科技面向物联网联合开发了该MCU 处理器内核。 2020 年3月 基金会总部从美国搬迁到瑞士。基金会宣称搬迁是基于持续保证对开源技术和软件的支持以及规避可能带来的政治风险等诸多因素的综合考量的决定。 2023年8 月,2023 RISC-V 中国峰会在京开幕,中国工程院院士倪光南,RISC-V 国际基金会 CEO 卡莉斯塔?雷德蒙德,峰会主席、中国科学院软件研究所副所长武延军,中国科学院计算技术研究所副所长包云岗出席峰会开幕式并致辞,卡莉斯塔·雷德蒙德在大会上做了主旨报告。 从最初的没几家, 到现在几十家, 我这汇总一下当前正在RISC-V设计方向创业的公司(或者团队),方便大家参考,顺便感受下国内在这个方向的研发热度。排名不分先后,数据来源于网络,如有遗漏错误欢迎留言补充。 1.奕斯伟(原京东方董事长王东升):自研RISC-V core,SoC,北京 2.蓝芯(原字节CPU负责人卢山):自研高性能RISC-V core,北京 3.嘉楠科技:自研RISC-V core,北京 4.中科睿芯(中科院计算所范东睿):自研RISC-V core,北京 5.中科声龙(中科院计算所博后汪福全):自研RISC-V core,北京 6.腾讯:自研RISC-V core,深圳 7.字节:自研RISC-V core和ARM Soc 8.百度:自研RISC-V core,北京 9.阿里平头哥:自研RISC-V core和ARM Soc 10.赛防中国:自研RISC-V core IP,北上 11.芯来科技:自研RISC-V core IP,北上武汉 12.进迭时空(原阿里平头哥910团队):自研高性能RISC-V core,杭州,北京 13.海思:自研RISC-V core,ARM core,SoC,北上深、西安等 14.微核芯:自研RISC-V core,北京 15.开源芯片研究院(中科院计算所):自研RISC-V core,北深 16.希奥端(原海思网络):ARM SoC+自研RISC-V core,北深 17.超睿科技:自研RISC-V core,上海 18.算能科技:自研RISC-V core,北京 19.旭日辰芯(原Intel中国总裁杨旭):自研RISC-V core, 北京 20.隼瞻科技:自研RISC-V core, 南京 21.睿思芯科(RISC-V团队谭章熹):自研RISC-V core, 深圳 22.奥维领芯(塞昉SoC team联创):自研RISC-V core和SoC, 北京 23.群芯闪耀科技(海光子公司):自研RISC-V core, 北京 24.华米科技:自研RISC-V IoT CPU 25.紫光展锐:自研RISC-V core,北京 26.中兴通讯:自研RISC-V core,深圳 27.兆易创新:自研RISC-V core,北京 28.中科院:自研RISC-V core,北京 29.智原科技:自研RISC-V core,上海 30.海光:自研RISC-V core,北京 31.飞利信:自研RISC-V core,北京 32.乐芯:自研RISC-V core,上海 33.沁恒:自研RISC-V core,南京 34.中微半导体:自研RISC-V core,深圳 35.瑞萨电子:自研RISC-V core,北京 36.中科蓝讯:自研RISC-V core,深圳 37.核芯互联:自研RISC-V core,北京 38.汇顶科技:自研RISC-V core,深圳 数据统计,包括IP内核与芯片设计等主要内容在内,中国目前有300家以上公司在关注RISC-V或以RISC-V指令集进行开发。 然而,尽管RISC-V架构值得我们对其未来充满信心,但也不可避免地会有人对其做出一些担忧和质疑。其中一个主要的担忧是RISC-V作为一个开源项目,是否会面临知识产权的风险。因为各个芯片厂商可以自由使用、设计和制造RISC-V芯片,这在某种程度上可能造成技术泄漏和知识产权不受保护的问题。 目前来看,RISC-V基金会作为负责管理和维护RISC-V生态系统的组织,一直在致力于为RISC-V架构提供良好的法律和商业支持。此外,开源社区的概念本身就意味着共同协作和保护,通过广泛的参与和集体智慧,可以更好地保护RISC-V的知识产权。因此,在RISC-V生态系统的发展中,合理和有效的知识产权保护可以得到保障。 在中国芯片企业的押注和全球范围内的积极参与下,RISC-V架构在中国的发展前景可观,而与此同时,存在的一些担忧也需值得关注。 所以,很多人认为RISC-V不会受到断供的影响,并且其开源和自由的特性将为其未来的发展奠定坚实基础。重要的是,我们应该保持对RISC-V的积极关注,并在发展中保持开放、合作的态度,共同推动中国芯片产业的创新与发展。 ▉ 总结: 展望未来,国产芯片借助RISC-V指令集有望摆脱对ARM的依赖,实现自主可控。随着RISC-V生态系统的不断完善和国内芯片厂商的不断努力,我们有理由相信,未来RISC-V将在中国的芯片领域有更大的应用空间和市场份额。同时,这也将推动我国在芯片领域的自主创新能力的提升,促进整个产业的健康发展。 在这个充满竞争的时代,RISC-V指令集的崛起无疑给了中国芯片产业一次难得的发展机遇。让我们期待国产RISC-V芯片的更多亮相和更好表现! |

【本文地址】