| 通过Cadence设计及验证,实现了LVS和DRC检查的Cadence两级放大电路版图设计 | 您所在的位置:网站首页 › virtuoso版图设计规则如何修改 › 通过Cadence设计及验证,实现了LVS和DRC检查的Cadence两级放大电路版图设计 |

通过Cadence设计及验证,实现了LVS和DRC检查的Cadence两级放大电路版图设计

|

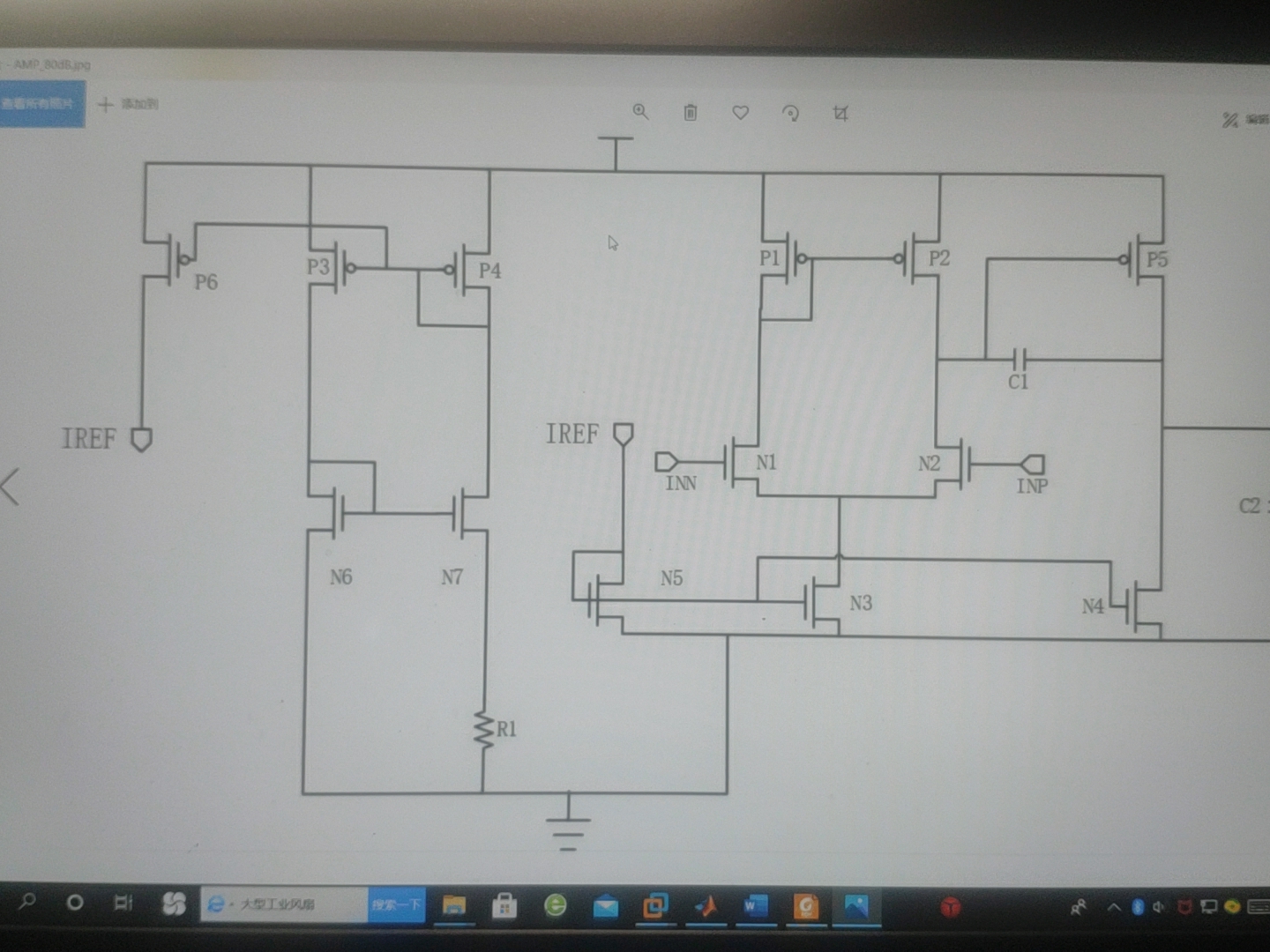

Cadence 两级放大电路,包括版图,已通过lvs ,drc检查 Cadence两级放大电路已经完成版图设计,并且已经通过了LVS(Layout vs. Schematic)和DRC(Design Rule Check)的检查。 在这段话中涉及到的知识点和领域范围是电路设计和集成电路设计工具。电路设计是指通过选择和配置电子元件,将它们连接在一起以实现特定功能的过程。而集成电路设计工具是用于设计和验证集成电路的软件工具,其中Cadence是一个常用的集成电路设计工具。 延申科普:集成电路设计是现代电子技术中的重要领域,它涉及到将多个电子元件(如晶体管、电容器、电阻器等)集成到单个芯片上,以实现各种功能。集成电路设计工具是帮助工程师进行电路设计和验证的软件工具,它们提供了各种功能和模块,包括原理图设计、版图设计、模拟仿真、验证和布局布线等。 Cadence是一个知名的集成电路设计工具供应商,他们提供了一系列的软件工具,包括用于原理图设计的Capture、用于版图设计的Virtuoso、用于模拟仿真的Spectre等。这些工具能够帮助工程师进行电路设计、验证和优化,提高电路设计的效率和可靠性。 LVS(Layout vs. Schematic)和DRC(Design Rule Check)是集成电路设计中常用的验证步骤。LVS检查用于验证版图和原理图之间的一致性,确保版图中的电路结构和原理图设计是一致的。DRC检查用于验证版图设计是否符合制造工艺的规则,确保版图中的电路布局满足制造要求。 通过使用Cadence这样的集成电路设计工具和进行LVS、DRC等验证步骤,工程师可以更好地设计和验证电路,确保其功能正确性和制造可行性。这些工具和验证步骤在集成电路设计中起到了关键的作用,帮助工程师提高设计质量和效率。 YYID:22230656670067817 小p

Cadence两级放大电路是一个重要的电路设计项目,它包括了版图设计和通过了LVS和DRC的检查。电路设计是指通过选择和配置电子元件,将它们连接在一起以实现特定功能的过程。而集成电路设计工具则是用于设计和验证集成电路的软件工具。Cadence作为一个常用的集成电路设计工具,提供了一系列的软件工具,包括用于原理图设计的Capture、用于版图设计的Virtuoso、用于模拟仿真的Spectre等。 在现代电子技术中,集成电路设计是一个极其重要的领域。它涉及到将多个电子元件集成到单个芯片上,以实现各种功能。集成电路设计工具是帮助工程师进行电路设计和验证的软件工具,它们提供了各种功能和模块,包括原理图设计、版图设计、模拟仿真、验证和布局布线等。 Cadence作为知名的集成电路设计工具供应商,提供了强大的工具和功能,帮助工程师进行电路设计、验证和优化。Capture是一款用于原理图设计的工具,能够帮助工程师快速、准确地绘制电路原理图。Virtuoso则是一款用于版图设计的工具,提供了丰富的布局设计和布线功能,能够帮助工程师将电子元件按照特定的布局进行排列和连接。Spectre是一款用于模拟仿真的工具,可以帮助工程师验证电路的性能和功能。 LVS和DRC是集成电路设计中常用的验证步骤。LVS检查用于验证版图和原理图之间的一致性,确保版图中的电路结构和原理图设计是一致的。DRC检查则用于验证版图设计是否符合制造工艺的规则,确保版图中的电路布局满足制造要求。这些验证步骤对于保证电路设计的准确性和可行性非常重要。 通过使用Cadence这样的集成电路设计工具和进行LVS、DRC等验证步骤,工程师可以更好地设计和验证电路,确保其功能正确性和制造可行性。这些工具和验证步骤在集成电路设计中起到了关键的作用,帮助工程师提高设计质量和效率。在完成了Cadence两级放大电路的版图设计并通过了LVS和DRC的检查后,我们可以有信心地说,该电路的设计是可行的,并且符合制造要求。这对于我们来说是一个重要的里程碑,也为我们未来的集成电路设计项目打下了坚实的基础。 以上相关代码,程序地址:http://wekup.cn/656670067817.html |

【本文地址】