| HLS入门实践 | 您所在的位置:网站首页 › vhdl中的component › HLS入门实践 |

HLS入门实践

|

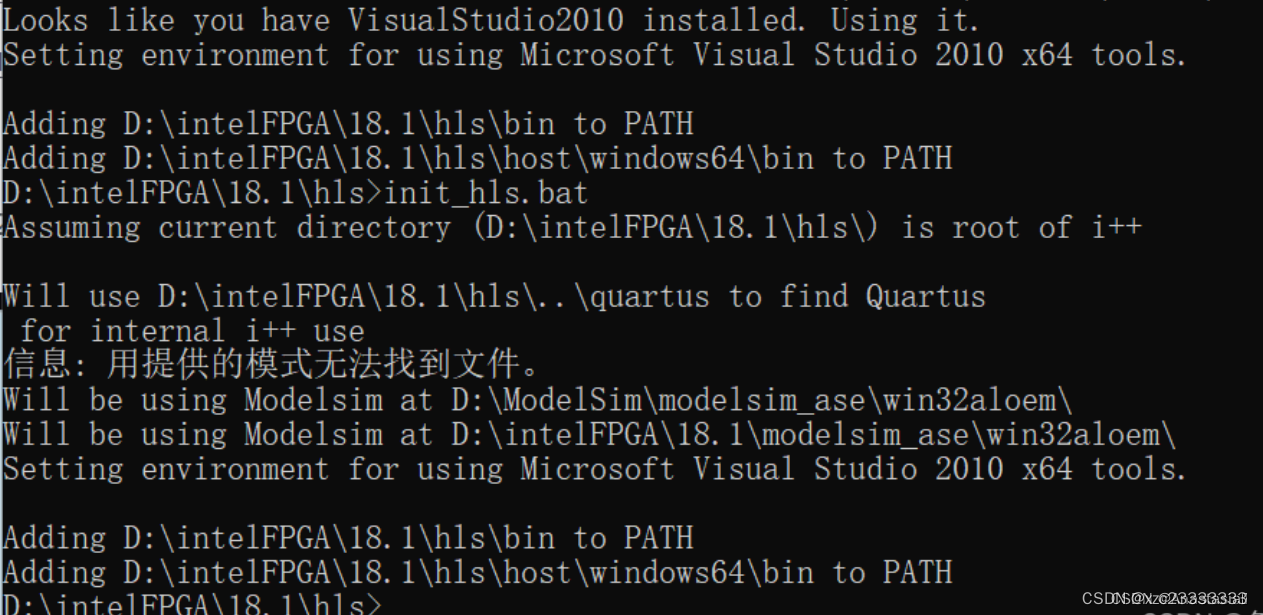

重庆交通大学信息科学与工程学院 《嵌入式系统基础A》课程 实验报告 班 级: 物联网工程2002 姓名-学号 : 谢志聪632007060527 实验项目名称: 重庆交通大学信息科学与工程学院 《嵌入式系统基础A》课程 实验报告(2) 班 级: 物联网工程2002 姓名-学号 : 谢志聪632007060527 实验项目名称: HLS入门实践 实验项目性质: 设计性 实验所属课程: 《嵌入式系统基础A》 实验室(中心): 南岸校区语音大楼 指 导 教 师 : 娄路 完成时间: 2023 年 5 月 18 日 一、实验内容和任务 HLS是什么?与VHDL/Verilog编程技术有什么关系? HLS有哪些关键技术问题?目前存在什么技术局限性? 在win10(或者Ubuntu系统下)安装 Intel 或者 Xilinx 的支持HLS的FPGA编程开发软件(Quartus18或者Vivado18),设置好环境,完成一个入门级的HLS程序,并进行仿真或者实际开发板运行。 Intel FPGA的HLS实验参考课件资料或网站,如: https://blog.csdn.net/han422858897/article/details/117106846?utm_source=app&app_version=4.7.1&code=app_1562916241&uLinkId=usr1mkqgl919blen Xilinx FPGA的HLS实验,参考: 1)Xilinx 2018.3相关软件工具 链接:https://pan.baidu.com/s/1jkurhTLgnxavgRnmi-JLDA 提取码:sygh 2)Z7-Lite-7010 板卡资料和教程,链接:https://pan.baidu.com/s/1s9o3pKul2eTkDvlHvv3tog 提取码:h49u 3)Z7-Lite-7020 板卡资料和教程,链接:https://pan.baidu.com/s/1owxkcZHvyOPyCfhBmDOBjA 提取码:doiy 4)ZYNQ开发视频教程 链接:https://pan.baidu.com/s/13AkvW0DD1VyU1PcfRlYvxQ 提取码:9fmh 二、实验要求 提交作业markdown文件,项目完整代码 和 博客地址。 三. 实验过程介绍 (此处可以填博客内容) 一、HLS介绍HLS是什么: HLS(High-Level Synthesis)是一种硬件描述语言编程技术,它可以将高级语言(如C/C++)转换为硬件描述语言(如VHDL或Verilog),以便将其用于FPGA(Field-Programmable Gate Array)或ASIC(Application-Specific Integrated Circuit)的设计中。 HLS技术在FPGA和ASIC的设计中非常有用,因为它可以帮助设计人员通过高级语言编写硬件逻辑,从而提高设计效率和可重用性。HLS技术还可以提供比传统的手动编写硬件描述语言更高的抽象级别,使得设计人员可以更快地开发出功能复杂的硬件系统。 HLS与VHDL/Verilog编程技术有什么关系: VHDL和Verilog是传统的硬件描述语言,用于手动编写硬件逻辑。与HLS技术相比,它们需要更多的时间和精力来编写和调试代码,但也提供了更高的灵活性和控制力。HLS技术和VHDL/Verilog编程技术可以结合使用,以便在设计过程中兼顾效率和灵活性。 HLS的关键技术 HLS(High-Level Synthesis)是一种复杂的技术,存在一些关键技术问题和技术局限性。以下是一些主要问题和限制: 高层次综合的优化问题:高层次综合包括多个优化阶段,如数据流分析、资源映射、调度和寄存器分配等。这些优化阶段的顺序和参数设置会对设计的性能、面积和功耗等方面产生影响,需要合理的算法和工具支持。 精度问题:由于高层次综合基于软件编程语言,因此需要考虑精度和舍入误差等问题。例如,浮点数运算会产生舍入误差,而整数运算可能会导致溢出或截断等问题。 时序约束问题:在设计硬件时,时序约束是非常重要的,因为它们可以确保电路的正确性和可靠性。高层次综合需要能够自动生成正确的时序约束,以确保设计的正确性。 可维护性和调试问题:由于高层次综合生成的硬件电路是自动生成的,因此很难进行调试和维护。开发人员需要有有效的工具和技术来检测和调试电路中的错误。 HLS的技术局限性 目前存在一些技术局限性,如: 支持的软件编程语言:目前,高层次综合支持的软件编程语言有限,大多数工具支持C/C++和SystemC等语言。因此,开发人员需要在这些语言中编写硬件描述。 复杂性:高层次综合涉及多个优化阶段和复杂的算法,需要大量的计算资源和时间。因此,它对硬件层面的知识和经验要求较高。 可移植性:高层次综合生成的电路可能会受到工具和目标平台的限制,因此需要进行定制化和优化。这可能会限制电路的可移植性和可重用性。 成本问题:高层次综合需要使用专业的工具和硬件平台,这可能会增加开发成本和时间。 二、环境搭建在win10(或者Ubuntu系统下)安装 Intel 或者 Xilinx 的支持HLS的FPGA编程开发软件(Quartus18或者Vivado18),设置好环境,完成一个入门级的HLS程序,并进行仿真或者实际开发板运行。 1、初始化打开系统命令管理器cmd,定位到init_hls.bat的路径,并运行 d: cd D:\intelFPGA\18.1\hls init_hls.bat

在D盘新建文件夹prj(英文路径下就可以),创建test.cpp,编写如下乘法器代码: #include “HLS/hls.h” #include “stdio.h” component int mul(int a,int b) { int c =0; c = a*b; return c; } int main() { int a=0,b=0,c=0,i=0; for(i=0;i |

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |

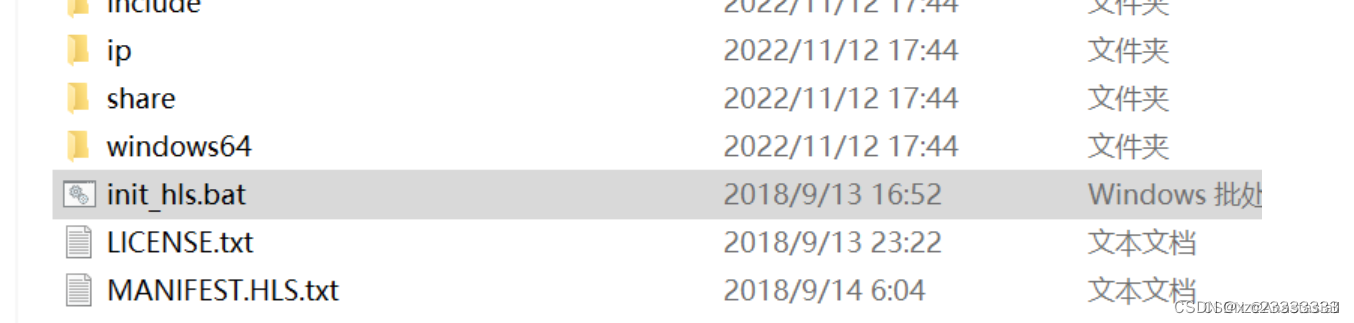

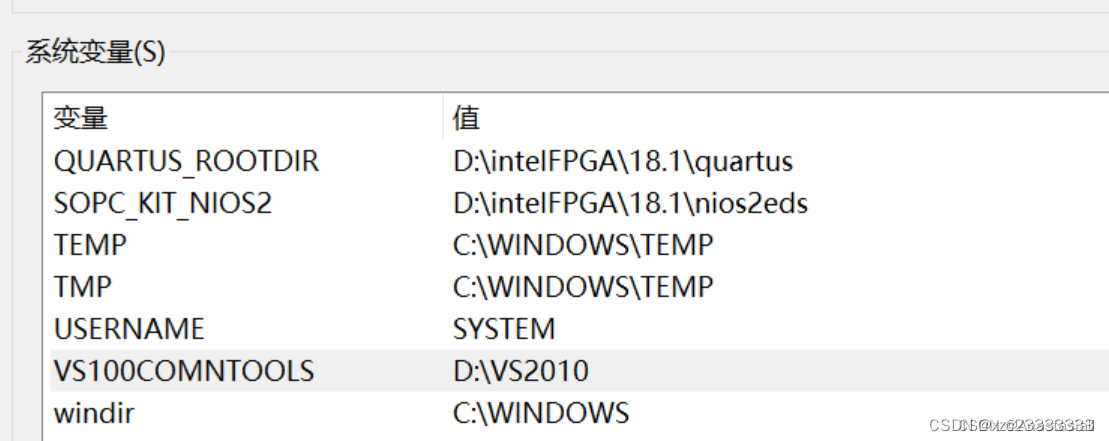

查看路径和环境变量,找到init_hls.bat

查看路径和环境变量,找到init_hls.bat