| 【FPGA学习笔记】Verilog语言的模块化设计 | 您所在的位置:网站首页 › verilog模块结构主要包括 › 【FPGA学习笔记】Verilog语言的模块化设计 |

【FPGA学习笔记】Verilog语言的模块化设计

|

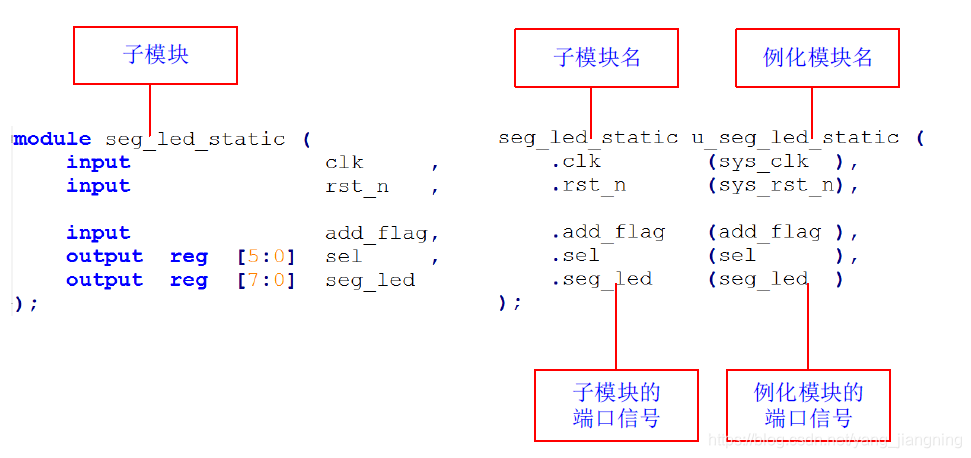

在进行模块化设计中,对于复杂的数字系统,我们一般采用自顶向下的设计方式。可以把系统划分成几个功能模块,每个功能模块再划分成下一层的子模块;每个模块的设计对应一个module,一个module设计成一个Verilog程序文件。因此,对一个系统的顶层模块,我们采用结构化的设计,即顶层模块分别调用了各个功能模块。 一、以下以静态数码管显示实验为例简单介绍。 1、底层模块1(计时模块) module time_count( input clk; input rst_n; output reg flag; ); //parameter define parameter MAX_NUM =25000000;//计数器最大值 ... endmodule2、底层模块2(数码管静态显示模块) module reg_led_static( input clk; input rst_n; input addr_flag; output reg [5:0] sel; output reg [5:0] sel_led; ); ... endmodule3、顶层模块对以上两个模块进行例化。 module seg_led_static_top( input sys_clk; input sys_rst_n; output sel; output sel_led; ); //parameter difine parameter MAX_SHOW = 25'd25000000; wire addr_flag; //*****main code**** //计时器模块例化 time_count #( .MAX_NUM (MAX_SHOW) )u_time_count( .clk (sys_clk), .rst_n (sys_rst_n), .flag (addr_flag) ); //数码管显示模块例化 reg_led_static u_reg_led_static( .clk (sys_clk), .rst (sys_rst_n), .addr_flag (addr_flag), .sel (sel), .sel_led (sel_led) );二、小结 |

【本文地址】

公司简介

联系我们