| Verilog各类分频器设计详解 | 您所在的位置:网站首页 › verilog实现三分频 › Verilog各类分频器设计详解 |

Verilog各类分频器设计详解

|

Verilog各类分频器设计详解

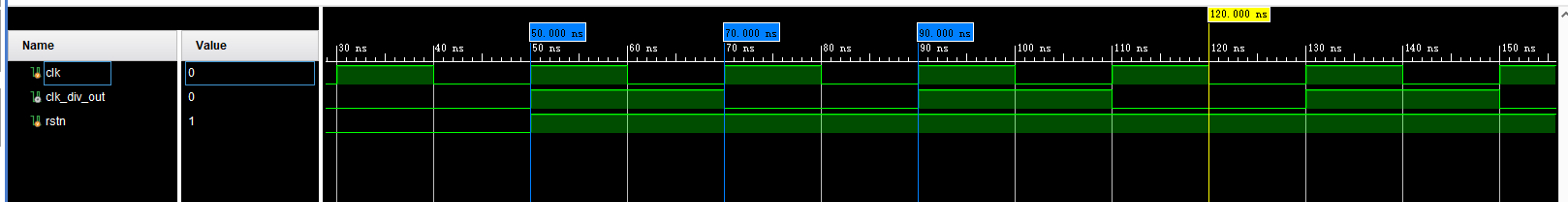

分频器是时序电路的基本器件,它的功能是对系统时钟或其他时钟进行分频产生所需要的时钟信号。分频有两种方式:一是通过HDL语言建模产生所需要的时钟信号,二是利用开发工具的PLL进行分频。前者分频灵活,需编写代码实现;后者使用场景受限,因为有的低端FPGA没有PLL,但PLL的分频效果更好,而且在进行小数分频时也比较容易实现。本文首先尝试用HDL语言建模方式设计各种类型的分频器,最后给大家简单介绍一下PLL的使用。如有不足之处还望大家批评指正。 偶数分频器我们先从最简单的偶数分频器切入,慢慢分析各种分频器的实现。 若要实现二分频,则只需要在原时钟的上升沿进行输出时钟状态的翻转即可,如下图所示

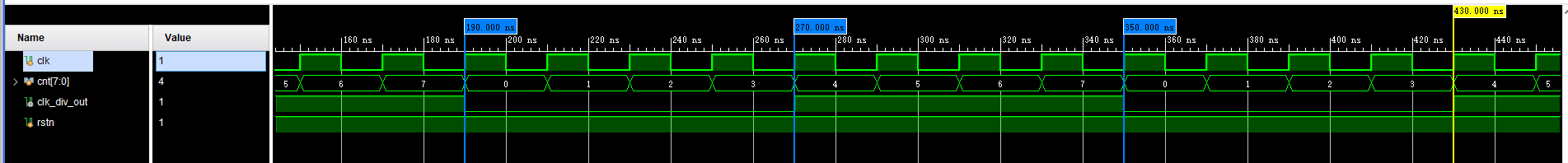

若实现四分频呢?则需要一个计数器,每次在原时钟的上升沿计数,当计数器记到2个上升沿时输出时钟状态进行翻转,如下图所示

现在对一般情况进行分析,对时钟进行N分频,N为偶数;则计数器每次在原时钟的上升沿计数,计数器的范围为0-(N-1),我们可以在0-(N-1)这N个数中分出两个范围选择输出时钟的状态,如当cnt在0-M范围时输出时钟为低电平,当cnt在(M+1)-(N-1)范围时输出时钟为高电平,则我们可以动态调整输出时钟的占空比,输出时钟的占空比为(N-M-1)/N;

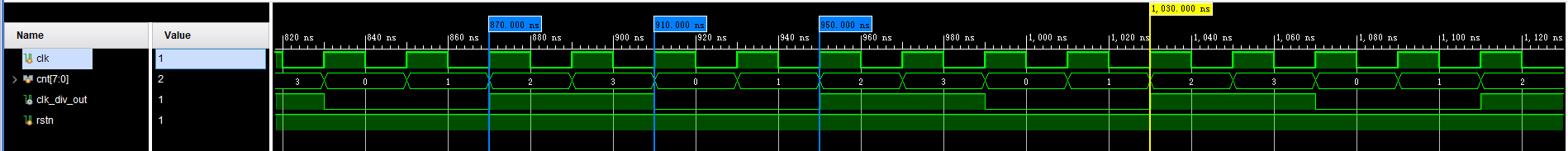

以8分频为例,则N=8,取M=3,则此时输出的时钟应当是50%占空比,如下图所示

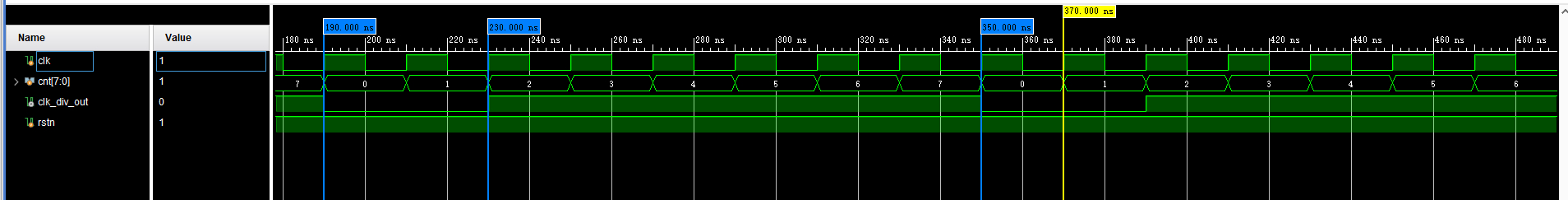

若取M=1,则此时输出时钟的占空比应当是75%,如下图所示

偶数分频器代码 // 偶数分频器示例,可调占空比 module clk_div_even( input wire clk, //系统时钟 input wire rst_n, //异步低电平复位 input wire [7:0] clkperiod, //分频系数,N(偶数)分频时clkperiod=N input wire [7:0] clklow, //低电平占用系统时钟的周期数 //占空比为50%时clklow=N/2 output reg clk_out //输出时钟 ); reg [7:0] cnt; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin cnt |

【本文地址】

公司简介

联系我们