| 学会使用Hdlbits网页版Verilog代码仿真验证平台 | 您所在的位置:网站首页 › verilog仿真波形图怎样与代码对应 › 学会使用Hdlbits网页版Verilog代码仿真验证平台 |

学会使用Hdlbits网页版Verilog代码仿真验证平台

|

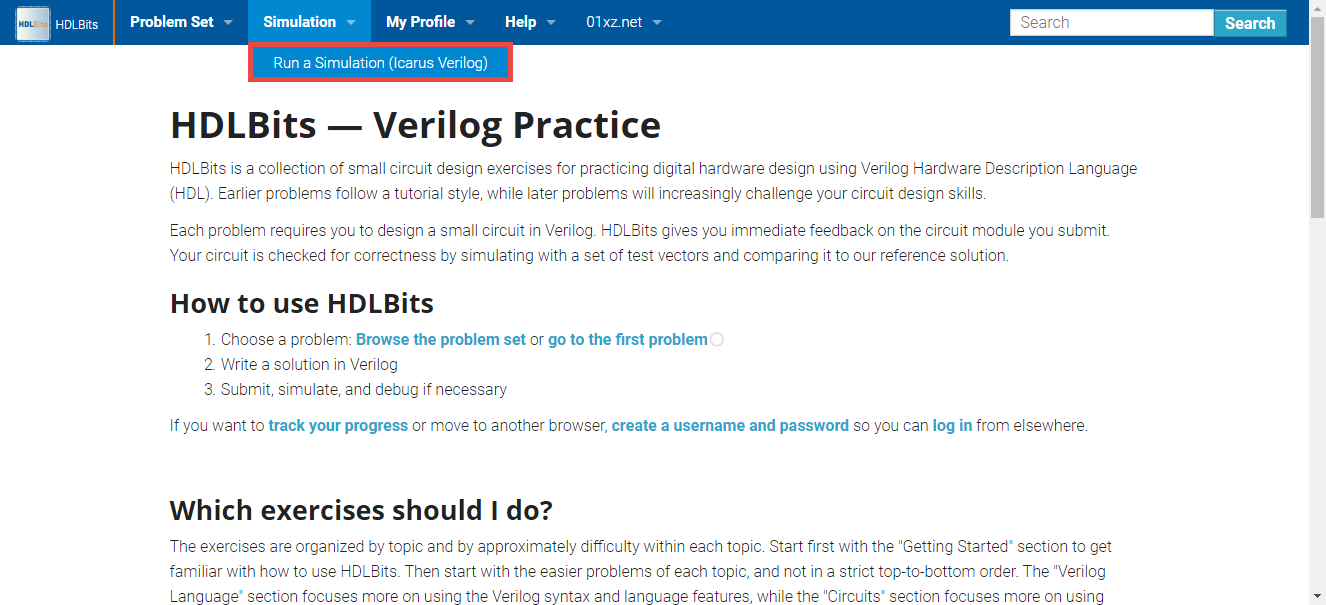

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进入网页,在该网页上可以进行Verilog代码的编写、综合,而且最后还能够仿真出波形来验证设计代码的正确性,该验证平台是基于Icarus Verilog(简称iVerilog,比较著名的开源HDL仿真工具,也有对应的安装版本)的,让你随时随地只需登录网页就能够享受Verilog编程仿真的乐趣! 一、官方模板演示1、首先打开“https://hdlbits.01xz.net/wiki/Main_Page”,打开后的界面如下图所示,全英文显示。如果感觉自己的英文水平欠佳,可以使用谷歌浏览器打开该网页,并选择在线翻译功能,翻译的正确率还是很高的。 2、点击Simulation下的 ”Run a Simulation(lcarus Verilog)“。 3、打开后的界面如下图所示,代码编辑框中给出了一个简单的例子。

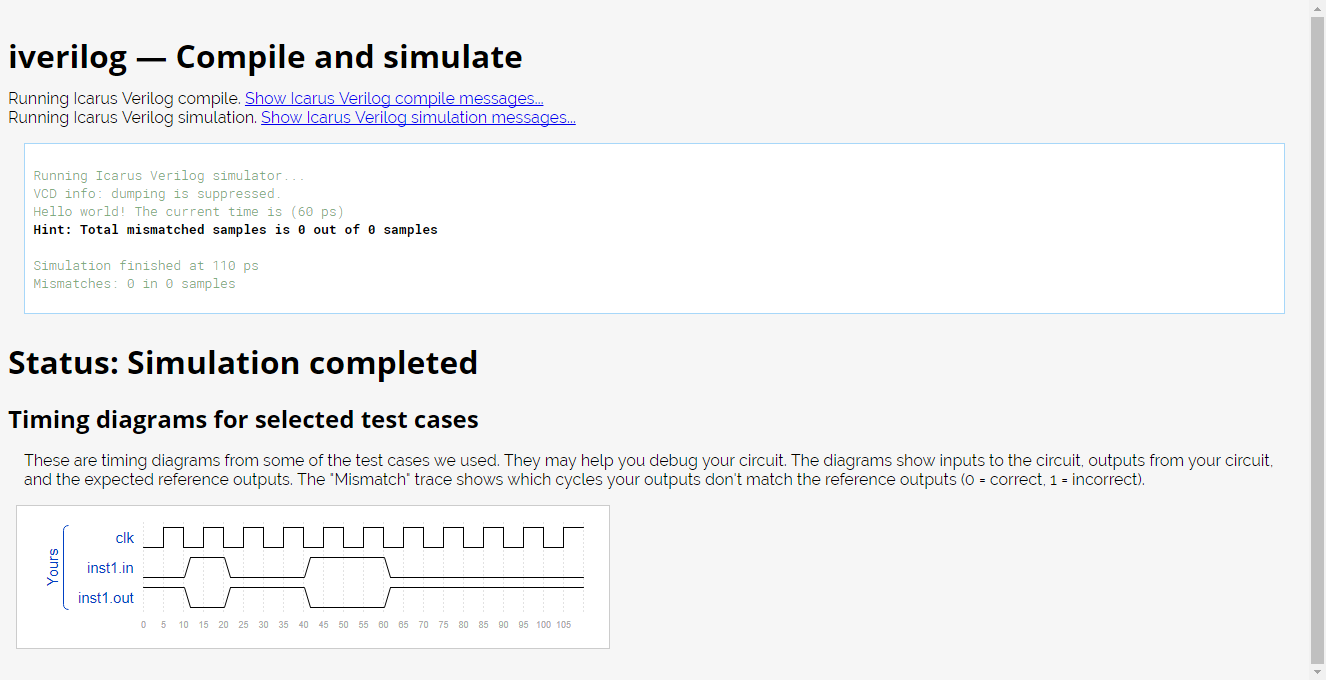

4、点击下面的“Submit(new window)“在新界面中进行仿真。 5、在新打开的界面中我们可以看到编译的信息和仿真波形图。 虽然看完了官方的模板演示,但我们要想立刻仿真验证自己设计的代码并不是那么容易,需要进行一番摸索。下面就是大家进行一个呼吸灯的设计实例演示。 1、学习过FPGA的朋友都知道要想对FPGA逻辑进行仿真一定要具备两个文件,一个是RTL代码文件,用来综合生成硬件电路的部分;第二个就是Testbench文件,用来验证RTL代码功能的仿真文件,这两者缺一不可。 2、根据观察发现官方模板中的代码编辑部分有两个module,大家也都知道一个.v 文件中只能有一个模块,也就是只能有一个module,而这里面有两个,那肯定就不对了。再仔细观察会发现代码编辑区域中的上半部分就是Testbench,而下半部分则是RTL代码,再结合仿真出的波形来更看验证了这个想法。原来 RTL 代码和Testbench都写在了一个编辑框里。 3、但是我们在提供的模板中发现一些我们平时几乎没有见过的新语法,如第4行的”initial `probe_start“、第6行的”`probe(clk)“、第26行的”`probe(in)“,通过模板的注释和多次实验发现这是官方定义的一个”宏“,也就是通过这个”宏“调用“probe”探针的功能,我们不用管这个”宏“是如何定义的,我们只需要会调用就可以了。 4、下面我们通过该网页来仿真验证一下自己设计的呼吸灯的例子。详细代码如下(呼吸灯逻辑和Testbench代码的编写方法这里我们不做讲解,会在以后的文章中再进行详细说明),下面代码可以全部直接复制使用(代码中的注释请详细阅读)。 1 `timescale 1ns/1ns 2 3 //----------------Tesebench----------------- 4 module top_module; //仿真文件名必须是“top_module” 5 6 reg sclk; 7 reg rst_n; 8 9 wire led; 10 11 initial `probe_start; // Start the timing diagram 12 13 `probe(sclk); // Probe signal "clk",这是加载的系统时钟,只能在Tesebench中加载 14 15 //初始化 16 initial begin 17 sclk = 1'b0; 18 rst_n |

【本文地址】