| 差分布线 USB3.0布线设计 | 您所在的位置:网站首页 › usb接口设计规范最新 › 差分布线 USB3.0布线设计 |

差分布线 USB3.0布线设计

|

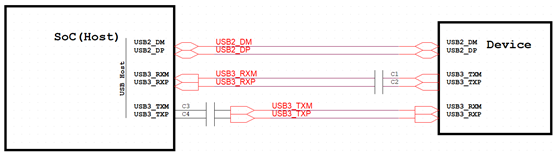

原文链接:https://blog.csdn.net/lwjun/article/details/92574928 USB 3.0硬件设计 概述 USB3.0相比2.0在硬件物理连接上有较大的改变,采用的是RX/TX全双工链路设计,由2对差分信号组成,同时向下兼容USB2.0,所以整个接口有3对差分信号,分别为USB3_RXM/USB3_RXP,USB3_TXM/USB3_TXP,USB2_DM/USB2_DP,USB3.0的传输速率可达到5Gbps,相比USB2.0 480Mbps有比较大的提供。 硬件原理设计 如下图,为USB3.0的Data数据连接原理图,从电路上可以看是USB2.0为半双工,数据收发在一对差分信号上传输。USB3.0为全双工,收发信号为独立的传输路径;其次,由于Sink端的直流偏置电压和source端的直流偏置电压不一样,故要需要串入AC耦合电容,电容一般取100nF,一般靠近驱动端放置,电容在设计上要求ESR ESL(特别重要)尽量小。

USB 3.0的Host的RX连接到Device Tx,Host的Tx连接到Device的 Rx,类似于我们常用的UART接口的连接。 PCB Layout设计 硬件连接上相对比较简单,最终需要PCB Layout设计来保证信号的完整性,接下来从PCB层叠结构、阻抗控制、走线要求等细节上说明USB3.0的设计的注意事项 1. PCB层叠结构要求 以下是4层板的层叠结构图,可通过Si9000计算出差分对所约束的线宽线距。 对于PCB阻抗线的定义,受那些物理参数影响,请自行查阅相关

2. USB差分阻抗控制要求 参考USB PHY手册,基于上图的层叠结构,计算出差分信号所要求的线宽线距,本文为ASM1153 为例进行阐述: ASM1153为USB 3.0转Sata接口的桥芯片,要求USB 3.0的差分阻抗为85欧,USB2.0为90欧,差分对等长公差在 +/-5mil。

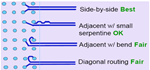

3. PCB走线要求 5Gbps的速率需要以高速线的设计规则来严格把关走线,充分考虑PCB的设计细节 3.1 PCB出线要求尽可能平等出差,具体走线参考下图:

3.2 走线换层需要在信号过孔旁边增加地过孔,用于信号的回流(高速通用规则) 3.3 USB信号测试点的放置建议如下图,“一”字形放置在路径上,非Y字形或T字形放置,并且测试焊盘如果走线不连续的较大焊盘,请将相邻层的GND层垂直于测试焊盘掏空,避免出现影响信号的寄生电容或等效电容。测试点的焊盘尺寸,应尽可能的小,如果必需要放置测试点的话,比照0402封装的焊盘尺寸或直接将测试点放置在信号线的过孔上。

3.4 关于等长匹配蛇形线的走线方式,建议按下图方式走线

3.5 USB3.0 的P/M如果走线上有交差,可以将差分对的P/M交换,USB3允许P/M反转 |

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |