| [UCAS] 超大规模集成电路与系统设计(080902M04002H)作业参考 | 您所在的位置:网站首页 › spice语句描述 › [UCAS] 超大规模集成电路与系统设计(080902M04002H)作业参考 |

[UCAS] 超大规模集成电路与系统设计(080902M04002H)作业参考

|

Assignment 1

1. Give a formal or descriptive definition for each of the following terms. ITRS, Gate-Equivalent, Technology Nodes, Feature size, IC design complexity sources, Behavioral representation, Abstraction hierarchy, IC design, Synthesis, Refinement, System-level synthesis, Logic synthesis, Layout synthesis, Digital design space, Static timing analysis, Behavioral simulation, Post place and route simulation, Composition-based approach, Design Technology Co- Optimization (DTCO) Mask synthesis解: ITRS是International Technology Roadmap for Semiconductors的缩写,即国际半导体技术路线图。该技术路线图规划了在关键年份的工艺节点、电源电压、MOSFET的阈值电压、氧化层厚度和芯片中集成的晶体管数量。 Gate-Equivalent等效逻辑门。由于二输入与非门中的晶体管数量为4个,因此4个晶体管被等效为1个逻辑门。 Technology Nodes工艺节点,指集成电路加工过程中的特征尺寸。 Feature size特征尺寸,大约是最小晶体管长度的一半。也可以指集成电路中的金属半节距(metal half-pitch),即从上一个金属互连起点到下一个金属互连起点的一半距离,其用来衡量晶体管集成密度。 IC design complexity sources主要有(1)芯片中的晶体管数量越来越多,功能越来越复杂;(2)晶体管参数的随机误差及可靠性问题;(3)随着晶体管尺寸的减小,静态功耗问题越来越严重;(4)非均匀性问题。 Behavioral representation行为域描述,是把电路看作黑匣子,将其输出描述为输入和时间的函数。 Abstraction hierarchy抽象层次,是一系列互相关联的电路描述级别,用它可以描述电路不同方面的细节。 IC design是多次地从电路的一个描述域转变为另一个描述域(综合),直到这个电路可以被制造出来。 Synthesis综合,是电路描述从一个域转变为另一个域的过程。 Refinement细化,是电路从高抽象层次到低抽象层次的转化。 System-level synthesis系统级综合,将任务级的设计规范映射为多种硬件或软件架构。 Logic synthesis逻辑综合,将行为域的数据流描述转变为结构域的逻辑门描述。 Layout synthesis版图综合,将结构域的逻辑门描述转变为几何域的版图描述。 Digital design space按照一些客观的准则,将设计划分为一些更小的模块。 Static timing analysis静态时序分析,根据时序模型计算每条路径的延迟时间,而不需要测试向量。 Behavioral simulation行为仿真,不考虑逻辑门的延时,验证电路功能是否正确。 Post place and route simulation布局布线后仿真,引入布局布线后的寄生参数的仿真。 Composition-based approach利用IP来设计电路的方法。这种方法更多地考虑深入的系统级设计、软硬件协同设计和验证、在所有层次验证所设计的电路以及需要谨慎地使用这些外部的IP。 Design Technology Co- Optimization (DTCO)设计工艺协同优化,是可以让工艺厂商在先进工艺发展中节省成本和上市时间的方法学。它可以使客户可以评估和选择新的晶体管结构、材料和其他工艺参数,以提升电路的功耗、性能和面积性能指标。 Mask synthesis掩膜版综合,由用于开发和批量使用模型的光刻工具组成,可以进行整个芯片的光学邻近效应矫正、反演光刻和对校正后的芯片版图图形的工艺检查和分析。

2. Access the Internet for information about Daniel D. Gajski's "Y-chart" methodology for integrated circuits design. According to your investigation of the related research papers and/or technical reports, please summarize the "Y-chart" theory, including (1) design representation domains, (2) design abstraction hierarchy and (3) design activities. References must be listed at the end of your report. 解: Y图理论中,电路设计的描述域有3个,分别是功能描述、结构描述和几何描述。功能描述,也称为行为描述,它不体现电路单元的具体实现方法和结构,其通常是站在系统、算法和布尔表达式的角度来纵览全局。结构描述,是连接功能描述和几何描述的桥梁。它是在成本、面积和时序等约束条件下,将功能描述映射为一系列基本单元及其连接关系。但是在结构描述中不体现元器件的物理参数。几何描述,是赋予电路结构以位置、几何尺寸等物理信息。 电路设计的抽象层次有系统级、算法级、寄存器传输级、逻辑级和电路级。系统级和算法级是高层次抽象;寄存器传输级是电路设计最常用的抽象层次,其描述数据是如何在寄存器之间传输;逻辑级关注电路如何用逻辑门和触发器实现;电路级是以晶体管和无源器件为单元,对电路进行抽象。 在Y图中,电路设计的行为过程体现为在图中三个描述域之间的相互转化(综合)和一步一步地从外圈细化至中心(降低抽象层次)。例如,一段RTL代码通过逻辑综合,完成从功能域到结构域的转化;之后,使用自动布局布线工具生成版图,完成从结构域到几何域的转化;在后仿真寄生参数提取时,又完成了从几何域到结构域的转化。 References [1] D. D. Gajski and R. H. Kuhn, “Guest Editor’s Introduction: New VLSI Tools,” IEEE Computer, pp. 11-14, Dec. 1983. [2] Jantsch, S. Kumar, and A. Hemani, “The Rugby Model: A Conceptual Frame for the Study of Modelling, Analysis and Synthesis Concepts of Electronic Systems,” in Design, Automation and Test in Europe Conference and Exhibition, Munich, Germany, pp. 256-262, 1999.

3. Write a summary in Chinese of the paper “A New Era in Advanced IC Design” (in less than 200 characters). 解: 面向Soc设计的关键在于:深入的系统级设计与分析、使用常用工具进行软硬件协同设计与验证、一个可以将逻辑仿真器和高效高产的工具相连的验证环境以及使用咨询服务来填补目前SoC基础设施的空缺。SoC设计者最重要的挑战是对于SoC的验证,但是能够帮助设计者提高验证效率的工具和方法已经找到了。SoC设计者必须更多地依赖早期设计验证方法和软硬件协同验证工具,以便在详细的门级验证之前对设计进行调整和优化。(187字) Assignment 21. Consider a 130 nm technology. Compute the value of VDSAT for the NMOS and PMOS device assuming VGS = 1.2 V, VTn = 0.4 V, VTp = −0.4 V, L = 100 nm. 解: 取电子的临界饱和电场强度

空穴的临界饱和电场强度

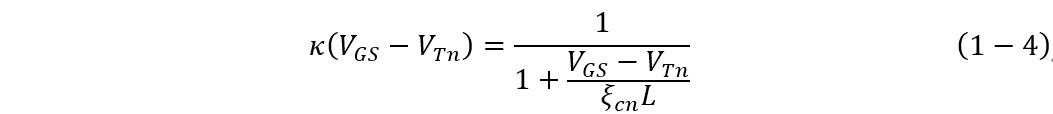

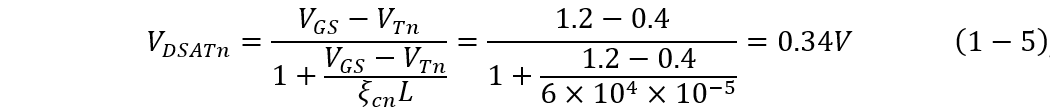

NMOS器件的饱和漏源电压为

其中

将式(1−1)、(1−4)代入式(1−3),得到

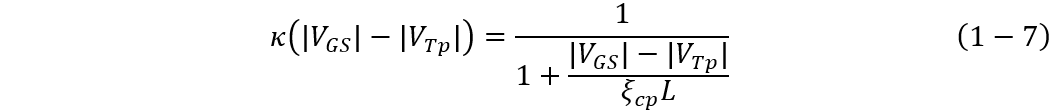

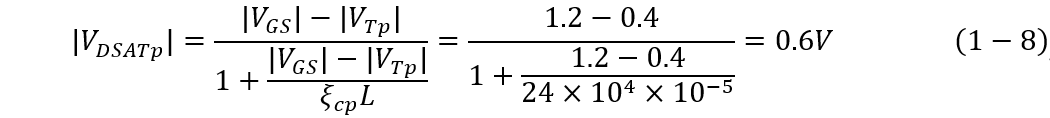

PMOS器件的饱和漏源电压为

其中

将式(1−2)、(1−7)代入式(1−6),得到

即

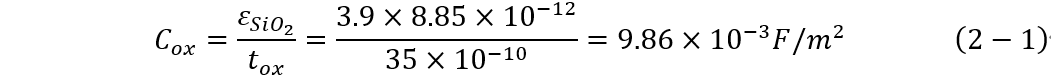

2. Compute the NMOS and PMOS saturation currents per micron of width for a 180 nm technology and the ratio of IDSATN/IDSATP. Assume a channel length of 200 nm, tox =35 Å, VTn= 0.5 V, VTp = −0.5V, VGS = 1.8 V. Use νsat = 8×106 cm/s. 解: 首先计算单位面积氧化层电容

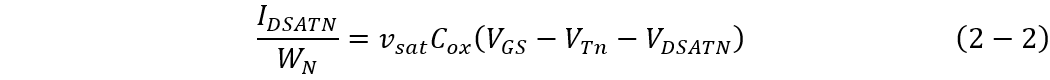

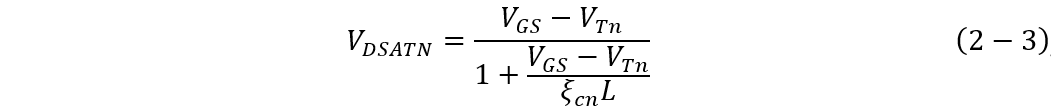

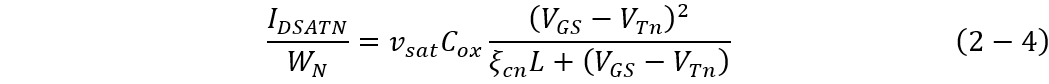

对于NMOS,有

其中

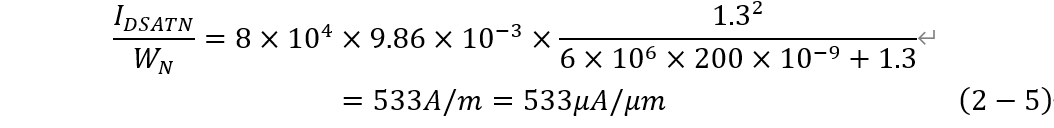

将式(2−3)代入式(2−2),得到NMOS单位沟道宽度上的饱和电流为

代入数据得到

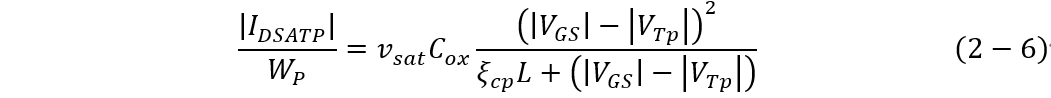

类似地,对于PMOS有

代入数据得到

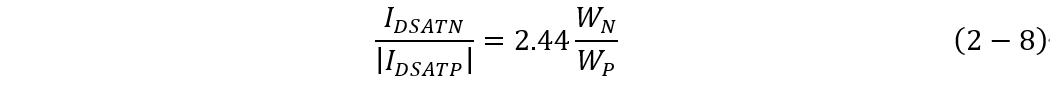

根据式(2−5)和式(2−7),可以得到

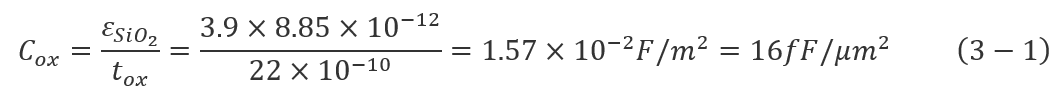

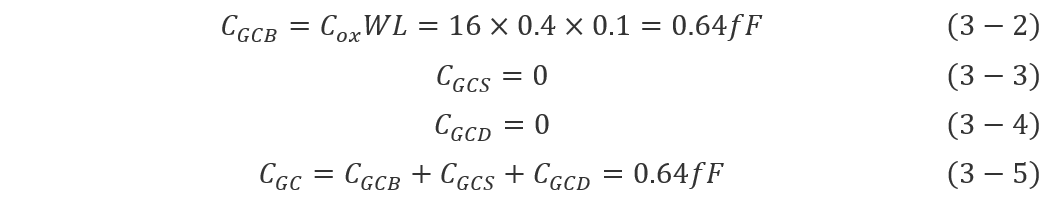

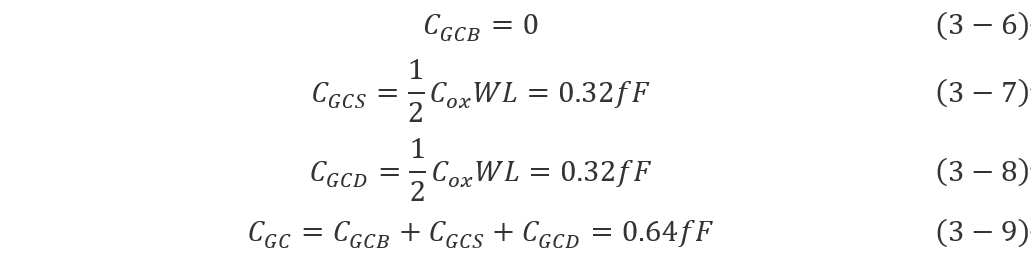

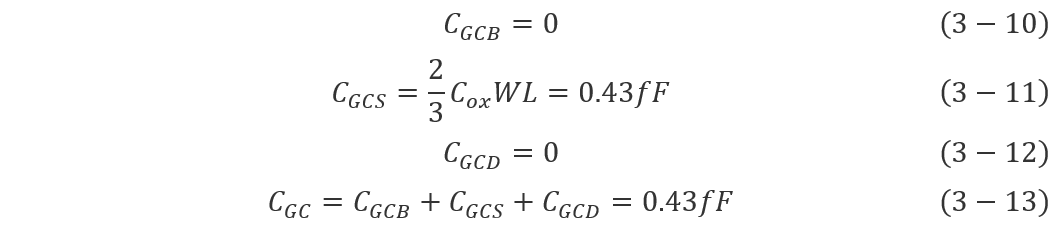

3. Compute the channel capacitance in the cutoff, resistive, and saturation regions required for a NMOS device with tox = 22 Å and W = 400 nm, L = 100 nm. 解: 单位面积的氧化层电容大小为

(1)在截止区中

(2)在线性区中

(3)在饱和区中

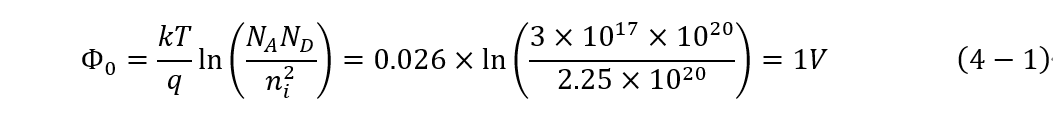

4. Compute the junction capacitance for a 130 nm technology. (a) Find Φ0 and Cjo for an n+p junction with ND = 1020 cm-3 and NA = 3×1017 cm-3. (b) W = 400 nm, L = 100 nm, xj = 50 nm, and the diffusion extension LS is 300 nm. Find Cdiff in unit of fF for VD = 0 V and VD = −1.2 V. Assume Cj = C’jsw. 解: (a)在室温下(T=300K)pn结的内建电势差为

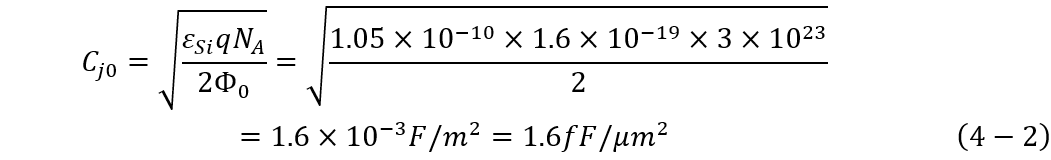

零偏压时的单位面积结电容为

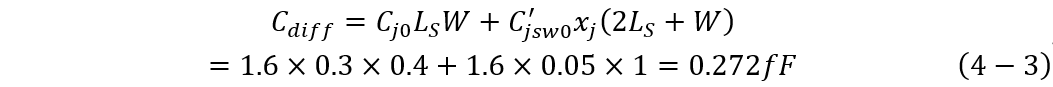

(b)当VD = 0 V时,结电容大小为

当VD = −1.2 V时,

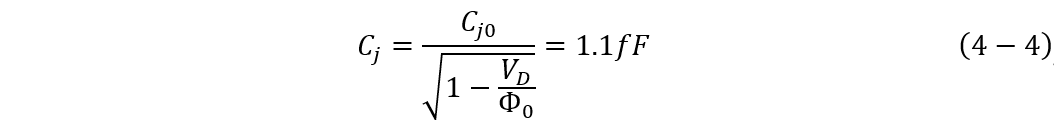

结电容大小为

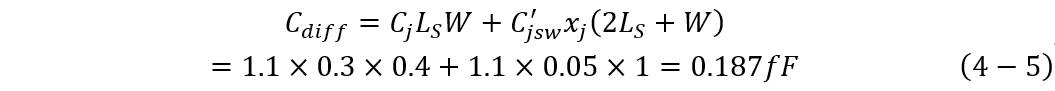

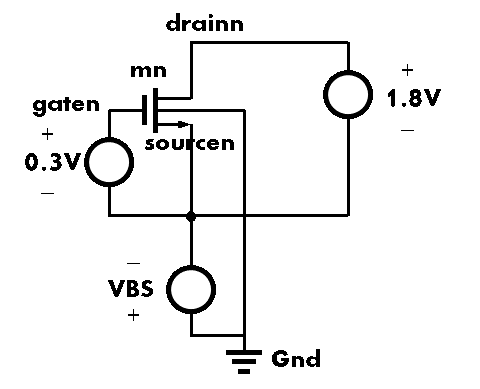

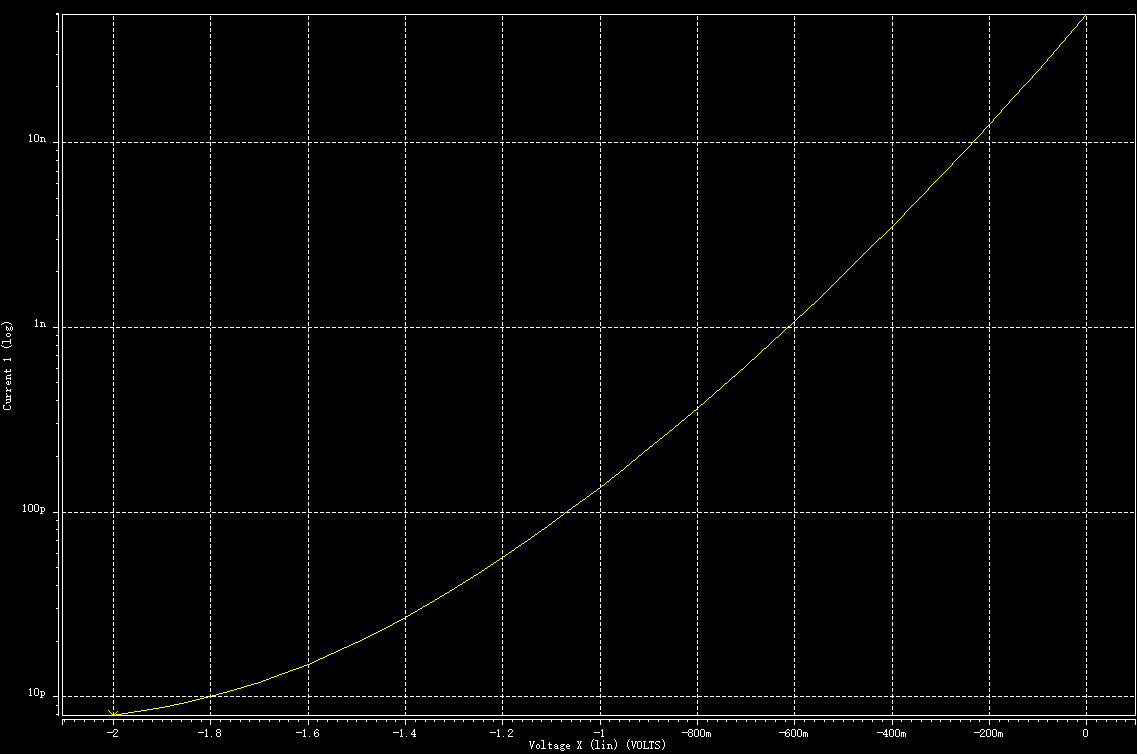

5. Using HSPICE and TSMC 0.18 µm CMOS technology model with 1.8 V power supply, plot the sub-threshold current IDSUB versus VBS, and the saturation current IDSAT versus VBS for an NMOS device with W=400 nm and L=200 nm. Specify the range for VBS as 0 to –2.0 V. Explain the results. 解: 要想控制器件工作是否在亚阈值区,首先要明确其阈值电压。在器件模型文件mm018.l中,可以找到器件子模型nch.12(题中NMOS器件L=200nm,W=400nm,对应的子模型为nch.12)在零衬偏时的阈值电压为VTH0=0.4736658V。用于模拟NMOS器件的亚阈值电流的电路如图5-1所示,其中VGS、VDS均不变,只有VBS改变。因此,只有VBS的变化贡献了电流的变化。 图5-1 用于模拟亚阈值电流的电路图 图5-2 IDSUB与VBS的关系曲线图 在图5-1中,NMOS器件的栅源电压设置为0.3V,小于VTH0=0.4V。在施加非零的VBS后,器件的阈值电压增加,进而保证了VBS在0至−2V的变化范围内,器件始终工作在亚阈值区。模拟程序如下: * SPICE INPUT FILE: IDSUBvsVBS.sp IDSUB-VBS .param Vbsmax=-2 * Set max value of Vbs .lib 'D:\Hspice\tsmc018\mm018.l' TT * Set 0.18um library .opt scale=0.1u * Set lambda mn drainn gaten sourcen Gnd nch l=2 w=4 ad=20 pd=4 as=20 ps=4 Vds drainn sourcen 1.8 Vgs gaten sourcen 0.3 Vbs 0 sourcen dc .dc Vbs 'Vbsmax' 0 'Vbsmax/40' .print dc I1(mn) .end其结果如图5-2所示,图中对纵坐标电流为对数坐标。 从图5-2中可以看出,|VBS|越大,IDSUB越小,这与理论是相符的。在VDS较大时,亚阈值区的电流表达式为 式中,当VTH增大时,IDSUB将会减小,并且lg(IDSUB)-VTH的图像为一条下降的直线。而VTH是VBS的函数,当|VBS|增大时,VTH也相应地增大,但是二者为非线性关系。综上所述,当|VBS|增大时,IDSUB将会减小,lg(IDSUB)-|VBS|为非线性关系。 用于模拟NMOS器件的饱和电流的电路如图5-3所示。和之前模拟亚阈值电流相同,VGS、VDS为常数,只有VBS改变。这样,饱和电流的变化完全是由VBS的变化引起的。从图5-3中不难得出,VDS>(VGS-VTH)κ(VGS-VTH),器件始终工作在饱和区。HSPICE模拟程序如下: * SPICE INPUT FILE: IDSATvsVBS.sp IDSAT-VBS .param Vbsmax=-2 * Set max value of Vbs .lib 'D:\Hspice\tsmc018\mm018.l' TT * Set 0.18um library .opt scale=0.1u * Set lambda mn drainn gaten sourcen Gnd nch l=2 w=4 ad=20 pd=4 as=20 ps=4 Vds drainn sourcen 1.8 Vgs gaten sourcen 1.8 Vbs 0 sourcen dc .dc Vbs 'Vbsmax' 0 'Vbsmax/40' .print dc I1(mn) .end模拟结果如图5-4所示。

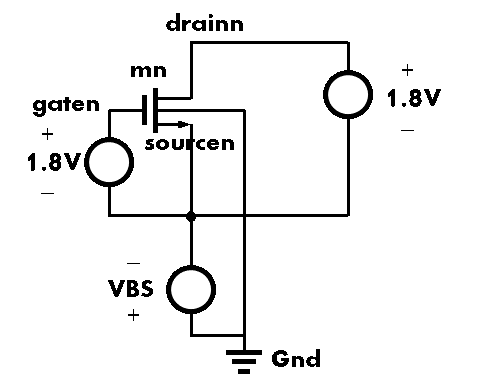

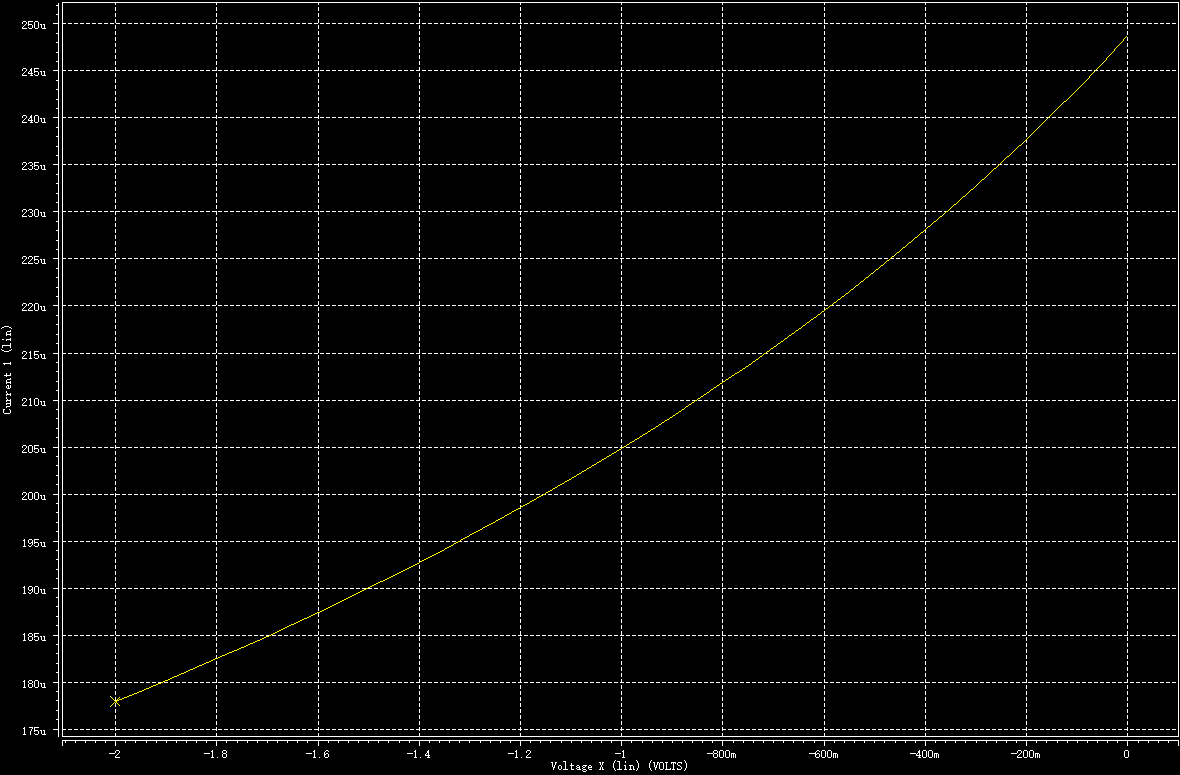

图5-3 用于模拟饱和电流的电路图 图5-4 IDSAT与VBS的关系曲线图 从图5-4中可以看出,随着|VBS|的增大,IDSAT逐渐减小。这是由于VTH随着|VBS|增大而增大,根据饱和区电流公式 可知,VTH越大,IDSAT越小。综上所述,IDSAT随着|VBS|的增大而减小。

6.Using HSPICE and TSMC 0.18 μm CMOS technology model with 1.8 V power supply, plot log IDS versus VGS while varying VDS for an NMOS device with L=200 nm, W=800 nm and a PMOS with L=200 nm, W= 2 µm. Explain the results. 解: 用于模拟题中NMOS与PMOS的转移特性曲线的HSPICE程序如下: * SPICE INPUT FILE: IDvsVGS.sp ID-VGS .param Supply=1.8 * Set value of Vdd .lib 'D:\Hspice\tsmc018\MM018.L' TT * Set 0.18um library .opt scale=0.1u * Set lambda mp drainp gatep Vdd Vdd pch l=2 w=20 ad=100 pd=20 as=100 ps=20 mn drainn gaten Gnd Gnd nch l=2 w=8 ad=40 pd=8 as=40 ps=8 Vdd Vdd 0 'Supply' Vgsp Vdd gatep dc Vgsn gaten 0 dc Vdsp Vdd drainp dc Vdsn drainn 0 dc .dc Vgsp 0 'Supply' 'Supply/40' Vdsp 0 'Supply' 'Supply/8' .dc Vgsn 0 'Supply' 'Supply/40' Vdsn 0 'Supply' 'Supply/8' .print dc I1(mp) .print dc I1(mn) .end其结果如图6-1所示。其中红线为NMOS的模拟结果,黄线为PMOS的模拟结果。在曲线前段(约|VGS|VT2,且VGD2=0 en, up_down => up_down, data => data); -- Clock Generation: GENERATE_CLOCK: process begin wait for (ClockPeriod / 2); clk |

【本文地址】