| FPGA | 您所在的位置:网站首页 › rom和ram最大的区别是rom是只读ram可读可写 › FPGA |

FPGA

|

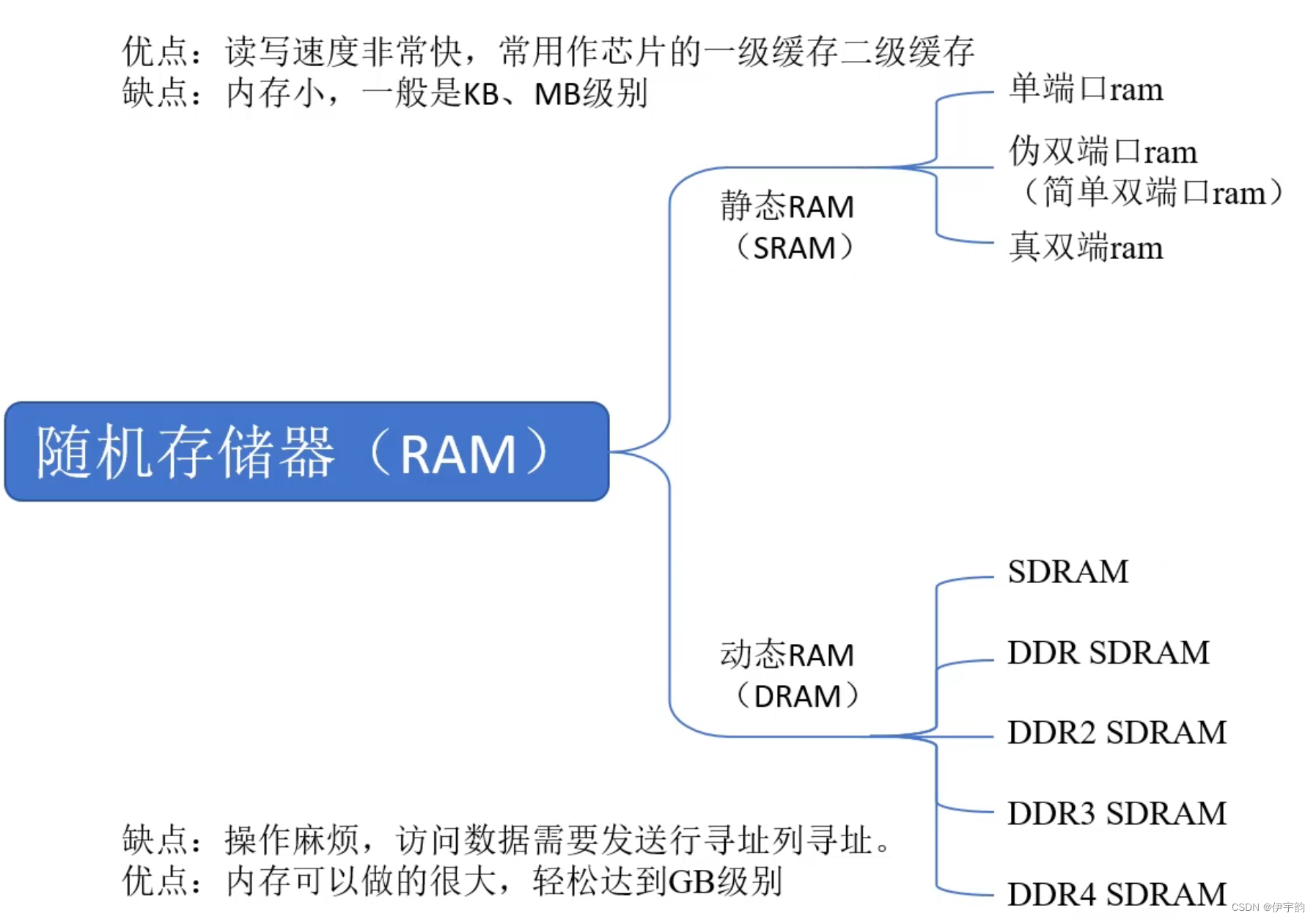

问题 信号源(例如ADC)以1us一个的速率产生12位的数据现要求获得连续1ms内的数据,通过串口以115200的波特率发到电脑。 分析 · 数据量是1000个 · 数据速率不匹配 · 数据内容未知 · 数据总数据量有限 · 数据的使用速度低于数据的产生速度 · 数据生产和消耗的位宽 · 数据量相对较大,数据要求能够重复使用,而且要求能够被更改 RAM:随机存储器(随机获取的存储器,可读可写的存储器)--random access memory 它可以随时把数据写入到任何一指定地址的存储单元。也可以随时从任一指定地址读出数据,其读写速度有时钟频率决定,主要用来存放程序以及程序执行过程中产生的数据,运算结果等 rom的预先存储 ram的实时写入

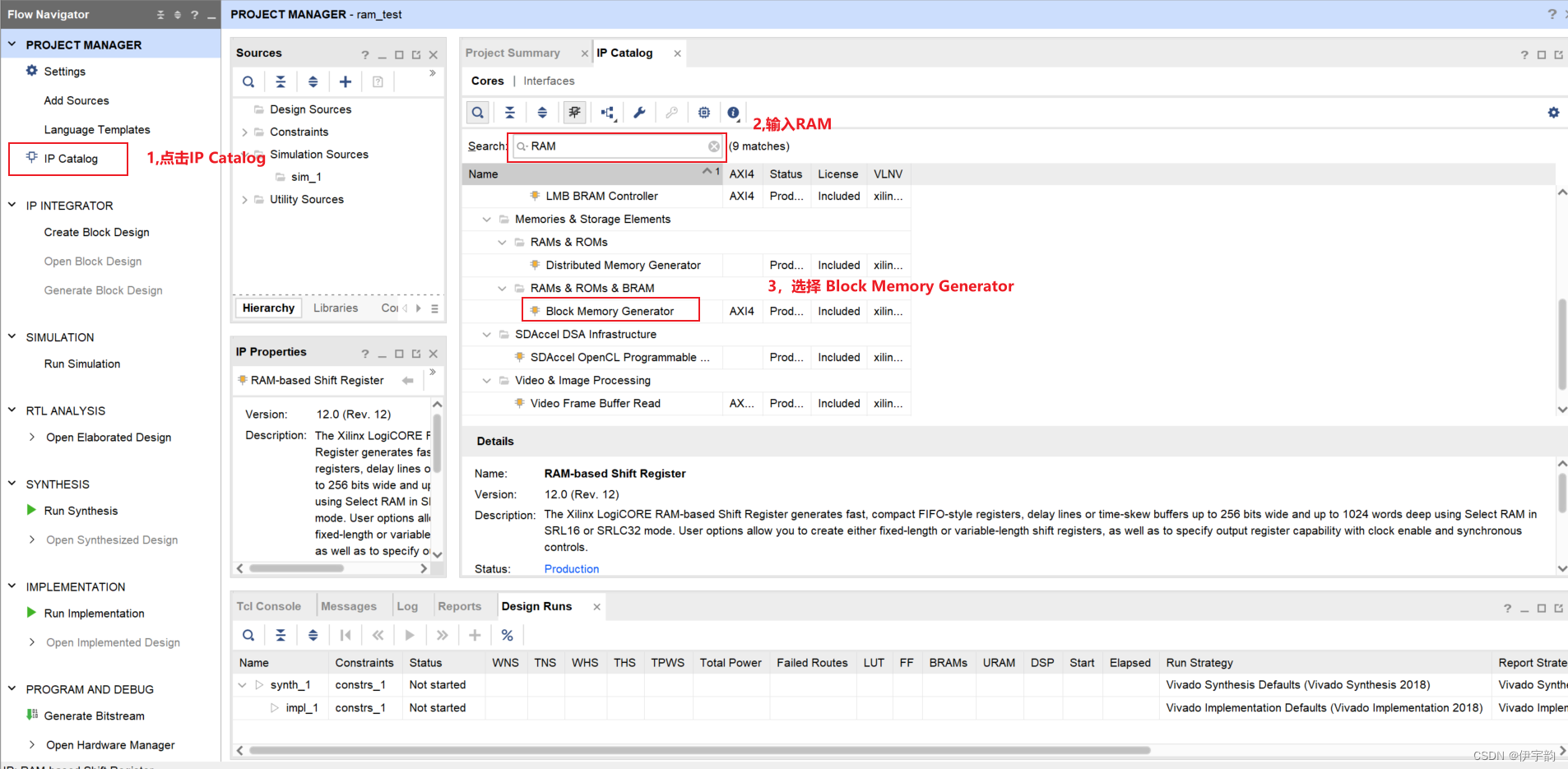

接下来 我们在Vivado中如何实现RAM IP核。 创建工程,进入Vivado界面

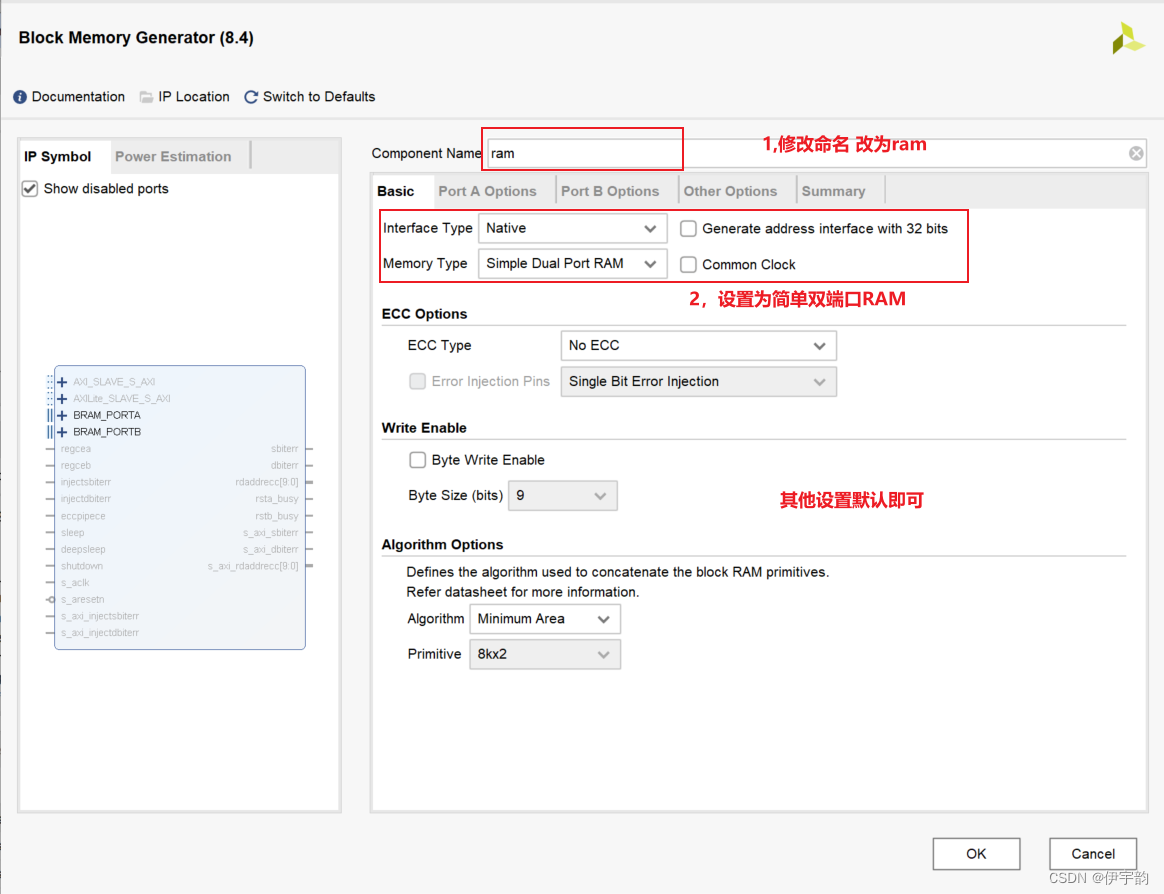

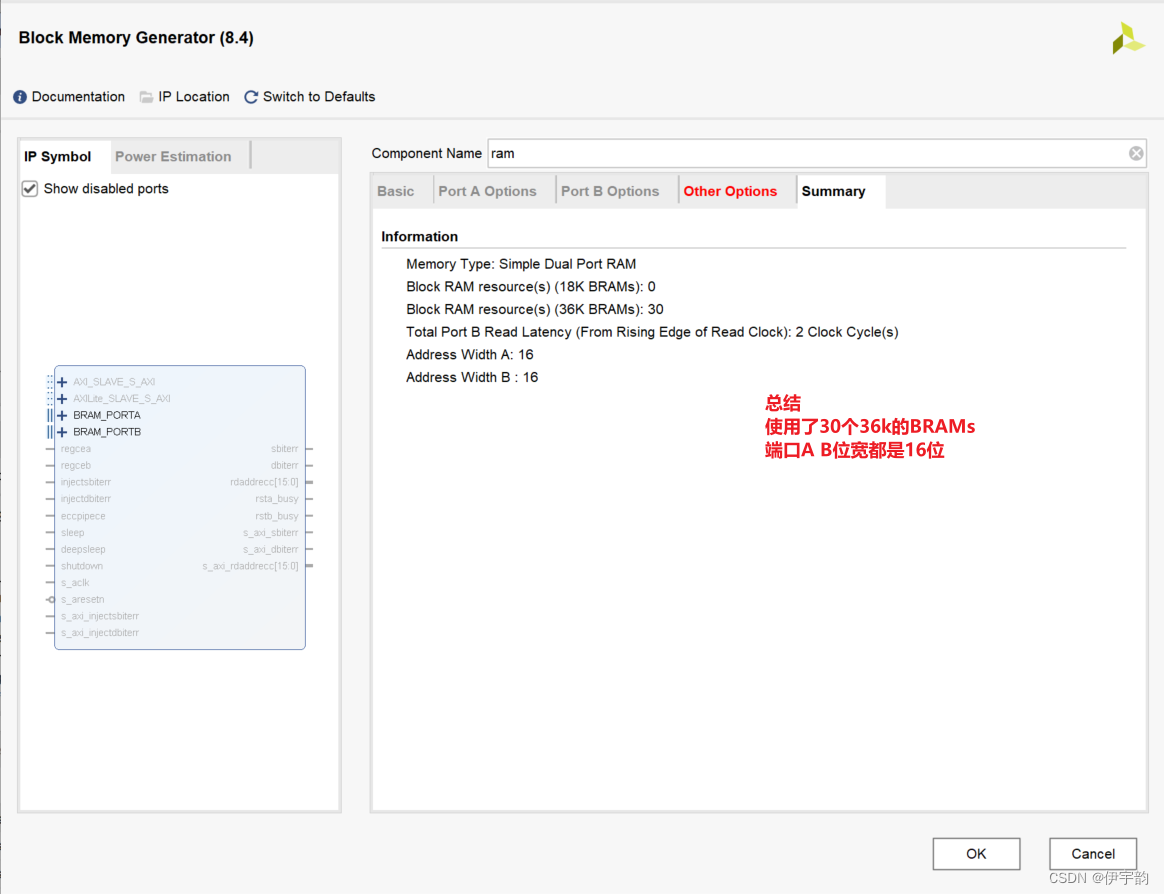

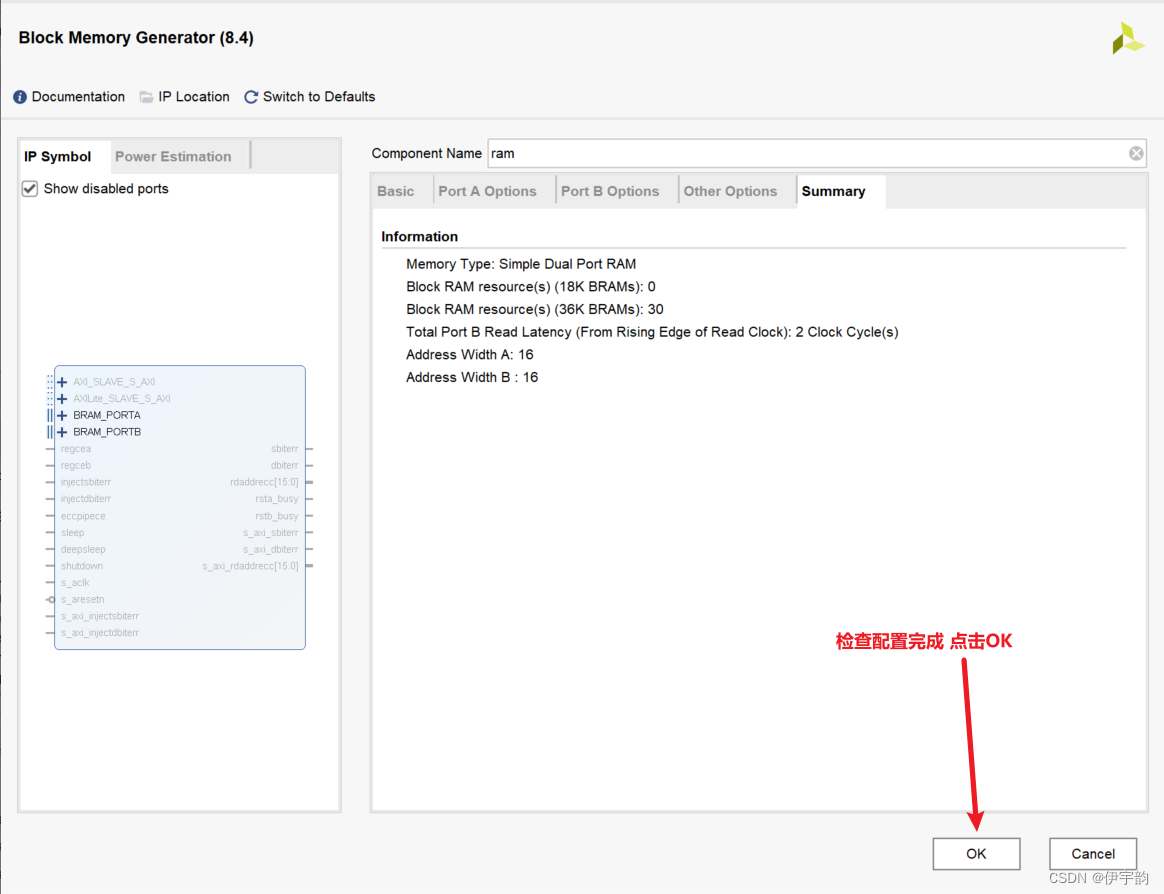

创建RAM IP 核

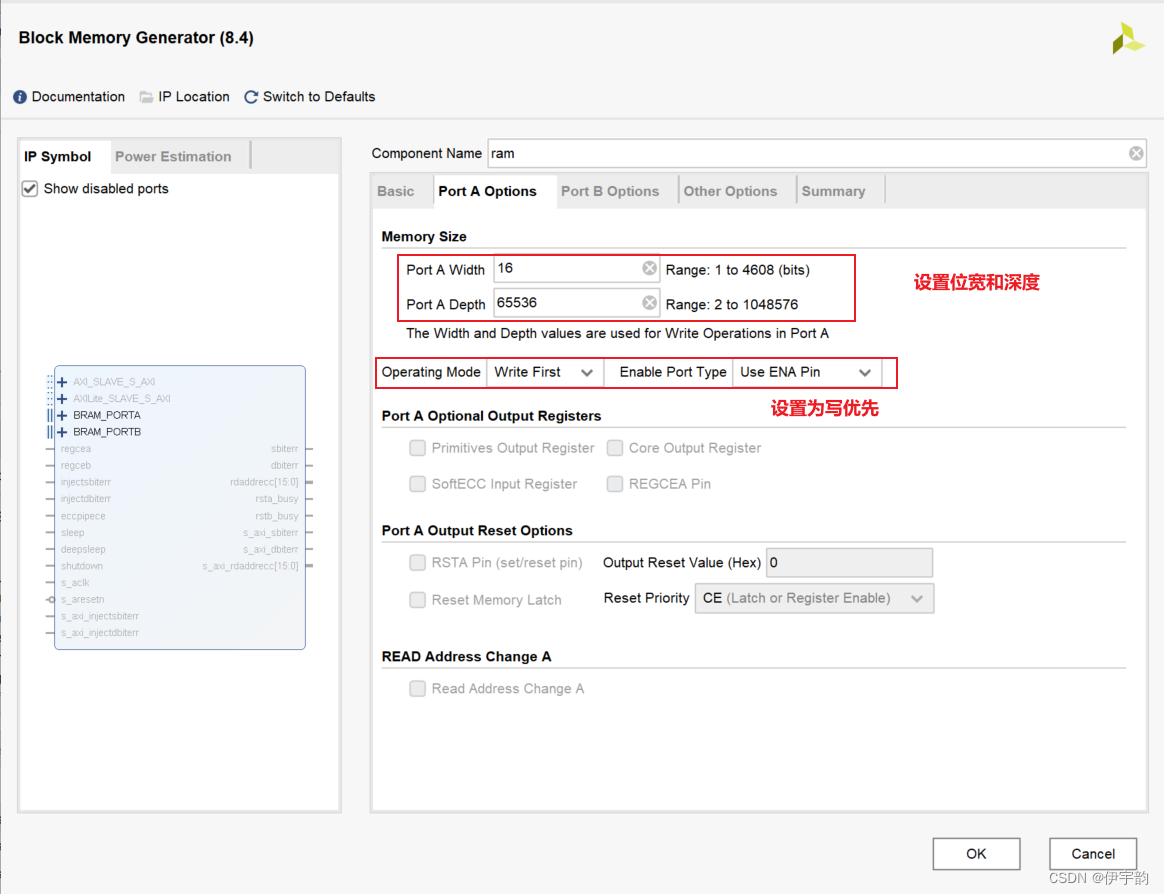

设置端口A(port A)

设置端口B(port B)

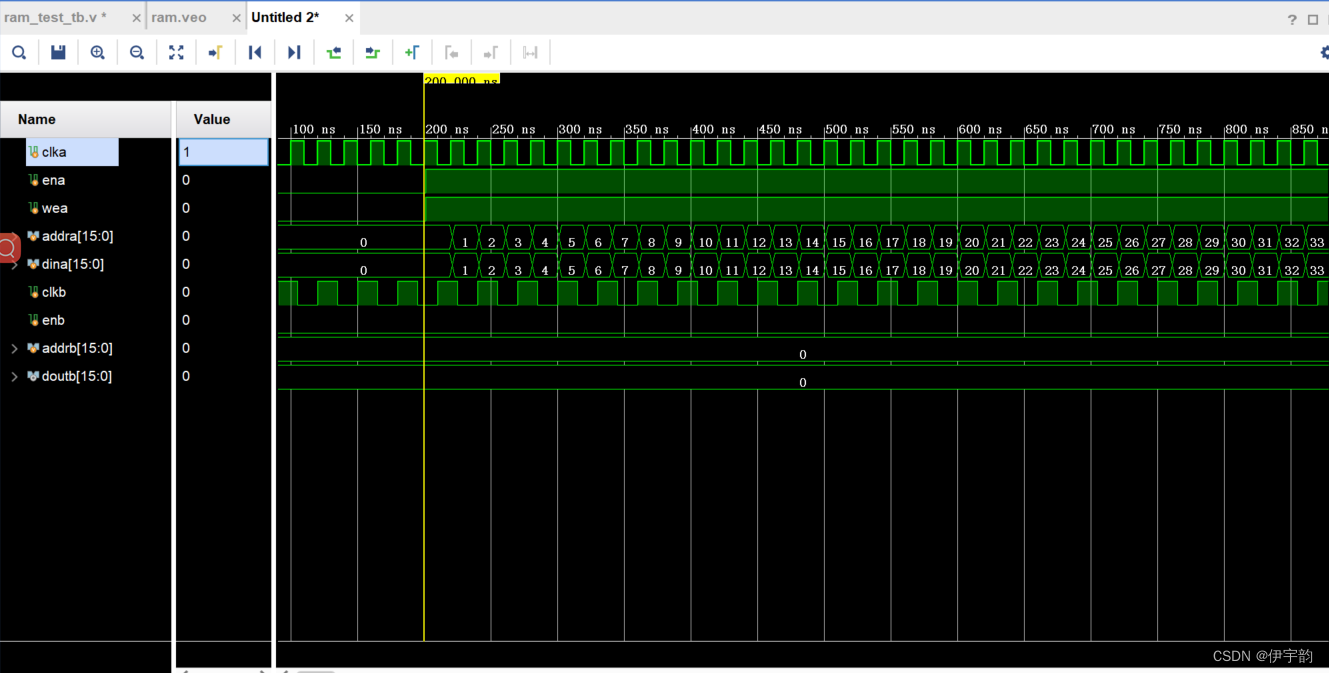

然后编写RAM测试文件 代码如下 `timescale 1ns / 1ps module ram_test_tb; reg clka; reg ena; reg wea; reg [15:0]addra; reg [15:0]dina; reg clkb; reg enb; reg [15:0]addrb; wire [15:0]doutb; ram ram ( .clka(clka), // input wire clka .ena(ena), // input wire ena .wea(wea), // input wire [0 : 0] wea .addra(addra), // input wire [15 : 0] addra .dina(dina), // input wire [15 : 0] dina .clkb(clkb), // input wire clkb .enb(enb), // input wire enb .addrb(addrb), // input wire [15 : 0] addrb .doutb(doutb) // output wire [15 : 0] doutb ); initial clka = 1; always #10 clka = ~clka; initial clkb = 1; always #15 clkb = ~clkb; initial begin ena = 0; wea = 0; addra = 0; dina = 0; addrb = 0; enb = 0; //写入写满 #201; repeat(65536) begin ena = 1; wea = 1; #20; addra = addra + 1; dina = dina + 1; end ena = 0; wea = 0; #20000; //读出; addrb = 65535; #300; repeat(65536)begin enb = 1; #30; addrb = addrb - 1; end #2000; $stop; end endmodule仿真波形 写入数据时波形

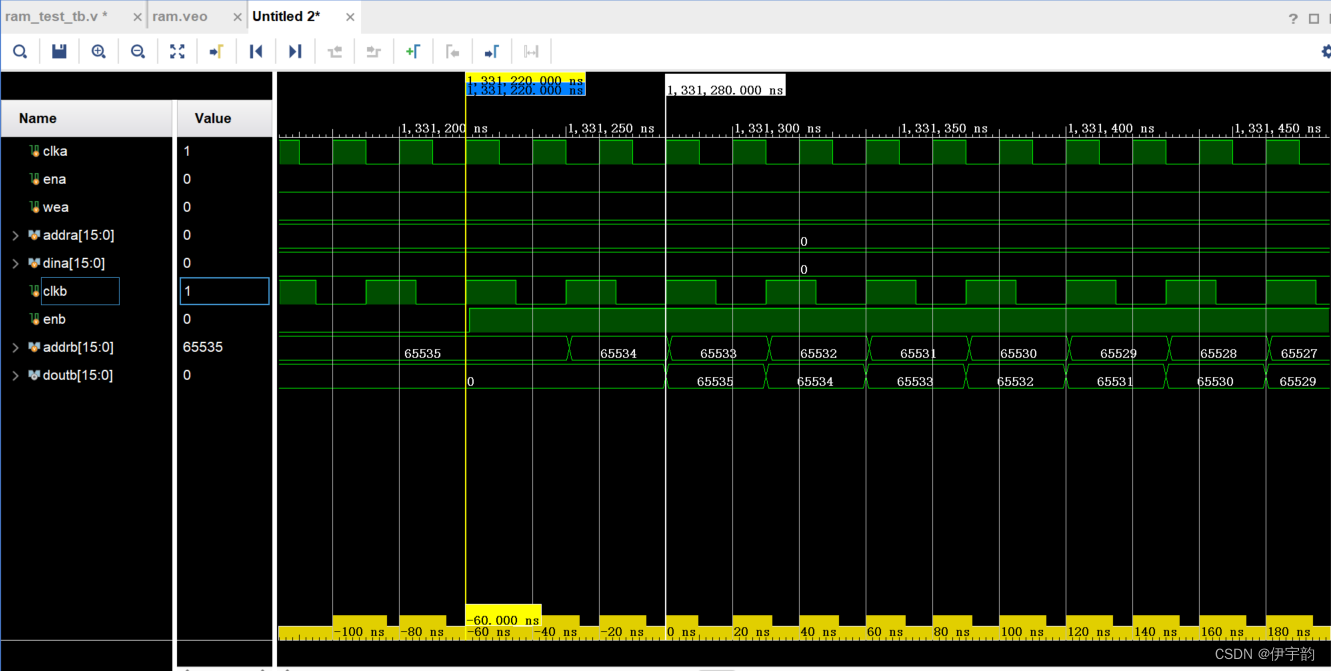

读出数据时波形(读使能到数据输出2个时钟周期)

|

【本文地址】

公司简介

联系我们