| Linux on PowerPC 学习笔记(1) | 您所在的位置:网站首页 › pmm寄存器 › Linux on PowerPC 学习笔记(1) |

Linux on PowerPC 学习笔记(1)

|

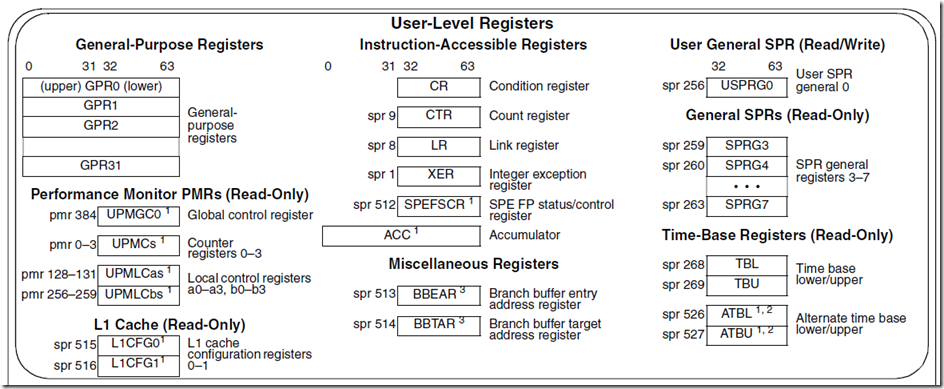

1. 准备: 1.1. 资料收集 去freescale的网站上下载下面的几个pdf文件: 名称 内容 EREFRM.pdf A Programmer's Reference Manual for Freescale Embedded Processors E500CORERM.pdf PowerPC™ e500 Core Family Reference Manual E500ABIUG.pdf PowerPC™ e500 Application Binary Interface User's Guide MPC5554.pdf MPC5554 Microcontroller Data Sheet MPC5553_MPC5554_RM.pdf MPC5553/5554 Microcontroller Reference Manual 1.2. Linux源代码下载: http://www.kernel.org/ 2. CPU学习 2.1. 寄存器 E500内核寄存器分为用户模式(ULR)和特权模式(SLR):

它们的访问受MSR(Machine State Register)的PR位的控制,PR=0时可以访问SLR。而MSR只有处于特权模式下才能访问,因此只有通过中断、系统调用和异常才能实现用户态到特权态的切换。 MSR寄存器如下所示:

在linux-2.6.33\arch\powerpc\include\asm\reg_booke.h中可以看到,Linux如下定义MSR的各个位: /* Machine State Register (MSR) Fields */ #define MSR_SF_LG 63 /* Enable 64 bit mode */ #define MSR_ISF_LG 61 /* Interrupt 64b mode valid on 630 */ #define MSR_HV_LG 60 /* Hypervisor state */ #define MSR_VEC_LG 25 /* Enable AltiVec */ #define MSR_VSX_LG 23 /* Enable VSX */ #define MSR_POW_LG 18 /* Enable Power Management */ #define MSR_WE_LG 18 /* Wait State Enable */ #define MSR_TGPR_LG 17 /* TLB Update registers in use */ #define MSR_CE_LG 17 /* Critical Interrupt Enable */ #define MSR_ILE_LG 16 /* Interrupt Little Endian */ #define MSR_EE_LG 15 /* External Interrupt Enable */ #define MSR_PR_LG 14 /* Problem State / Privilege Level */ #define MSR_FP_LG 13 /* Floating Point enable */ #define MSR_ME_LG 12 /* Machine Check Enable */ #define MSR_FE0_LG 11 /* Floating Exception mode 0 */ #define MSR_SE_LG 10 /* Single Step */ #define MSR_BE_LG 9 /* Branch Trace */ #define MSR_DE_LG 9 /* Debug Exception Enable */ #define MSR_FE1_LG 8 /* Floating Exception mode 1 */ #define MSR_IP_LG 6 /* Exception prefix 0x000/0xFFF */ #define MSR_IR_LG 5 /* Instruction Relocate */ #define MSR_DR_LG 4 /* Data Relocate */ #define MSR_PE_LG 3 /* Protection Enable */ #define MSR_PX_LG 2 /* Protection Exclusive Mode */ #define MSR_PMM_LG 2 /* Performance monitor */ #define MSR_RI_LG 1 /* Recoverable Exception */ #define MSR_LE_LG 0 /* Little Endian */ #define MSR_GS (1thread.used_vsr = 0; #endif memset(current->thread.fpr, 0, sizeof(current->thread.fpr)); current->thread.fpscr.val = 0; #ifdef CONFIG_ALTIVEC memset(current->thread.vr, 0, sizeof(current->thread.vr)); memset(¤t->thread.vscr, 0, sizeof(current->thread.vscr)); current->thread.vscr.u[3] = 0x00010000; /* Java mode disabled */ current->thread.vrsave = 0; current->thread.used_vr = 0; #endif /* CONFIG_ALTIVEC */ #ifdef CONFIG_SPE memset(current->thread.evr, 0, sizeof(current->thread.evr)); current->thread.acc = 0; current->thread.spefscr = 0; current->thread.used_spe = 0; #endif /* CONFIG_SPE */ } |

【本文地址】

公司简介

联系我们