| PCIe(三):PCIe分层结构 | 您所在的位置:网站首页 › pcie协议简介 › PCIe(三):PCIe分层结构 |

PCIe(三):PCIe分层结构

|

PCIe分层结构

绝大多数的总线或者接口,都是采用分层实现的。PCIe也不例外,它的层次结构如下:

PCIe传输的数据从上到下,都是以packet的形式传输的,每个packet都是有其固定的格式的。 事务层的主要职责是创建(发送)或者解析(接收)TLP (Transaction Layer packet),流量控制,QoS,事务排序等。 数据链路层的主要职责是创建(发送)或者解析(接收)DLLP(Data Link Layer packet),Ack/Nak协议(链路层检错和纠错),流控,电源管理等。 物理层的主要职责是处理所有的Packet数据物理传输,发送端数据分发到各个Lane传输(stripe),接收端把各个Lane上的数据汇总起来(De-stripe),每个Lane上加扰(Scramble,目的是让0和1分布均匀,去除信道的电磁干扰EMI)去扰(De-scramble),以及8/10或者128/130编码解码,等等。 今天只讲个大概,这三层以后还会专门细讲。这里先贴个这三层的细节图,自己看:

接收方物理层是最先接收到这些数据的,然后执行逆操作;在数据链路层,校验序列号和LCRC,如果没错,剥掉序列号和LCRC,往事务层走;如果校验出差,通知对方重传;在事务层,校验ECRC,有错,数据抛弃,没错,去掉ECRC,获得数据。整个过程犹如脱衣睡觉,外套脱了,衬衫脱了,内衣也脱了,光溜溜钻进被窝。

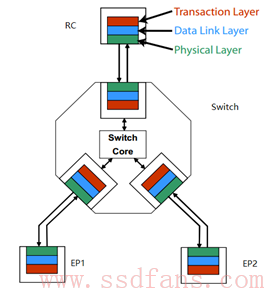

每个Endpoint都需要实现这三层,每个Switch的每个Port也是需要实现这三层的:

|

【本文地址】

PCIe定义了下三层(彩色部分):事务层(Transaction Layer),数据链路层(Data Link Layer)和物理层(Physical Layer),每层职能是不同的,且下层是为上层服务的。分层设计的一个好处:如果层次分得够好,接口版本升级时,硬件设计可能只需要改动某一层,其它层次可以保持不动。

PCIe定义了下三层(彩色部分):事务层(Transaction Layer),数据链路层(Data Link Layer)和物理层(Physical Layer),每层职能是不同的,且下层是为上层服务的。分层设计的一个好处:如果层次分得够好,接口版本升级时,硬件设计可能只需要改动某一层,其它层次可以保持不动。 数据从上到下,一层一层打包,上层打包完的数据,作为下层的原始数据,再打包。就像人穿衣服一样,穿了内衣穿衬衫,穿了衬衫穿外套。

数据从上到下,一层一层打包,上层打包完的数据,作为下层的原始数据,再打包。就像人穿衣服一样,穿了内衣穿衬衫,穿了衬衫穿外套。 红色的是TLP的格式,Data是事务层上层给的数据,事务层给它头上加个Header,然后尾巴上再加个CRC校验,就构成了一个TLP;这个TLP下传到数据链路层,又被数据链路层头上加了个包序列号,尾巴再加个CRC校验,构成一个DLLP;然后DLLP下传到物理层,头上加个Start,尾巴加个End符号,把这些数据分派到各个Lane上,然后每个Lane上加扰码,经8/10或128/130编码,最后通过物理传输介质传输给接收方。

红色的是TLP的格式,Data是事务层上层给的数据,事务层给它头上加个Header,然后尾巴上再加个CRC校验,就构成了一个TLP;这个TLP下传到数据链路层,又被数据链路层头上加了个包序列号,尾巴再加个CRC校验,构成一个DLLP;然后DLLP下传到物理层,头上加个Start,尾巴加个End符号,把这些数据分派到各个Lane上,然后每个Lane上加扰码,经8/10或128/130编码,最后通过物理传输介质传输给接收方。 和PCI数据裸奔不同,PCIe的数据是穿有衣服的。PCIe数据以packet的形式传输,比起PCI冷冰冰的数据,PCIe的数据是鲜活有生命的。

和PCI数据裸奔不同,PCIe的数据是穿有衣服的。PCIe数据以packet的形式传输,比起PCI冷冰冰的数据,PCIe的数据是鲜活有生命的。 上图中,如果RC要与EP1通信,中间要经历怎样的一个过程?

上图中,如果RC要与EP1通信,中间要经历怎样的一个过程? 如果把前述的数据发送和接收过程,我们通俗的叫做穿衣脱衣,那么,RC与EP1数据传输过程中,则存在好几次这样穿衣脱衣过程:RC跟数据穿好衣服,发送给Switch的上游端口,A为了知道该笔数据发送给谁,就需要脱掉该数据的衣服,找到里面的地址信息。衣服脱光后,Switch发现它是往EP1的,又帮它换了身新衣服,发送给端口B。B又不嫌麻烦的脱掉它的衣服,换上新衣服,最后发送给EP1。

如果把前述的数据发送和接收过程,我们通俗的叫做穿衣脱衣,那么,RC与EP1数据传输过程中,则存在好几次这样穿衣脱衣过程:RC跟数据穿好衣服,发送给Switch的上游端口,A为了知道该笔数据发送给谁,就需要脱掉该数据的衣服,找到里面的地址信息。衣服脱光后,Switch发现它是往EP1的,又帮它换了身新衣服,发送给端口B。B又不嫌麻烦的脱掉它的衣服,换上新衣服,最后发送给EP1。