| Multisim实现D触发器时钟信号分频 | 您所在的位置:网站首页 › jk触发器怎么算 › Multisim实现D触发器时钟信号分频 |

Multisim实现D触发器时钟信号分频

|

D触发器实现时钟信号分频

一. 元器件介绍二. 原理分析三. 仿真实验

一. 元器件介绍

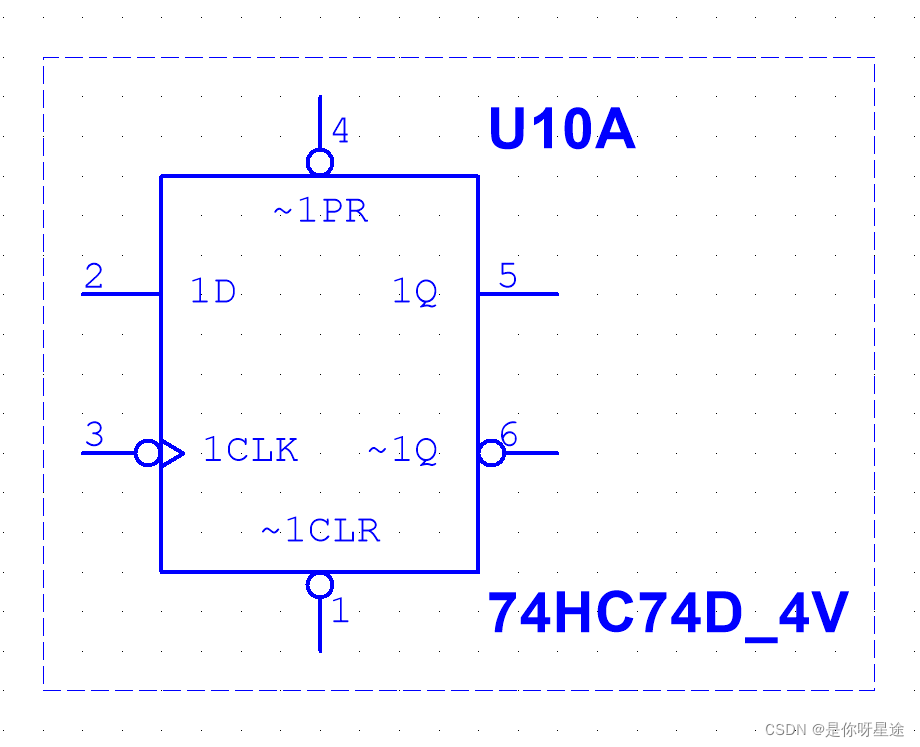

这里用到的元器件有: DIgital power(VCC)数字电源DIGITAL-CLOCK 数字时钟逻辑分析仪(XLA)ground 数字地SPDT 单刀双掷开关74HC74D_4V D触发器芯片 二. 原理分析先来说说D触发器的原理: 74HC74D_4V D触发器芯片有六个:D输入、Preset输入、Clear输入、 Q \mathsf{Q} Q输出、 Q ‾ \overline{\mathsf{Q}} Q输出、Clock时钟输入  对应输入输出电平值:

D

C

L

K

‾

\overline{\mathsf{CLK}}

CLK

Q

\mathsf{Q}

Q

Q

‾

\overline{\mathsf{Q}}

Q0↓011↓10

对应输入输出电平值:

D

C

L

K

‾

\overline{\mathsf{CLK}}

CLK

Q

\mathsf{Q}

Q

Q

‾

\overline{\mathsf{Q}}

Q0↓011↓10

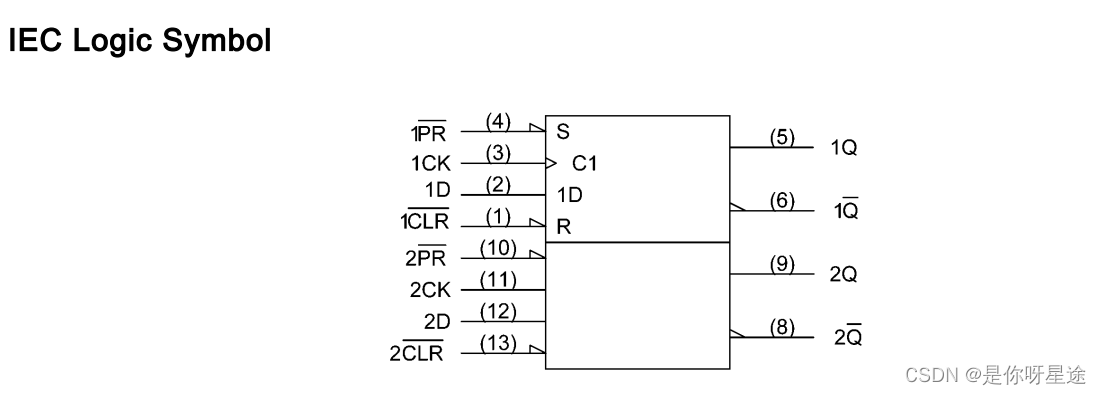

↓ = clock transition HIGH to LOW 依据表格中D输入输出值 分频器的原理: 根据时钟输入信号的上升沿(或下降沿)触发一次的时间为一周期(此处一周期为输入时钟脉冲的一周期),每变化一周期实现一次信号翻转(Toggle)。D触发器不同于JK触发器可以实现芯片内信号翻转,则信号翻转需要通过 Q ‾ \overline{\mathsf{Q}} Q输出来实现, Q ‾ \overline{\mathsf{Q}} Q输出信号为D输入信号的非信号(相反信号),则将 Q ‾ \overline{\mathsf{Q}} Q输出信号作为下一时刻的D输入信号实现翻转信号要想实现实时翻转,对D输入端初始信号没有要求 且要求不会受到Preset和Clear的影响,需要将Preset和Clear同时接高电平(实验中Preset和Clear为低电平有效)实际上完整的运行过程为D初始无信号输入,时钟下降沿触发使 Q ‾ \overline{\mathsf{Q}} Q输出到D输入上使 Q \mathsf{Q} Q输出信号变为初始信号的相反值 Q ‾ \overline{\mathsf{Q}} Q,实现一次翻转,每经过时钟一周期翻转一次,翻转两次形成输出信号的一个周期,则输出信号的一周期在时间上等价于输入时钟信号的两周期从而实现D触发器分频

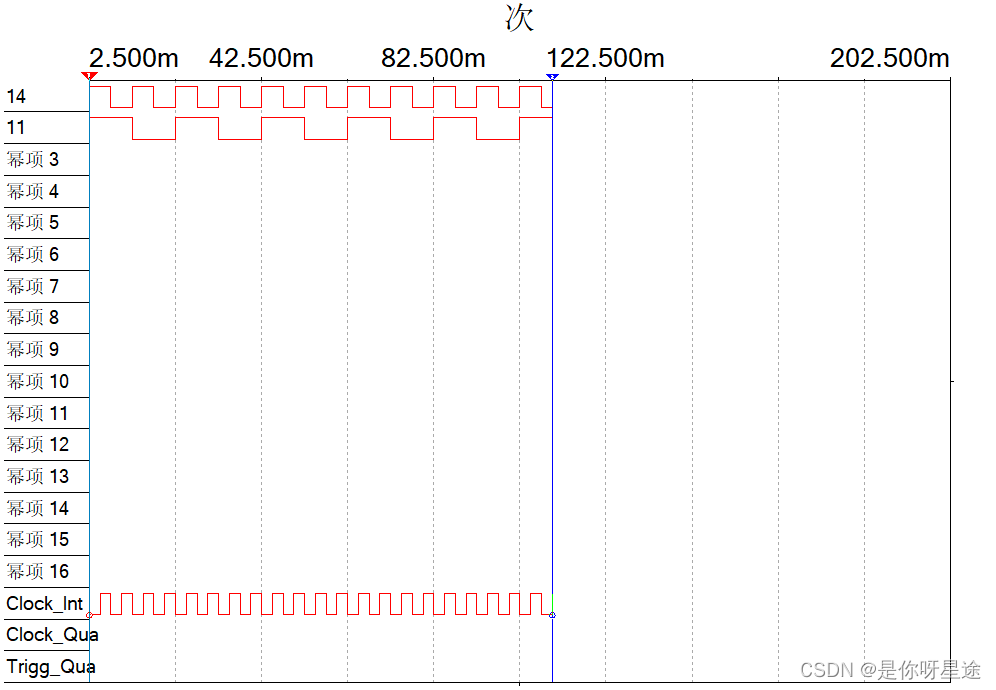

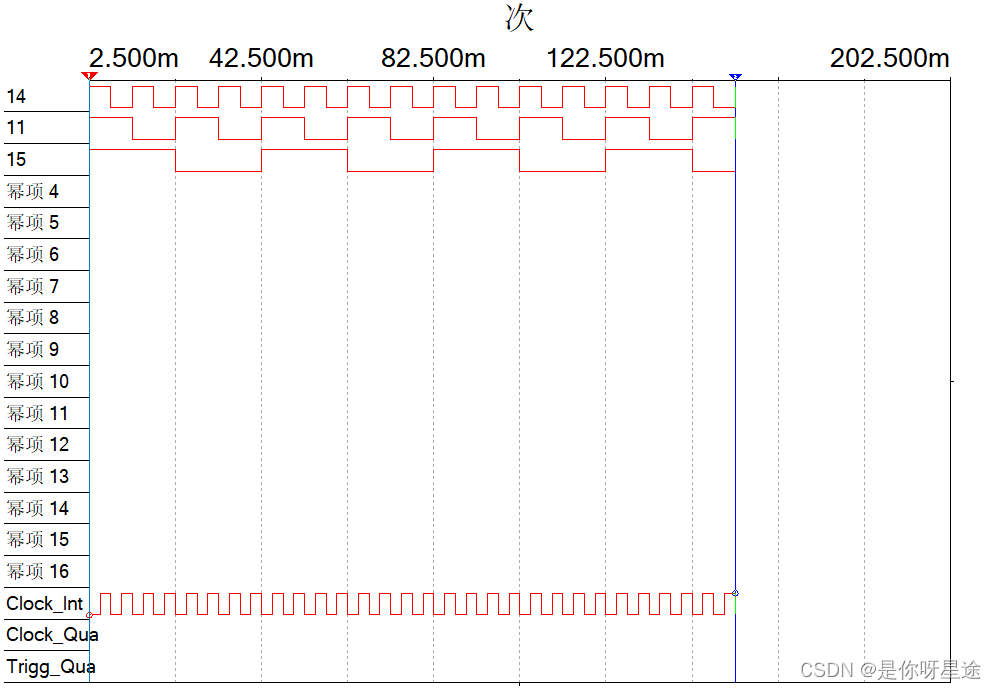

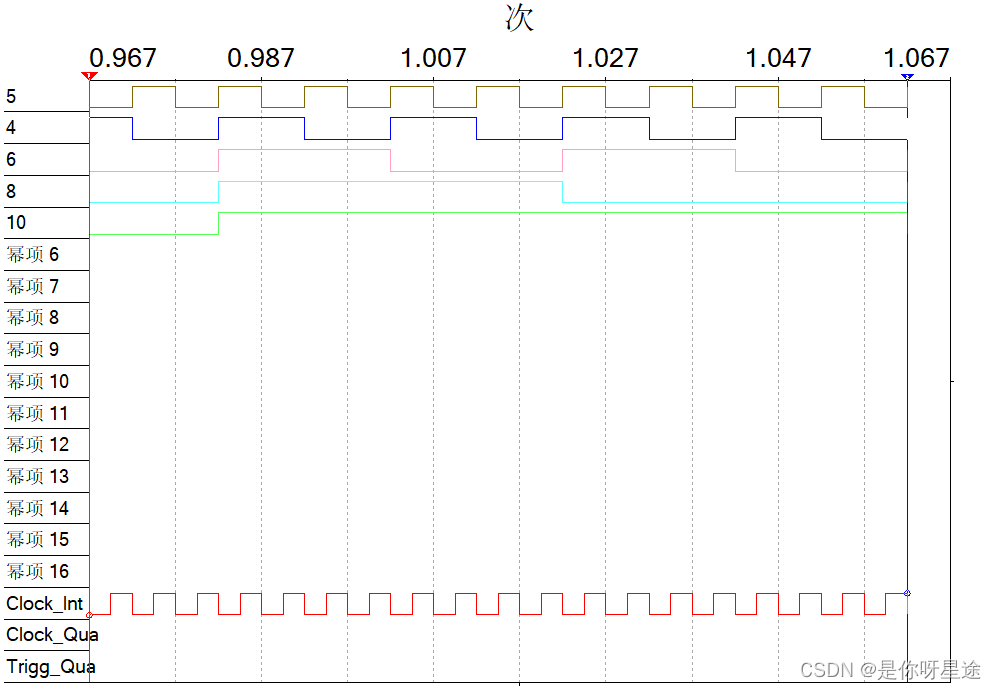

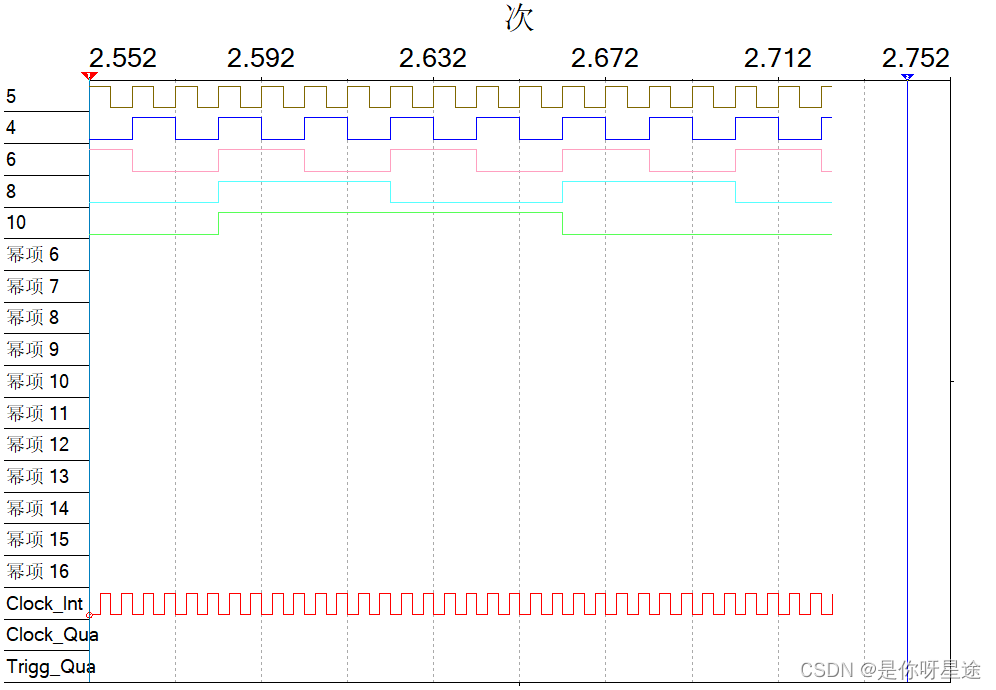

调整到可以全局概览(时钟数调整为4)

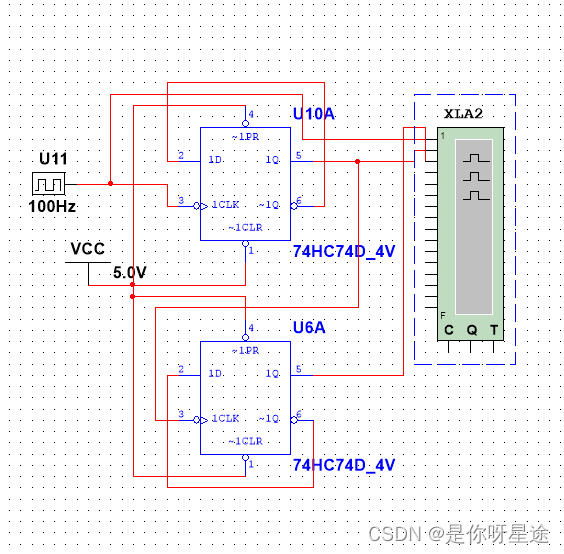

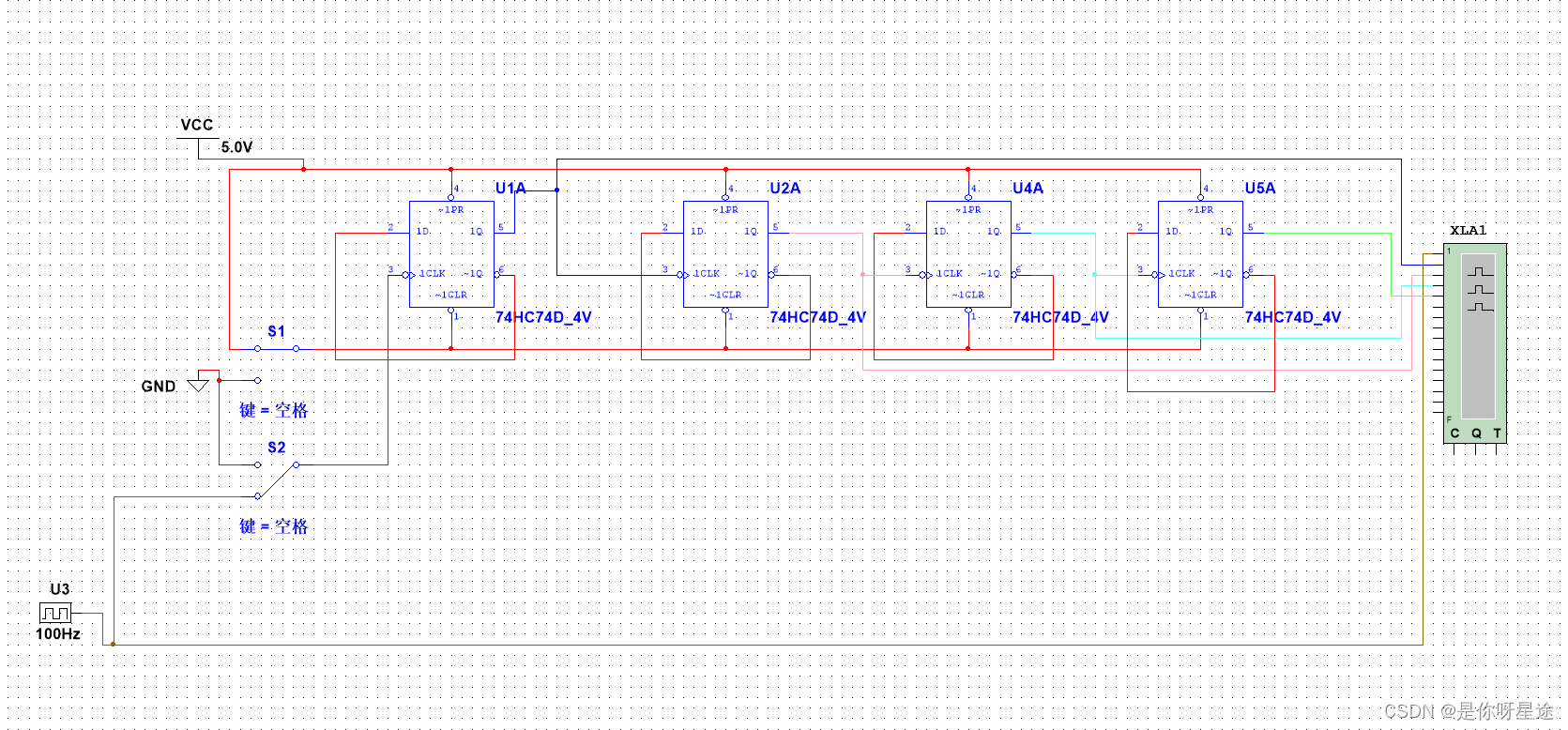

5棕线为输入100HZ,占空比为50%的时钟脉冲 4蓝线为二分频 6浅红线为四分频 8浅蓝线为八分频 10浅绿线为十六分频 图中74HC74D_4V D触发器芯片为下降沿触发 可实际上查阅相关芯片信息,描述为 the 74hc74 are dual posiN/Ave edge triggered d-type flip-flop. 表示该芯片实际上为上升沿触发,这就是为什么看到逻辑分析仪上的信号跳变为上升沿跳变 查阅相关芯片信息源 74HC74D源文档下载 实际74HC74D逻辑符号为: 据此 此芯片的实际真值表: DCLK Q \mathsf{Q} Q Q ‾ \overline{\mathsf{Q}} Q0↑011↑10↑ = clock transition LOW to HIGH 将二分频输出信号作为下一个JK触发器时钟输入信号实现对二分频的分频即四分频以此类推… 三. 仿真实验需要快速作图的小伙伴直接copy下方图片中的接线即可 以下图实现十六分频为例

逻辑分析仪显示如下图

注意设置合适的数字时钟频率以及逻辑分析仪接受频率以显示合适的图像 (该仿真实验中选择数字时钟频率为100HZ,接受时钟频率为200HZ,显示时钟格数为2-4最适) 将 Q \mathsf{Q} Q输出接入下一个D触发器时钟端,其他引脚接线方式与第一个相同 实现如下图四分频

逻辑分析仪显示如下图

以此类推实现多分频 希望能够帮到迷途之中的你,知识有限,如有学术错误请及时指正,感谢大家的阅读 (^^)/▽ ▽\(^^) |

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |

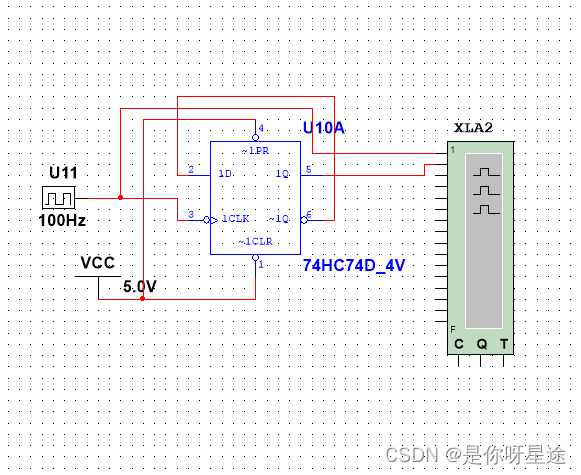

可以看到时钟输入为上升沿触发

可以看到时钟输入为上升沿触发 将Preset输入、Clear输入同时接入高电平 D输入接

Q

‾

\overline{\mathsf{Q}}

Q输出实现沿时钟上升沿翻转 如下图实现二分频

将Preset输入、Clear输入同时接入高电平 D输入接

Q

‾

\overline{\mathsf{Q}}

Q输出实现沿时钟上升沿翻转 如下图实现二分频