| 基于FPGA的数据采集系统(一) | 您所在的位置:网站首页 › fpga按键按下是0还是1 › 基于FPGA的数据采集系统(一) |

基于FPGA的数据采集系统(一)

|

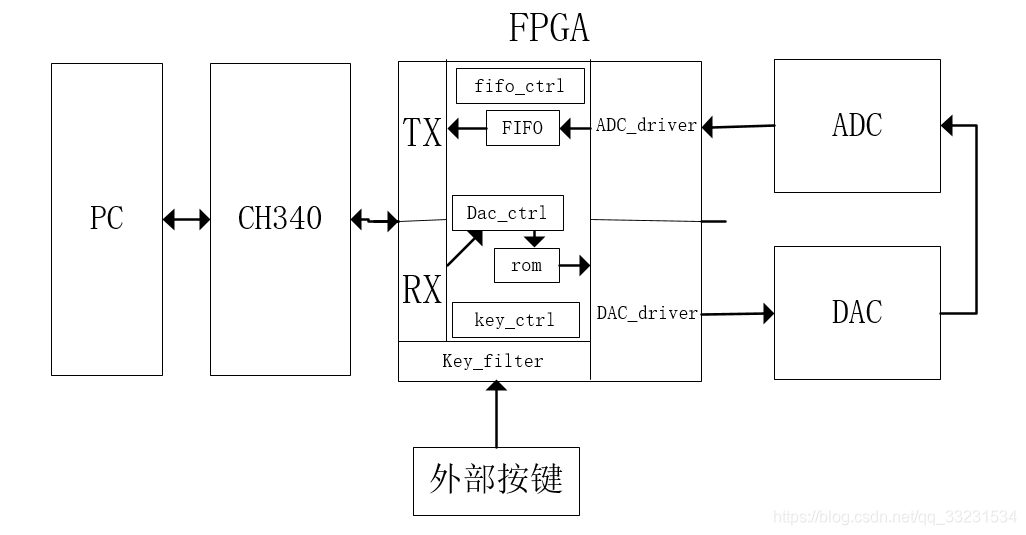

目录 整体系统设计 一、串口接收模块 二、串口发送模块 三、按键消抖模块 四、ROM模块 本设计工程文件下载链接(包含注释):https://download.csdn.net/download/qq_33231534/12450178 整体系统设计本设计主要是对ADC和DAC的使用,主要实现功能流程为:首先通过串口向FPGA发送控制信号,控制DAC芯片tlv5618进行DA装换,转换的数据存在ROM中,转换开始时读取ROM中数据进行读取转换。其次用按键控制adc128s052进行模数转换100次,模数转换数据存储到FIFO中,再从FIFO中读取数据通过串口输出显示在pc上。其整体系统框图如下:  图1:FPGA数据采集系统整体框图

图1:FPGA数据采集系统整体框图

从图中可以看出,该系统主要包括9个模块:串口接收模块、按键消抖模块、按键控制模块、ROM模块、DAC驱动模块、ADC驱动模块、同步FIFO模块、FIFO控制模块、串口发送模块。各个模块的作用如下: (1)串口接收模块(UART_Byte_Rx.v):完成串口数据接收,将串行数据转换成并行数据输出。 (2)按键消抖模块(key_filter.v):进行按键消抖,可输出一个脉冲按键按下标志和按键按下时间标志。 (3)按键控制模块(key_ctrl.v):当在DA一直输出模拟信号时,按下按键控制ADC转换100次。 (4)ROM模块(single_port_rom.v):存储DA转换的数据,可存放正弦波形数据。 (5)DAC驱动模块(dac_driver.v):数模转换驱动模块,与外部DAC芯片相连,提供DAC芯片时钟和数据信号等。 (6)ADC驱动模块(adc_driver.v):模数转换驱动模块,与外部ADC芯片相连,提供ADC芯片时钟和控制信号等。 (7)同步FIFO模块(sync_fifo.v):存放ADC转换后的数据。 (8)FIFO控制模块(fifo_ctrl.v):当FIFO中有数据时,将FIFO中的数据转换成可以UART串口发送的数据。 (9)串口发送模块(Uart_Byte_Tx.v):经过FIFO控制模块转换的数据通过串口发送模块发送到串口,显示在pc端。 (10)DAC控制模块(dac_ctrl.v):当接收串口指定的指令时,开始将ROM的正弦数据进行DAC转换。 一、串口接收模块前面已经写过串口接收模块,这里可以直接拿来用。这里串口发送数据格式包含:1位起始位、8位数据位、1位停止位,无校验位。该模块接口列表入下: 表1.1:串口接收模块接口列表 信号名称I/O位数功能描述clkI1系统时钟50MHzrst_nI1系统复位rs232_txI1串口串行数据发送数据口baud_setI3波特率选择信号data_byteO8并行数据输出rx_doneO1接收1字节数据完成标志代码如下:UART_Byte_Rx.v //------------------------------------------------------------------- //https://blog.csdn.net/qq_33231534 PHF的CSDN //File name: UART_Byte_Rx.v //Last modified Date: 2020/5/22 //Last Version: //Descriptions: 工业级别串口数据接收模块,防干扰。对每位数据内部采样16个点, // 对中间6位数据进行判定数据是1还是0 //------------------------------------------------------------------- module UART_Byte_Rx( input clk ,//系统时钟50MHz input rst_n ,//系统复位 input rs232_tx ,//串口串行数据发送数据口 input [ 2: 0] baud_set ,//波特率选择信号 output reg [ 7: 0] data_byte ,//并行数据输出 output reg rx_done //接收1字节数据完成标志,rx_done可以作为输出有效信号使用 ); reg [ 13: 0] baud_c ;//波特率对应计数次数(4800bps-10416),(9600bps-5208),(19200bps-2604), //(38400bps-1302),(57600bps-868),(115200bps-434) reg rs232_tx_ff0 ; reg rs232_tx_ff1 ; reg rs232_tx_ff2 ; wire tx_neg_flag ; reg add_flag ; reg [ 13: 0] cnt0 ; reg [ 3: 0] cnt1 ; reg [ 9: 0] cnt2 ; reg [ 3: 0] cnt3 ; reg [ 2: 0] cnt_0 ; reg [ 2: 0] cnt_1 ; wire add_cnt0 ; wire end_cnt0 ; wire add_cnt1 ; wire end_cnt1 ; wire add_cnt2 ; wire end_cnt2 ; wire add_cnt3 ; wire end_cnt3 ; //查找表 always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin baud_c |

【本文地址】