| Vitis指南 | 您所在的位置:网站首页 › fpga加速卡干嘛用的 › Vitis指南 |

Vitis指南

|

大侠好,欢迎来到“艮林子”专栏,本次为艮林子首次和大侠见面,新春佳节之际,略备薄礼,不成敬意,给大侠带来“Xilinx Vitis 系列连载”,给大侠提供参考学习的资料,如有不足之处,还请多多指教。 由于内容过多,首篇给大侠列出目录,后续有时间分篇连载发出,欢迎各位大侠关注“FPGA技术江湖”,我们是真正做事的团队,希望大家多多支持,如果想获取更多资源,可以加大辉哥微信,进交流群,可以永久性交流学习,共同进步。 今天带来第一篇,介绍Vitis 2019.2软件平台发行说明、安装以及Vitis加速环境简介。后续还会带来详细的开发教程,敬请关注。话不多说,咱们就进入正题。 VITIS简介 作者:艮林子 校对:陆辉 连载目录 一、Vitis 2019.2软件平台发行说明 1.1 Vitis软件平台中的内容 1.1.1 硬件加速的应用程序开发流程 1.2 改变行为 1.2.1 从SDAccel迁移 1.2.2 从SDSoC迁移 1.3 支持平台 1.3.1 数据中心加速卡 1.3.2 嵌入式平台 二、安装 三、Vitis加速环境简介 3.1 简介与概述 3.2 FPGA加速 3.3 执行模型 3.4 建立过程 3.4.1 主机程序构建过程 3.4.2 FPGA二进制构建过程 3.5 建立目标 3.5.1 软件仿真 3.5.2 硬件仿真 3.5.3 系统 3.6 使用Vitis软件平台加速应用程序的方法论 3.6.1 文件受众和范围 3.6.2 加速:工业类比 3.6.3 设计设备加速应用程序的方法 3.6.4 开发C / C ++内核的方法论 四、开发应用程序 4.1 程序设计模型 4.2 主机申请 4.2.1 设置OpenCL环境 4.2.2 在FPGA中执行命令 4.2.3 后处理和FPGA清理 4.2.4 摘要 4.3 RTL内核 4.3.1 RTL内核的要求 4.3.2 RTL内核开发流程 4.3.2.1 将RTL代码打包为Vivado IP 4.3.2.2 创建内核描述XML文件 4.3.2.3 从RTL内核创建XO文件 4.3.3 RTL内核向导 4.3.4 摘要 五、构建和运行程序 5.1 设置Vitis环境 5.2 建立目标 5.2.1 软件仿真 5.2.2 硬件仿真 5.2.3 系统硬件目标 5.3 构建主机程序 5.4 构建FPGA二进制文件 5.4.1 在Vivado HLS中创建内核 六、对应用程序进行性能分析,优化和调试 七、使用Vitis分析仪 7.1 处理报告 7.2 了解葡萄分析仪 7.3 创建运行配置 7.4 配置葡萄分析仪 八、使用Vitis IDE 8.1 Vitis命令选项 8.2 创建Vitis IDE项目 8.2.1 启动Vitis IDE工作区 8.2.2 创建一个应用程序项目 8.2.3 管理平台和存储库 8.2.4 了解Vitis IDE 8.2.5 添加源 8.2.5.1 添加源文件 8.2.5.2 创建和编辑新的源文件 8.2.5.3 在项目编辑器视图中工作 8.2.5.4 在助理视图中工作 8.3 建立系统 8.3.1 Vitis IDE指导视图 8.3.2 从Vitis IDE使用Vivado工具 8.4 建立系统 8.5 配置Vitis IDE 8.5.1 Vitis项目设置 8.5.2 Vitis Build配置设置 8.5.3 Vitis运行配置设置 8.5.4 Vitis二进制容器设置 8.5.5 Vitis硬件功能设置 8.5.6 Vitis工具链设置 4.5.6.1 Vitis内核编译器和链接器选项 4.5.6.2 emconfigutil设置 4.5.6.3 G ++主机编译器和链接器设置 8.6 项目进出口 8.6.1 导出Vitis项目 8.6.2 导入葡萄项目

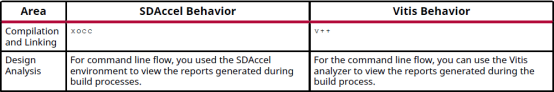

正文 一 Vitis 2019.2软件平台发行说明 1.1 Vitis软件平台中的内容 1.1.1 硬件加速的应用程序开发流程对于基于FPGA的加速,Vitis核心开发工具包允许使用API构建软件应用程序,比如建立一个软件应用程序的OpenCL™ API,运行硬件(HW)内核上加速卡,如赛灵思 Alveo数据中心加速卡。所述葡萄核心开发套件还支持运行运行Linux,如嵌入式处理器平台上的软件应用ZYNQ的UltraScale +片上多核设备。对于嵌入式处理器平台,Vitis核心开发套件执行模型还使用OpenCL API和基于Linux的Xilinx 运行时(XRT),用于调度硬件内核并控制数据移动。 VItis具包可支持Alove 200,U250,U280和数据中心加速卡,还有zcu102_base,zcu104_base,zc702_base和zc706_base嵌入式处理器平台。除了这些现成的平台以外,还支持自定义平台。 通过Vitis软件平台,您可以将数据中心应用程序迁移到嵌入式平台。所述Vitis核心开发工具包括在V++台上的硬件内核编译器,g++编译器用于编译在x86主机上运行的应用,以及ARM®用于交叉编译应用程序到的嵌入式处理器上运行的编译器的Xilinx设备。 1.2 改变行为 1.2.1 从SDAccel迁移下表列出了SDAccel开发环境和Vitis软件平台之间的差异。

总览 该葡萄的核心开发工具包是仿照SDAccel™编程和执行模型。Vitis环境的一项优势是它对数据中心和边缘应用程序的支持。这意味着您可以在标准数据中心平台(例如Alveo™数据中心U200加速卡)上对应用程序进行原型设计,然后在可用时将应用程序重定向到边缘平台。有关更多信息,请参阅构建主机程序。 在Vitis环境中,您需要调用Arm交叉编译器以构建主应用程序代码,并调用Vitis编译器以构建硬件内核。您为主机(.elf)创建一个可执行文件,为硬件内核(.xclbin)创建一个映像。您将使用OpenCL API和基于Linux的Xilinx运行时(XRT)来控制主应用程序和内核之间的数据移动,并计划任务的执行。 对于嵌入式处理器平台(或项目),Vitis环境仅支持运行Linux主机操作系统且平台已将XRT和ZOCL驱动程序添加到根文件系统的平台。平台创建者需要提供一个sysroot,以便通过OpenCL包含文件和库交叉编译到Arm 核心。在主机编译期间,您将需要使用适当的标头。 要从SDSoC环境迁移到Vitis环境,您将必须修改构建脚本和源代码。本节讨论迁移步骤,包括命令行示例,这些示例使用sysroot中的文件,使用Vitis编译器编译硬件内核,并使用Arm cross编译器编译主机应用程序。提供的代码示例仅用于教育目的,不应用于您的设计。 基本迁移步骤如下: 迁移主机应用程序 更新所需的#include文件 根据需要编辑主要功能以及任何其他软件的仅特定功能 迁移硬件功能 使用编译指示定义内核接口 建立系统 构建和链接内核 编译和链接应用程序 迁移主机应用程序 在本节中,您将回顾具有和加速功能的简单SDSoC™程序,main()以识别必须更改的元素。要开始将应用程序和硬件功能迁移到Vitis环境平台和工具的过程,请检查您的主要功能和硬件功能代码。此处提供的代码是mmult示例应用程序。 以下代码段是main()原始开发应用程序项目中的示例函数。 #include #include #include "mmult.h" #include "sds_lib.h" #define NUM_TESTS 5 void printMatrix(int *mat, int col, int row) { for (int i = 0; i |

【本文地址】