| ARM TrustZone白皮书部分阅读 | 您所在的位置:网站首页 › dsc480处理器调试 › ARM TrustZone白皮书部分阅读 |

ARM TrustZone白皮书部分阅读

|

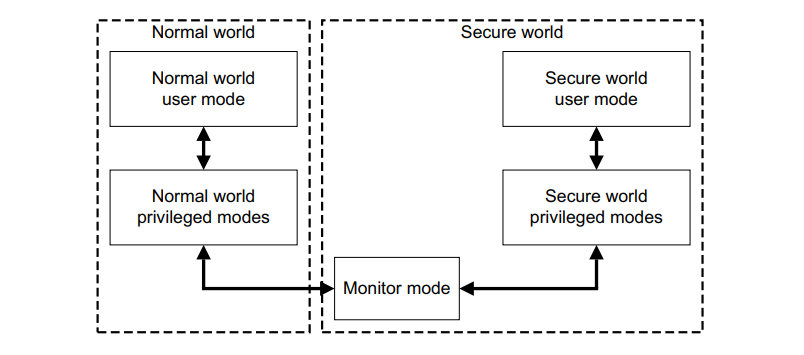

每个处理器核心都提供了两个虚拟核心,一个安全一个不安全,还有一个在他们之间进行上下文切换的 monitor mode:

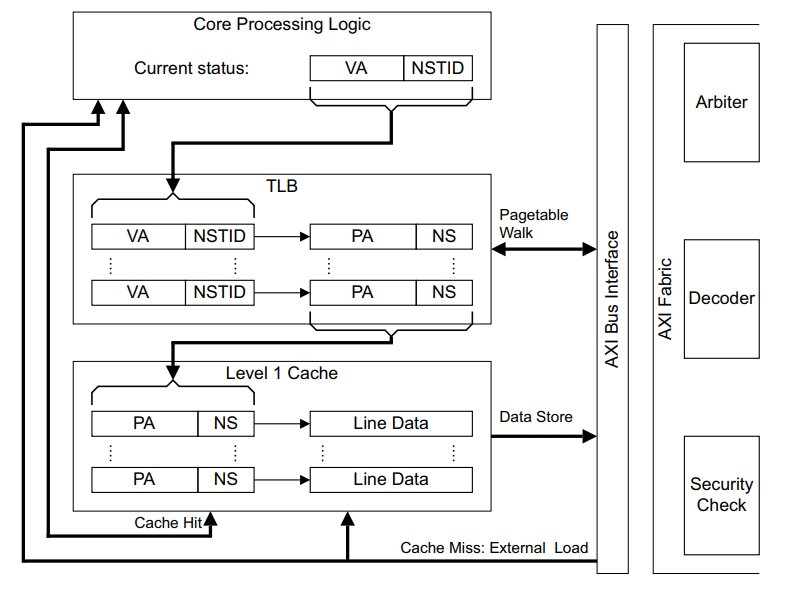

发送到主系统总线上的NS位的值是由执行指令或数据访问的虚拟内核的身份标识间接得出的。非安全的虚拟处理器只能访问非安全系统资源,但安全虚拟处理器可以看到所有资源。 world切换:这两个虚拟处理器以时间切片的方式执行,在更改当前运行的虚拟处理器时,上下文将通过名为monitor mode的新核心模式进行切换。物理处理器进入monitor mode时可以通过执行特定指令的软件、SMC指令、硬件异常机制的子集进行触发。如果处理器不在监控模式下,它正在执行的世界由系统控制协处理器CP15中安全配置寄存器(SCR)中的NS位指示;如果处于监控模式下,无论SCR NS位的值是多少,处理器总是在安全的世界中执行;但是如果SCR NS位设置为1,则对banked CP15寄存器的操作将访问正常世界的副本。 一级保护内存系统: MMU:TrsutZone中硬件提供两个虚拟MMU,每个虚拟处理器一个。每个世界都有一组本地转换表,使它们能够独立地控制虚拟地址到物理地址的映射。为在两个世界之间实现高效的上下文切换,arm处理器会标记TLB中的条目,TLB缓存了地址转换表的遍历结果,并使用执行遍历的世界的标识,这允许非安全和安全条目在TLB中共存,从而加快切换,因为无需刷新TLB条目。 cache:目标是实现支持缓存中两种安全状态的数据,这样可以消除切换世界的时候需要刷新缓存的需要。解决方法是处理器缓存扩展了一个额外的标志位,该位录访问内存的事务的安全状态。

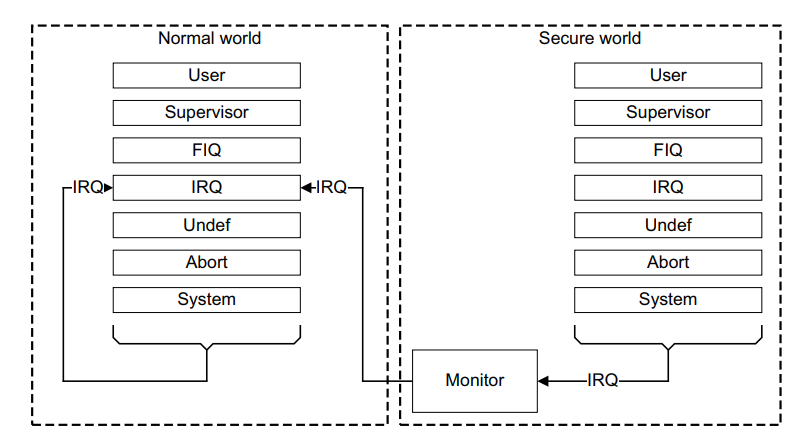

安全中断:直接向monitor捕获IRQ和FIQ的能力(不需要任何一个世界的代码干预)可以为安全中断源创建一个灵活的中断模型。ARM推荐的模型是使用IRQ作为非安全世界的中断源,FIQ作为安全世界的中断源。CPSR是存放的程序状态寄存器

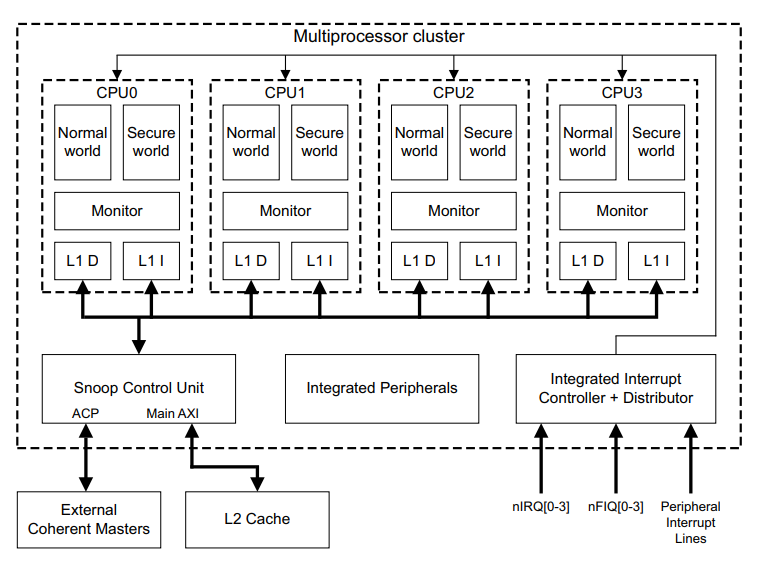

启用TrustZone的处理器实现了三组异常向量表。其中一个表用于正常世界,一个用于安全世界,另一个用于监视模式。 安全处理器:协处理器CP15中的敏感的配置选项,或全局应用于核心的配置选项,只能由安全世界软件编写,非安全世界可以读取。 多处理器系统:集群中的处理器可以配置为以对称多处理(SMP)模式或非对称多处理(AMP)模式执行。当处理器以SMP模式执行时,集群的Snoop控制单(SCU)将透明地将跨SMP处理器共享的数据保存在L1数据缓存中。当处理器以AMP模式执行时,如果需要,执行软件必须手动保持内存一致性。多处理器集群中的每个处理器都有一个正常世界和一个安全世界。每个虚拟处理器都可以独立控制它们的MMU配置。

|

【本文地址】