| DC | 您所在的位置:网站首页 › dcdc频率越高噪声越低吗 › DC |

DC

|

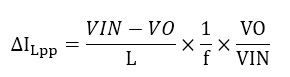

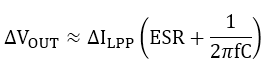

作者:AirCity 2020.2.16 [email protected] 本文所有权归作者Aircity所有 DC-DC即直流-直流转换器,输入是直流电压,输出也是直流电压。DC-DC有升压型boost,降压型buck和升降压型buck-boost。本文只讲述Buck型DC-DC,并用DC-DC简称Buck。 跟LDO相比,DC-DC的效率非常,功率大,但复杂度,成本也高一些。 1 DC-DC基本原理 1.1 输出电压如下图,一个典型的DC-DC Buck电路如左上角图示。 D表示NMOS管的占空比,DC-DC的输出电压与占空比正相关。 这个就是DCDC的基本原理。 2 DCDC的损耗DCDC损耗包括直流损耗,交流损耗。交流损耗又包括MOS管开关损耗、电感铁损、MOS管死区损耗和MOS管驱动器损耗。 直流损耗一般占5%,交流损耗一般占2%-5%。 2.1 DCDC直流损耗DCDC的损耗主要包括MOS管Q1的直流阻抗损耗,二极管D1的导通损耗,电感的直流电阻损耗,电感的交流损耗。有关电感的损耗见文章《了解电感—参数、特性、选型》。则DCDC的直流损耗可以计算如下: 假设DCDC是一个12V输入,3.3V/10A输出的降压电源; DCDC效率: 假设Q2和Q1的参数一致,则同步降压型DCDC的功率损耗为 MOS管的开关损耗是由“弥勒效应”导致的。详细自行百度。这里指说一下大概原理。 我们把管子导通的关断瞬变过程放大,如下图。IDS和VDS都是一个缓慢变化的过程,这个过程的功率损耗,在同样时间内,可比管子的直流损耗大多了!VSG电压中间的那个小平台就是米勒平台。 MOS管的打开和关闭损耗计算起来很复杂,但可以从器件规格书中找到。 2.2.2 电感的铁损铁损指交流信号在磁芯和屏蔽材料中的损耗。介绍详见文章《了解电感—参数、特性、选型》。 交流信号的频率越高,损耗越大。铁氧体磁芯是陶瓷铁磁材料,由氧化铁与氧化锰或氧化锌的混合物构成的晶体结构,这种材料虽然容易磁饱和,但磁芯损耗小。另一种磁芯是金属(铁粉),这种材料磁饱和过程比较舒缓,但是磁芯损耗很大。 2.2.3 Q1和Q2的死区损耗Q1和Q2不可能完全同步,两个管子都处于关断状态时,称为死区时间。此时两个管子的体二极管有传导损耗。这部分损耗与频率成正比,但很难计算。 2.2.4 MOS管驱动器损耗这个指驱动器驱动MOS管的G极,消耗的能量,大小与频率有关(VDRVQGf)。 3 DCDC的开关频率开关频率越高,对L和C的要求越低,可以选择较小的值,而且瞬态响应也好。但是高的开关频率会带来较大的交流损耗,发热严重。 看了ADI,MPS,TI和ON的DCDC选型表,输出电流>10A的DCDC,开关频率都只有几百KHz。输出电流<10A的DCDC,开关频率从几百KHz到几MHz不等。 开关频率每增加1倍,DCDC效率大约会降低2%。 4 PWM与PFM当DCDC负载较大时,一般是PWM模式。当DCDC负载比较轻时,一般是PFM模式。 PWM是脉冲宽度调制,功率越大,占空比越大,Q1的导通时间越长。 PFM是固定脉冲宽度的频率调制,Q1只在需要给电感充电的时候打开,打开的时间固定。 在PFM模式,MOS管导通时间短,直流损耗小,效率高。在PFM模式,如果负载电流瞬间增大,电流反馈将迅速提高PFM的频率,提高输出电流。 PWM模式下,开关频率很高,交流损耗很大,如果此时负载很轻,会导致DCDC效率很低,这个时候要切换到PFM模式,降低开关频率。 5 DCDC的纹波电流根据公式(1)和公式(3),纹波电流公式如下: 由公式可知,电感越大,纹波电流越小。频率越高,纹波电流越小。但感值越大,直流损耗和交流损耗都越大。一般来说挑选电感时,会把纹波电流控制在输出电流平均值的25%~50%。 6 DCDC的MOS管选择要选择VDS耐压大于VIN的MOS管,但不宜大出太多。 RDS(ON)越小越好,QGD(栅极电荷)越小越好,但这两个值是一对矛盾。一般而言,小硅芯片尺寸的FET具有低 QG,但导通电阻RDS(ON)很高;而採用大硅芯片的FET則具有低RDS(ON),但QG很大。在2.2节中,我们得知Q1有开关损耗,Q2没有。所以Q1的QG很重要,越小越好,特别是DCDC的输出电压低或者DCDC的占空比小(轻载)的应用场景。对Q2的QG没有严格要求,它的低RDS(ON)更重要。 DCDC转换器都是集成了Q1和Q2的,不需要自己选。DCDC控制器是需要自己选MOS管的,一般用在大功率场所。 7 DCDC的输入电容CIN和输出电容COUT电容的定电压要高于工作电压,并且要有一定比例降额。 CIN上经常有脉冲开关大电流和大的纹波,因此要选择ESR低的电容,如陶瓷电容,聚合物电容,或者用多个铝电解电容,钽电容并联使用。注意电容会有一个额定功率损耗或者RMS纹波电流指标,要注意不能超限。 COUT越大,输出电压纹波越小,DCDC的瞬态响应性能越好。输出电压纹波计算公式如下: 电压反馈模式的反馈点都在最远端,所有DCDC的外部FB管脚都是电压反馈输入,一定要从最远的负载端引线。负反馈的原理很简单,不再解释。 电流反馈模式有两个回路,一个是电压反馈,一个是电流反馈,如下图。电压反馈仍然在DCDC外部,电流反馈回路在DCDC内部。这个反馈回路实时监测DCDC的输出电流,在DCDC启动和运行时,都能更好的让系统稳定工作。电流反馈模式能提供更快的响应速度。 IQ:DCDC工作时自身消耗的电流。这个是越小,DCDC效率越高。规格书会提供PWM模式的IQ,一般是10~20mA。PFM模式一般只有几十uA。 DCLOAD:负载电流调整率。电流从0到最大电流跳变,输出电压变化率,单位是%/A; DCLINE:线性负载调整率,指额定负载下输出电压随输入电压变化而发生的变化率。 tSTART:启动时间,从EN信号有效,到VOUT达到95%输出电压值的时间。这个值一般在几百us。如果VIN和EN连接在一起,这个时间可能更长,因为VIN施加后,DCDC内部电路需要一段时间才能稳定工作。 其他参数都很简单,不解释了。 10 如何估算电感值下面是一个电感的电流理论波形,IO是输出电流均值,ΔI是纹波电流大小。

需要在靠近负载端的地方焊接一根粗导线,用电流探头测量,如下两个示意图: 如果要用串小电阻,毫欧姆级别,测电压的方式,这个电压往往很小,很容易受到DCDC电路的MOS管开关信号的影响,不推荐。 一定要测量DCDC的电流,这是观察电感选择是否合适的一个重要手段,如果电感发生了接近磁饱和现象,电流会突然增大,如下图: 如下图,红色阴影部分,是交流电流区域,噪声非常高,要注意隔离。其他小信号不得与这个区域在相邻层。 红色实线和红色虚线,有高频的大电流,需要尽量缩短寄生电感,因此走线要足够短,过孔要足够多的。 图中的SW这个点,电压一直在跳变,有很强的EMI噪声,这个点需要用地屏蔽,立体包地。 CHF一定要有,否则在VSW信号上会有很强的开关噪声。 |

【本文地址】

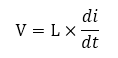

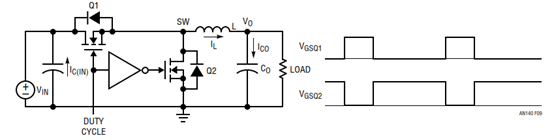

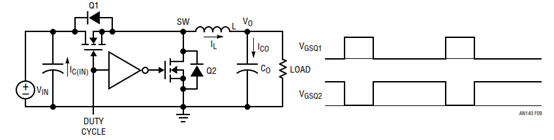

当NMOS管Q1导通时,VIN向电感充电,回路情况如图A。此时VSW=VIN,VL=VIN-VO;当NOMS管Q1关断时,回路情况如图B。此时VSW=0,VL=-VO。 电感两端的电压公式是:

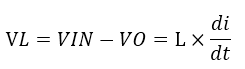

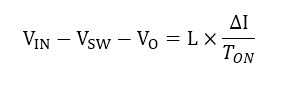

当NMOS管Q1导通时,VIN向电感充电,回路情况如图A。此时VSW=VIN,VL=VIN-VO;当NOMS管Q1关断时,回路情况如图B。此时VSW=0,VL=-VO。 电感两端的电压公式是:  当NMOS管导通时:

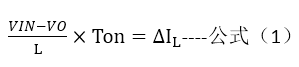

当NMOS管导通时:  假设电流是线性变化,则上式简化为:

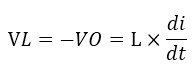

假设电流是线性变化,则上式简化为:  当NMOS管关断时:

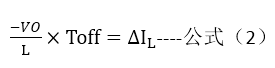

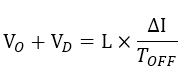

当NMOS管关断时:  假设电流是线性变化,则上式简化为:

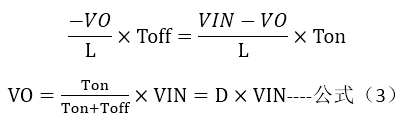

假设电流是线性变化,则上式简化为:  公式(1)和公式(2)可以推到出:

公式(1)和公式(2)可以推到出:

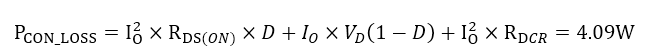

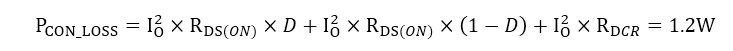

R_(DS(ON))是MOS管的导通阻抗,假设为10mΩ; V_D是二极管的正向导通电压,假设为0.5V; R_DCR是电感的直流电阻,假设为2mΩ;

R_(DS(ON))是MOS管的导通阻抗,假设为10mΩ; V_D是二极管的正向导通电压,假设为0.5V; R_DCR是电感的直流电阻,假设为2mΩ; 上述损耗中,二极管的损耗值为3.62W,非常之大,其实可以用一个NMOS来代替之。如下图:

上述损耗中,二极管的损耗值为3.62W,非常之大,其实可以用一个NMOS来代替之。如下图:  Q1和Q2是互补导通的,他们需要严格同步,所以这种结构的DCDC成为同步降压型转换器。最上面的二极管型DCDC成为非同步(或“异步”)降压转换器。

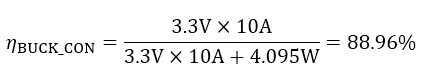

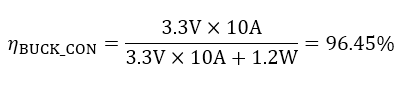

Q1和Q2是互补导通的,他们需要严格同步,所以这种结构的DCDC成为同步降压型转换器。最上面的二极管型DCDC成为非同步(或“异步”)降压转换器。 效率为:

效率为:  同步型DCDC效率更高!

同步型DCDC效率更高! 管子Q1存在着严重的开关损耗,但是Q2上很小,因为当需要Q2导通的时候,Q2的体二极管肯定优先导通,在它的米勒平台阶段,电流大部分从体二极管走了。在需要Q2关断的时候,管子先关闭,电流会从二极管走,直到Q1打开,二极管截止。Q2打开和关闭的过程,电流都由二极管分走,这让Q2的开关损耗变得很小。换个角度理解,由于体二极管的导通,Q2始终在VDS比较小的时候导通或关断。

管子Q1存在着严重的开关损耗,但是Q2上很小,因为当需要Q2导通的时候,Q2的体二极管肯定优先导通,在它的米勒平台阶段,电流大部分从体二极管走了。在需要Q2关断的时候,管子先关闭,电流会从二极管走,直到Q1打开,二极管截止。Q2打开和关闭的过程,电流都由二极管分走,这让Q2的开关损耗变得很小。换个角度理解,由于体二极管的导通,Q2始终在VDS比较小的时候导通或关断。

一定要选择ESR低的电容。

一定要选择ESR低的电容。

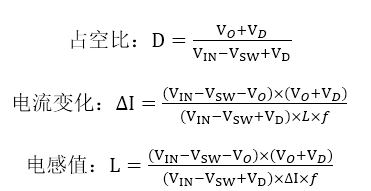

假设输入电压是VIN,Q1上的压降是VSW,Q2上的压降是VD,输出电压是VO,开关频率是f,占空比是D,如下两个公式成立:

假设输入电压是VIN,Q1上的压降是VSW,Q2上的压降是VD,输出电压是VO,开关频率是f,占空比是D,如下两个公式成立:

其中TON是电流上升时间,TOFF是电流下降时间。TON+TFF=1/f,上面两个公式结合,可以得出:

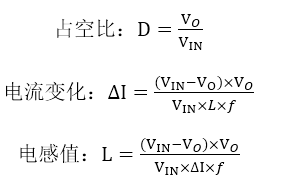

其中TON是电流上升时间,TOFF是电流下降时间。TON+TFF=1/f,上面两个公式结合,可以得出: 如果忽略Q1和Q2的压降,VSW=VD=0V,上面公式简化为:

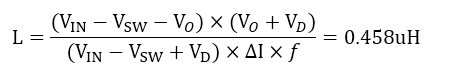

如果忽略Q1和Q2的压降,VSW=VD=0V,上面公式简化为:  举例: NCP6463,Q1阻抗36mΩ,Q2阻抗19mΩ,VIN=3.6V,VO=1.225V,IO=3.9A,∆I=0.85A,f=3MHz,带入上面公式:

举例: NCP6463,Q1阻抗36mΩ,Q2阻抗19mΩ,VIN=3.6V,VO=1.225V,IO=3.9A,∆I=0.85A,f=3MHz,带入上面公式:  接近规格书推荐的电感值0.47uH。

接近规格书推荐的电感值0.47uH。

注意电流探头要距离DCDC远一点,以防DCDC干扰到电流钳。

注意电流探头要距离DCDC远一点,以防DCDC干扰到电流钳。

普通要充分,足够的走线宽度,以减小寄生参数,还有能利于散热。如下图:

普通要充分,足够的走线宽度,以减小寄生参数,还有能利于散热。如下图:  当由多个DCDC存在时,DCDC的取电要从源头开始,如下图:

当由多个DCDC存在时,DCDC的取电要从源头开始,如下图: