| 一种基于扩散热阻的双面散热平面互联模块热建模方法 | 您所在的位置:网站首页 › cauer模型 › 一种基于扩散热阻的双面散热平面互联模块热建模方法 |

一种基于扩散热阻的双面散热平面互联模块热建模方法

1.本发明属于电力电子器件领域,具体涉及一种基于扩散热阻的双面散热平面互联模块热建模方法。 背景技术: 2.随着新能源汽车,轨道交通,智能电网和新一代移动通讯等领域的发展,对功率半导体模块的要求也随之提高,主要体现在需要更大功率,更好可靠性的功率模块,然而目前传统的功率模块具有封装寄生参数大,结壳热阻大,等问题,无法充分发挥功率半导体的性能,因此,新型封装结构的功率模块的研制成为需要,双面散热平面互联模块是一种新的封装结构,具有寄生参数小,散热能力强的优点,但其由于结构复杂,热模型的表征存在难点。3.针对模块热建模的方法,热网络模型法通过考虑一维传热路径,建立foster或cauer热网络,该模型描述单芯片模块时有较好的表现,在多芯片并联模块中由于热耦合会造成很大的误差。4.针对模块温度的准确建模,业界一般采用有限元方法,基于comsol,ansys等商业有限元软件进行求解,但该方法具有计算量大,计算时间长等问题,会限制模块在设计阶段优化迭代的效率。5.国内外也有学者提出基于傅里叶级数的热建模方法,将模块几何模型简化,列写热传导方程,通过把待求函数展开为傅里叶级数来实现功率模块热流的描述,该方法只适用于传统封装结构,并不适用于新型封装结构。 技术实现要素: 6.本发明的目的在于提供一种基于扩散热阻的双面散热平面互联模块热建模方法,以解决现有技术存在的问题,本发明所需计算量小,计算速度快,对模块结构适应性强,适合双面散热平面互联模块设计阶段的快速热建模。7.为达到上述目的,本发明采用如下技术方案:8.一种基于扩散热阻的双面散热平面互联模块热建模方法,包括以下步骤;9.s1:设置平面互联模块dbc各层厚度、芯片型号、互联结构、焊层类型和厚度,设置环境温度和对流换热系数,并设置模块的结构,设置每个芯片的损耗,设置芯片向顶部dbc与底部dbc传递热损耗的初值;10.s2:在comsol中对底部dbc、芯片和芯片对应的焊层进行建模,模型中只考虑底部dbc,一个芯片,且芯片位于dbc中心位置,对芯片赋予设定值的损耗,仿真获得dbc上铜层不同面积时的芯片平均温度和铜层平均温度,以及底部dbc上铜层面积最大时的上铜层下表面垂直方向热通量分布和温升分布;11.s3:根据模块的结构,获取芯片所在的铜层,根据铜层的大小和s2中的结果,得到对应的芯片平均温升和铜层平均温升;12.s4:考虑芯片间的热耦合效应和边缘效应,结合s2中所得结果,计算在同一块dbc铜层上的芯片由于热耦合和边缘效应导致的温升;13.s5:根据s2中获得的热通量分布和平均温度信息,获得在底部dbc同一块铜层上的芯片热损耗引起另一块铜层和另一块铜层上的芯片的温升,综合s3、s4计算结果,完成底部传热通道热模型;14.s6:在comsol中对顶部dbc、芯片、铜排以及三者之间用于连接的焊层进行建模,模型中只考虑dbc,一个芯片,铜排,且芯片中心位于dbc中心,通过铜排和焊层连接到顶部dbc,仿真获得顶部dbc下铜层不同大小时,芯片的平均温度和铜层面积最大时的垂直方向热通量;15.s7:考虑顶部dbc下铜层之间的热耦合效应和边缘效应,并根据s6中计算得到的平均温度和热通量信息,计算在同一个dbc铜层上的芯片由于顶部dbc下铜层热耦合效应和边缘效应导致的温升,完成顶部传热通道热模型;16.s8:考虑经由铜排从底部dbc传热到顶部dbc这一现象,根据s2中获取的热通量分布估计铜排与底部dbc连接处的平均温度,根据铜排的热阻和芯片通过铜排向顶部dbc传递的热量,估计铜排与顶部dbc连接处的平均温度,根据铜排的热阻,计算出从底部dbc经由铜排,传递到顶部dbc的热损耗;17.s9:s5所建立的底部传热通道热模型,s7所建立的顶部传热通道热模型以及s8中的补充模型共同组成双面散热平面互联模块热模型,通过给定互联模块各项参数,即能够得到各个芯片的温升及传热情况;具体流程如下:根据s8计算的从底部dbc经由铜排,传递到顶部dbc的热损耗,考虑铜排从两个dbc之间传热,分别使用底部传热通道热模型和顶部传热通道热模型计算出各个芯片温升,对比两个模型的计算结果,若误差小于设定值,则输出底部传热通道热模型计算得到的芯片温升,芯片向顶部dbc与底部dbc传递热量的值,建模完成;否则,迭代调整芯片向顶部dbc与底部dbc传递热量的比例,重新代入模型进行计算。18.进一步地,所述步骤s2中,所建模型中,芯片位于dbc中心位置,对芯片赋予ptest=50w的损耗,控制dbc上铜层一直处于dbc中心,使上铜层长度从最长到芯片长度变化,宽度从最宽到芯片宽度变化,仿真芯片平均温度和铜层平均温度,并仿真获得dbc上铜层面积最大时上铜层下表面垂直方向热通量分布f(x,y)和温升分布θspread(x,y),其中x,y代表以芯片中心为原点时铜层上点的坐标。19.进一步地,所述步骤s3中,使用插值方法对s2中的芯片平均温升和铜层平均温升进行拟合,获得芯片平均温升和焊层平均温升关于铜层长宽的拟合函数θdie(lcu,wcu)和θtrace(lcu,wcu),其中θdie表示芯片平均温升,θtrace表示焊层平均温升,lcu为铜层长度,wcu为铜层宽度,获取芯片所在铜层所能包含的最大矩形的长宽,将其代入到拟合函数中,计算出芯片平均温升和铜层平均温升,并将芯片i通过焊层所连接的铜层所能包含的最大矩形铜层称为芯片i所在铜层,记为gi。20.进一步地,步骤s4中,芯片间的热耦合效应所产生的耦合热阻通过下式考虑:[0021][0022]其中i,j为在同一个铜层上的芯片的编号,rij表示芯片j对芯片i的耦合热阻,θspread表示dbc上铜层下表面的温升分布,xcj,ycj表示芯片j的中心坐标,scj在积分号下时表示为芯片j所在区域,其余情况表示芯片j的面积;[0023]边缘效应通过如下公式考虑,芯片在所在铜层中央时扩散的热量为:[0024][0025]芯片i在现实位置时扩散的热量为:[0026][0027]其中,stracegi表示芯片i所在铜层的区域,xci,yci表示芯片i的中心坐标,则考虑边缘效应,芯片i的温升为θdiepei/pe0,其中θdie表示根据芯片所在铜层大小计算出的芯片平均温升;[0028]同时考虑边缘效应和耦合效应,按芯片i热损耗为50w等比例缩放,得到芯片i受其他在同一铜层上的芯片和自己损耗影响而引起的温升为:[0029][0030]式中,θtestchip为s2中dbc铜层面积最大时的芯片平均温度,pei和pej分别为芯片i和j扩散的功耗,rji表示芯片i对芯片j的耦合热阻,θdie_i和θdie_j分别为根据芯片i和j所在铜层的大小计算出的函数θdie(lcu,wcu)的值,ptest为s2中施加损耗,pdj和pdi分别为芯片i,j从底部传热通道传递的损耗。[0031]进一步地,所述步骤s5中,考虑在不同铜层上的芯片之间的热耦合,取在不同的铜层上的芯片i和m,若dbc上铜层是最大状态,则芯片i对其所在铜层gi那一部分区域产生的温升影响为:[0032][0033]基于能量守恒,得到芯片i对其铜层以外的铜层产生影响的校正系数为:[0034][0035]其中,δtisolation表示在s2中对芯片施加设定值的损耗时的dbc绝缘层上表面平均温升,sisolation表示dbc绝缘层上表面的面积,θtracegi表示s3中获取的芯片i所在铜层的平均温升,stracegi表示芯片i所在铜层的面积;[0036]由此,得到芯片i对芯片m所在铜层温升产生的影响为:[0037][0038]同理,得到芯片i对芯片m温升产生的影响为:[0039][0040]按芯片i热损耗为50w等比例缩放,得到与芯片i不在同一个铜层上的其他芯片对芯片i温升的影响为:[0041][0042]其中pdm为芯片m从底部传热通道传递的热损耗;[0043]由此得到芯片i受所有芯片热损耗影响而产生的温升为:[0044]θdiei_all=θdiei_same+θdiei_diff[0045]按芯片i热损耗为50w等比例缩放,芯片i所在铜层受所有芯片热损耗产生的温升为:[0046][0047]其中,j表示和i在同一铜层上的所有芯片,且包括i;m表示和芯片i在不同铜层上的芯片;[0048]由此,计算得到芯片i到其所在铜层的一维热阻和扩散热阻之和为:[0049][0050]按芯片i所在铜层上的ni个芯片热损耗之和为niptest等比例缩放,芯片i所在铜层和陶瓷基板之间的扩散热阻为:[0051][0052]其中,ni表示芯片i所在铜层上芯片的数量,j表示和i在同一铜层上的所有芯片,且包括i;m表示和芯片i在不同铜层上的芯片;[0053]最后,芯片i的温升使用下式计算,其他芯片同理;[0054][0055]其中,rresidue表示底部dbc陶瓷层、下铜层和热对流过程的一维等效热阻;[0056][0057]至此,底部传热通道热模型建立完毕。[0058]进一步地,所述步骤s6中,芯片位于dbc中心位置,对芯片赋予20w的损耗,控制顶部dbc下铜层只有一片铜层,使其长度从最长到在长方向上与芯片所连接铜排完全接触所需的长度变化,宽度从最宽到从宽方向上与芯片所连接铜排完全接触所需的长度变化,仿真芯片平均温度,并针对上铜层面积最大时,记录上dbc铜层上表面垂直方向热通量分布fup,dbc铜层上表面温度分布θup,若铜排有不同的形状,则对每种形状均进行仿真。[0059]进一步地,所述步骤s7中,考虑通过顶部dbc下铜层上的热耦合效应,将芯片i对应铜排与顶部dbc所连接位置的焊层记为solderi_up,中心位置为(xciupyciup),中心位置定义为芯片的几何中心,solderi_up为芯片i对应铜排与顶部dbc连接的所有焊层,耦合热阻rcij_up,j与i连接在同一个顶部dbc下铜层上,计算如下:[0060][0061]其中,ssolderj_up在积分号下表示焊层所在区域,其余情况表示此区域面积;[0062]芯片温度计算时将芯片的一维热阻替换为芯片与铜排共同的热阻即可,其余与底部传热通道热模型相同,由此完成了顶部传热通道热模型。[0063]进一步地,所述步骤s8中,考虑底部dbc经由铜排,传递到顶部dbc的热量,首先使用下式预估顶部dbc与铜排接触位置的温度:[0064][0065][0066]其中,tlu为预估的顶部dbc与所有铜排接触位置的温度平均温度,i,j均表示连接顶部dbc的芯片,ni表示芯片i所连接的顶部dbc铜层所连接的芯片的个数,tuppathi表示顶部传热通道热模型所计算出的芯片i的温度,pui表示芯片i通过顶部传热通道传递的热量;rcu表示该铜层上所有芯片的铜排的等效热阻,rsinglebondingi表示单根铜排的热阻,rcij_upk表示芯片i连接铜排和芯片j连接铜排与dbc接触位置之间的耦合热阻,且rcij_upk=rcij_up;[0067]接着使用下式估算铜排与底部dbc接触位置的温度:[0068][0069]其中,(xcpi,ycpi)表示芯片i所连接铜排与底部dbc焊接处的中心坐标,(xcj,ycj)表示距离(xcpi,ycpi)最近的芯片j的中心坐标,lchip和wchip表示芯片的长和宽,tdownpathi表示底部dbc传热通道热模型计算出来的芯片i的温度;[0070]trd表示底部dbc所有与芯片i并联的芯片所连接铜排与底部dbc接触位置的平均温度,使用下式计算:[0071][0072]由此,计算出所有与芯片i并联的芯片的铜排传导的从底部dbc传递到顶部dbc的热损耗pex为:[0073]pex=(trd-tlu)/rcup[0074][0075]其中,rsinglebondingpi表示单根铜排的热阻,rcij_upp表示在芯片i连接铜排和芯片j连接铜排与dbc接触位置之间的耦合热阻,且rcij_upp=rcij_up。[0076]进一步地,所述步骤s8中,考虑底部dbc经由铜排,传递到顶部dbc的热量,首先使用下式预估顶部dbc与铜排接触位置的温度:[0077][0078][0079]其中,tlu为预估的顶部dbc与所有铜排接触位置的温度平均温度,i,j均表示连接顶部dbc的芯片,ni表示芯片i所连接的顶部dbc铜层所连接的芯片的个数,tuppathi表示顶部传热通道热模型所计算出的芯片i的温度,pui表示芯片i通过顶部传热通道传递的热量,rcu表示该铜层上所有芯片的铜排的等效热阻,rsinglebondingi表示单根铜排的热阻,rcij_upk表示芯片i连接铜排和芯片j连接铜排与dbc接触位置之间的耦合热阻,且rcij_upk=rcij_up;[0080]接着使用下式估算铜排与底部dbc接触位置的温度:[0081][0082]其中,(xcpi,ycpi)表示芯片i所连接铜排与底部dbc焊接处的中心坐标,(xcj,ycj)表示距离(xcpi,ycpi)最近的芯片j的中心坐标,lchip和wchip表示芯片的长和宽,tdownpathi表示底部dbc传热通道热模型计算出来的芯片i的温度;[0083]trd表示底部dbc所有与芯片i并联的芯片所连接铜排与底部dbc接触位置的平均温度,使用下式计算:[0084][0085]由此,计算出所有与芯片i并联的芯片的铜排传导的从底部dbc传递到顶部dbc的热损耗pex为:[0086]pex=(trd-tlu)/rcup[0087][0088]其中,rsinglebondingpi表示单根铜排的热阻,rcij_upp表示在芯片i连接铜排和芯片j连接铜排与dbc接触位置之间的耦合热阻,且rcij_upp=rcij_up。[0089]进一步地,所述步骤s9中,根据s8中计算出从底部dbc经由铜排,传递到顶部dbc的热损耗,考虑铜排从两个dbc之间传热,分别使用底部传热通道热模型和顶部传热通道热模型计算出各个芯片温升,修正后的底部传热通道结温计算公式如下,顶部传热通道同理修改,计算出t’uppathi:[0090][0091]式中,p*exgi表示从芯片i所在底部dbc铜层gi经由铜排传递到顶部dbc的热量;[0092]对比两个模型的计算结果,若误差小于阈值,则输出底部传热通道热模型计算得到的芯片温升,芯片向顶部dbc与底部dbc传递热量的值,否则,调整芯片向顶部dbc与底部dbc传递热量的比例,继续s5,s7,s8,s9步骤,调整过程如下式,以任意芯片i为例:[0093]ei=t′uppathi-t′downpathi[0094][0095][0096]其中,puin和pdin分别表示第n次迭代时的芯片i向顶部dbc与底部dbc传热通道传递的热损耗,ζ代表迭代的速度,取0.1~0.3。[0097]与现有技术相比,本发明具有以下有益的技术效果:[0098]本发明使用基于扩散热阻的方法,首先使用comsol仿真出简单布局下的热流分布和温度分布,之后考虑热耦合效应,边缘效应和封装结构带来的特有传热路径,建立了一种快速热建模方法,有别于其他方法,本方法所需计算量小,计算速度快,对模块结构适应性强,适合双面散热平面互联模块设计阶段的快速热建模。附图说明[0099]图1为双面散热平面互联模块的封装结构图;[0100]图2为两种铜排形状示意图,其中(a)为第一种铜排形状,(b)为第二种铜排形状;[0101]图3为芯片标号和dbc布局示意图;[0102]图4为s2中上铜层面积最大时有限元仿真样例图;[0103]图5为s6中有限元仿真样例图;[0104]图6为底部dbc-铜排-顶部dbc传热路径位置图。[0105]图7为建立该双面散热平面互联模块热模型的流程图。具体实施方式[0106]为了更详细地解释本发明,下面将结合附图,以图1所示的双面散热平面互联模块为例对本发明做进一步的详细说明。[0107]本发明提出的基于扩散热阻的双面散热平面互联模块热建模方法,具体步骤包括:[0108]s1:给定平面互联模块dbc各层厚度,芯片型号,互联结构,焊层类型和厚度,环境温度,对流换热系数,并给定模块的结构,给定每个芯片的损耗,给定芯片向顶部dbc与底部dbc传递热损耗的初值。[0109]s2:在comsol中对底部dbc,芯片和芯片对应的焊层进行建模,模型中只考虑底部dbc,一个芯片,且芯片位于dbc中心位置。对芯片赋予50w的损耗,仿真获得dbc上铜层不同面积时的芯片平均温度和铜层平均温度,仿真获得底部dbc上铜层面积最大时的上铜层下表面垂直方向热通量分布和温升分布。[0110]s3:根据模块的结构,获取芯片所在的铜层,根据铜层的大小和s2中的结果,得到对应的芯片平均温升和铜层平均温升。[0111]s4:考虑芯片间的热耦合效应和边缘效应,结合s2中所得结果,计算在同一块dbc铜层上的芯片由于热耦合和边缘效应导致的温升。[0112]s5:根据s2中获得的热通量分布和平均温度信息,获得在底部dbc同一块铜层上的芯片热损耗引起另一块铜层和另一块铜层上的芯片的温升,综合s3、s4计算结果,完成底部传热通道热模型。[0113]s6:在comsol中对顶部dbc,芯片,铜排,以及三者之间用于连接的焊层进行建模,模型中只考虑dbc,一个芯片,铜排,且芯片中心位于dbc中心,通过铜排和焊层连接到顶部dbc,仿真获得顶部dbc下铜层不同大小时,芯片的平均温度和铜层面积最大时的垂直方向热通量,仿真中芯片损耗设置为20w。[0114]s7:考虑顶部dbc下铜层之间的热耦合效应和边缘效应,并根据s6中计算得到的平均温度和热通量信息,计算在同一个dbc铜层上的芯片由于顶部dbc下铜层热耦合效应和边缘效应导致的温升,完成顶部传热通道热模型。[0115]s8:考虑经由铜排从底部dbc传热到顶部dbc这一现象,根据s2中获取的热通量分布估计铜排与底部dbc连接处的平均温度,根据铜排的热阻和芯片通过铜排向顶部dbc传递的热量,估计铜排与顶部dbc连接处的平均温度,根据铜排的热阻,计算出从底部dbc经由铜排,传递到顶部dbc的热损耗。[0116]s9:s5所建立的底部传热通道热模型,s7所建立的顶部传热通道热模型以及s8中的补充模型共同组成了双面散热平面互联模块热模型,通过给定互联模块各项参数,即可得到各个芯片的温升及传热损耗。具体流程如下:根据s8,计算出从底部dbc经由铜排,传递到顶部dbc的热损耗,考虑铜排从两个dbc之间传热,分别使用底部传热通道热模型和顶部传热通道热模型计算出各个芯片温升,对比两个模型的计算结果,若误差小于一定程度,则输出底部传热通道热模型计算得到的芯片温升,芯片向顶部dbc与底部dbc传递热量的值,否则,迭代调整芯片向顶部dbc与底部dbc传递热量的比例,重新代入模型进行计算。[0117]步骤s1中,模块自上至下包括dbc,铜排,芯片,dbc,任意两者之间使用焊料连接,如图1所示,该模块为半桥模块,dbc尺寸为48mm*38mm,上下两个传热面的传热系数均为h=10000w/(m2.k),环境温度设置为25℃,焊料为sac305,厚度为50μm芯片采用cree公司的cpm3-1200-0013a,dbc铜层和陶瓷层厚度分别为0.3mm和0.68mm,该模块中出现的两种不同形状的铜排如图2所示,铜排两端弯折,且通过焊层与dbc直接连接的部位的长度基本不影响铜排的导热性能,因此,此位置长度不同的铜排也认为是相同形状的铜排。每个桥臂有3个芯片,芯片标号和dbc布局如图3所示,假设芯片热损耗为pall=[pall1,pall2,pall3,pall4,pall5,pall6],通过底部传热通道散发的热损耗为pd=[pd1,pd2,pd3,pld4,pld5,pld6],通过顶部传热通道散热的热损耗为pu=[pu1,pu2,pu3,pu4,pu5,pu6].设芯片向顶部和底部传热通道散热的热损耗比例初值均为75%和25%。[0118]步骤s2中,芯片位于dbc中心位置,对芯片赋予50w的损耗,控制dbc上铜层一直处于dbc中心,使上铜层长度从最长到芯片长度变化,宽度从最宽到芯片宽度变化,仿真芯片平均温度和铜层平均温度,并仿真获得dbc上铜层面积最大时上铜层下表面垂直方向热通量分布f(x,y)和温升分布θspread(x,y),图4为comsol中所建立的上铜层面积最大时的仿真几何结构图。[0119]步骤s3中,使用插值方法对s2中的芯片平均温升和铜层平均温升进行拟合,获得芯片平均温升和焊层平均温升关于铜层长宽的拟合函数θdie(lcu,wcu)和θtrace(lcu,wcu),获取芯片所在铜层所能包含的最大矩形的长宽,将其代入到拟合函数中,计算出芯片平均温升和铜层平均温升,并将芯片所在铜层所能包含的最大矩形铜层称为芯片所在铜层,如图3所示,芯片1,2,3所在的铜层记为trace12,芯片4,5,6所在铜层记为trace11,即g1=g2=g3=12,g4=g5=g6=11。[0120]步骤s4中,芯片间的热耦合效应所产生的耦合热阻通过下式考虑[0121][0122]其中i,j为在同一个铜层上的芯片的编号。[0123]边缘效应通过如下公式考虑,以芯片1,2,3所在的trace12为例,芯片在所在铜层中央时可以扩散的热量为[0124][0125]其中strace12表示trace12所在区域,也表示trace12的面积,上式中表示该区域,芯片i在现实位置时可以扩散的热量为[0126][0127]则考虑边缘效应,芯片i的温升应该为θdiepei/pe0(i=1,2,3)[0128]同时考虑边缘效应和耦合效应,以芯片1为例,可以得到受其他在同一铜层上的芯片和自己损耗影响而引起的温升为(按芯片1热损耗为50w等比例缩放)[0129][0130]式中,θtestchip为s2中dbc铜层面积最大时的芯片平均温度,ptest为s2中施加损耗,为50w。其他芯片的计算方法同理。[0131]步骤s5中,需要考虑在不同铜层上的芯片之间的热耦合,取在不同的铜层上的芯片i和m,若dbc上铜层是最大状态,则芯片i对其所在铜层产生的温升影响为[0132][0133]基于能量守恒,可以得到芯片i对其铜层以外的铜层产生影响的校正系数为[0134][0135]其中,δtisolation表示在s2中对芯片施加50w损耗时的dbc绝缘层上表面平均温升,sisolation表示dbc绝缘层上表面的面积,θtracegi表示s3中获取的芯片i所在铜层的平均温升,stracegi表示芯片i所在铜层的面积。[0136]由此,可以得到芯片i对芯片m所在铜层温升产生的影响为[0137][0138]同理,也可以得到芯片i对芯片m温升产生的影响为[0139][0140]以芯片1为例,由此可以得到与芯片1不在同一个铜层上的其他芯片(芯片4,5,6)对芯片1温升的影响为(按芯片1热损耗为50w等比例缩放)[0141][0142]由此得到芯片1受所有芯片热损耗影响而产生的温升为[0143]θdie1_all=θdie1_same+θdie1_diff[0144]以芯片1为例,芯片1所在铜层trace12受所有芯片热损耗产生的温升为(按芯片1热损耗为50w等比例缩放)[0145][0146]由此,可以计算得到芯片1到其所在铜层的一维热阻和扩散热阻之和为[0147][0148]芯片1所在铜层和陶瓷基板之间的扩散热阻为(按芯片1,2,3热损耗之和为150w等比例缩放)[0149][0150]最后,芯片1的温升可以使用下式计算,其他芯片同理。[0151][0152]至此,底部传热通道热模型建立完毕。[0153]步骤s6中,在comsol中对顶部dbc,芯片,铜排,以及三者之间用于连接的焊层进行建模,模型中只考虑dbc,且芯片位于dbc中心位置,对芯片赋予ptest2=20w的损耗,控制顶部dbc下铜层只有一片铜层,使其长度从最长到在长方向上与芯片所连接铜排完全接触所需的长度变化,宽度从最宽到从宽方向上与芯片所连接铜排完全接触所需的长度变化,样例如图5所示。仿真芯片平均温度,并针对上铜层面积最大时,记录上dbc铜层上表面垂直方向热通量分布fup,dbc铜层上表面温度分布θup,若铜排有不同的形状,则每种形状都需要进行仿真。[0154]步骤s7中,考虑通过铜排连接到同一片顶部dbc下铜层上的芯片之间的热耦合效应,将芯片i,j对应铜排与顶部dbc所连接位置的焊层记为solderi_up,中心位置为(xciupyciup),中心位置定义为芯片的几何中心,solderi_up为芯片i对应铜排与顶部dbc连接的所有焊层,耦合热阻rcij_up(j与i连接在同一个顶部dbc下铜层上)计算如下[0155][0156]其中,ssolderj_up在积分号下表示焊层所在区域,其余情况表示此区域面积。[0157]芯片温度计算方法只需将芯片的一维热阻替换为芯片与铜排共同的热阻即可,由此完成了顶部传热通道热模型。[0158]步骤s8中,考虑底部dbc经由铜排,传递到顶部dbc的热量,传热路径位置如图6所示(仅展示了芯片1,4及其铜排),本布局中该现象发生在芯片1,2,3对应的铜排上,因此可以使用下式预估顶部dbc与铜排接触位置的温度[0159][0160][0161]其中,tlu为预估的顶部dbc与所有铜排接触位置的温度平均温度,i,j均表示连接顶部dbc的芯片,tuppathi表示顶部传热通道热模型所计算出的芯片i的温度,pui表示芯片i通过顶部传热通道传递的热量。rcup表示该铜层上所有芯片的铜排的等效热阻。rsinglebondingi表示单根铜排的热阻,本例中为5.20k/w,rcij_upk表示芯片i连接铜排和芯片j连接铜排之间的耦合热阻,本方案中认为rcij_upk=rcij_up。[0162]接着使用下式估算铜排与底部dbc接触位置的温度[0163][0164]其中,(xcpi,ycpi)表示芯片i所连接铜排与底部dbc焊接处的中心坐标,(xcj,ycj)表示距离(xcpi,ycpi)最近的芯片j的坐标。lchip和wchip表示芯片的长和宽。如图1所示,在本模块中,距离芯片1,2,3所连接铜排与底部dbc焊接处最近的芯片分别为芯片4,5,6。[0165]trd表示底部dbc所有与芯片i并联的芯片所连接铜排与底部dbc接触位置的平均温度。使用下式计算[0166][0167]由此,可以计算出所有与芯片i(i=1,2,3)并联的芯片的铜排传导的从底部dbc传递到顶部dbc的热损耗pex为[0168]pex=(trd-tlu)/rcup[0169]rcup=(3rsinglebondingp+2rc21_dbc2+2rc32_dbc2+2rc31_dbc2)/9[0170]其中,rsinglebondingp表示铜排将热量从底部dbc传递到顶部dbc传热通道的热阻,为5.489k/w。[0171]步骤s9中,根据s8中计算出从底部dbc经由铜排,传递到顶部dbc的热损耗,考虑铜排从两个dbc之间传热,分别使用底部传热通道热模型和顶部传热通道热模型计算出各个芯片温升,修正后的底部传热通道结温计算公式如下,顶部传热通道同理修改,计算出t’uppathi。[0172][0173]式中,p*exgi表示从芯片i所在底部dbc铜层经由铜排传递到顶部dbc的热量。对于本模块,对于芯片1,2,3,不存在铜排从trace12上直接将热量导入上dbc,因此,p*exg1=p*exg2=p*exg3=0。[0174]对比两个模型的计算结果,若误差小于一定程度,则输出底部传热通道热模型计算得到的芯片温升,芯片向顶部dbc与底部dbc传递热量的值,否则,调整芯片向顶部dbc与底部dbc传递热量的比例,继续s5,s7,s8,s9步骤,调整过程如下式,以任意芯片i为例。[0175]ei=t′uppathi-t′downpathi[0176][0177][0178]puin和pdin分别表示第n次迭代时的芯片i向顶部dbc与底部dbc传热通道传递的热损耗,ζ代表迭代的速度,本文取1/7。[0179]完成热建模后,赋予芯片损耗pall=[86.275w,82.9848w,88.3108w,98.4435w,96.1152w,97.9825w],本方法计算出来的结温与有限元软件comsol仿真得到的平均结温温升对比情况见表1[0180]表1本发明方法与有限元软件芯片平均温升计算结果对比[0181] t1t2t3t4t5t6本发明方法/℃79.3017586.8960380.8878193.12482101.668593.45487有限元软件/℃76.78784.31978.63590.7398.79289.616误差3.27%3.06%2.86%2.64%2.91%4.28%[0182]有限元软件耗时10s,本发明方法建模耗时约0.25s,迭代计算过程一般电热联合仿真需要进行2-4次迭代,本发明所提方法可以大幅减小电热联合仿真所需时间,并保证一定的精确度(5%)。[0183]以上结合具体实例对本发明的具体实施方式对本发明作了进一步详细说明,所述内容均为对本发明的解释但这些说明不能被理解为限制了本发明的范围,本发明的保护范围由随附的权利要求书限定,任何在本发明权利要求基础上的改动就是本发明的保护范围。 |

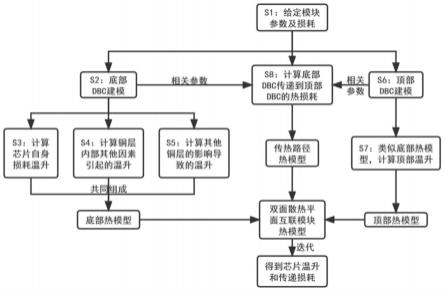

【本文地址】