| Allegro的模块化设计 | 您所在的位置:网站首页 › cadence软件使用说明 › Allegro的模块化设计 |

Allegro的模块化设计

|

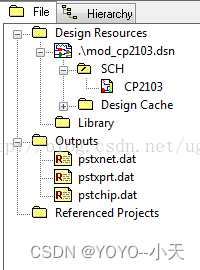

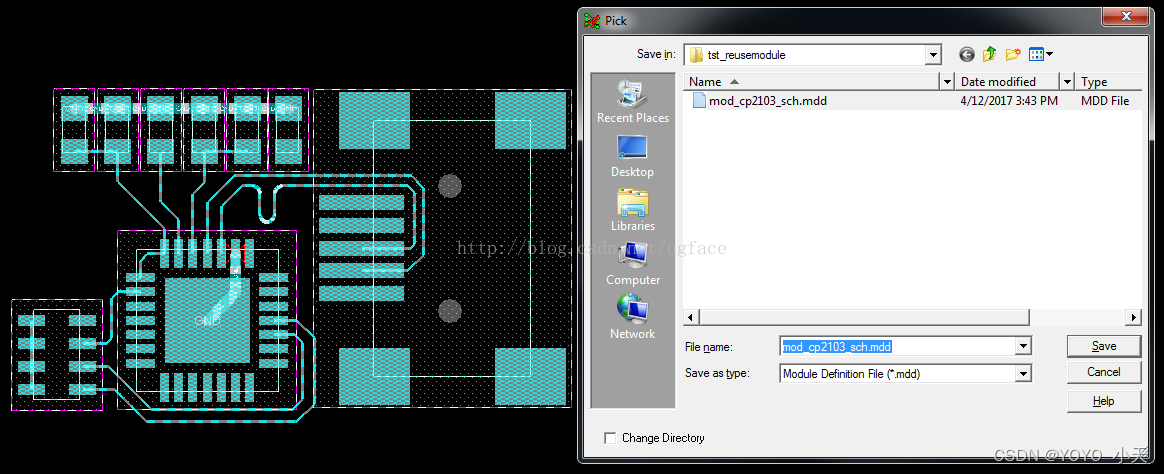

一.何为模块化 毫无疑问,如果能够将某种验证成熟的技术或已有的东西拷贝粘贴,是降低重复劳动的良好手段。就像我们建立了一个元件库后,每次使用时只需将该元件引用或例化一次即可,这样做非常高效。电路设计的模块化也是同样的道理,如果针对某种经常使用或者通道重复的电路,能够将其原理图和对应的PCB“封装”在一起,最终形成类似元件库中一个简单元件的Schematic和Footprint统一的形式,这就做成了模块化电路。 二.如何模块化 Allegro中模块化设计的操作会有多种,但都非常类似,抓住核心理念和对基本 概念形成正确理解才是关键。以下以一个瞎编乱造的电路为例,以自下而上的方式对操作步骤进行一个简要说明。 1.创建需要模块化的电路的原理图:在Capture下new->project->mod_cp2103,为了后续方便,将默认的SCHEMATIC1重命名成SCH,并在该工程下进行CP2103原理图的设计,此处与一般设计无异。 3. 生成与原理图对应的PCB模块:对模块电路经过上述annotate且检查无误后,可导出netlist并开始layout工作,或是在Place后即创建PCB的Module。与正常layout的区别是,当自己感觉模块可以或需要并入主电路进行布局布线工作时,将该模块的PCB创建成一个名为“DSN_NAME”+“_”+“SCH_NAME”的.mdd文件。其中DSN_NAME指模块的设计名称,比如此处为mod_cp2103,SCH_NAME此处指SCH,( 默认生成的名称为SCHEMATIC1)。因此按照下图所示,创建的模块需要被命名为mod_cp2103_SCH.mdd,创建时确保打开所有设计过的层面,防止出现不一致。Tools->createmodule而后框选需要创建模块的部分,并输入坐标,然后将文件另存为mod_cp2103_SCH.mdd。

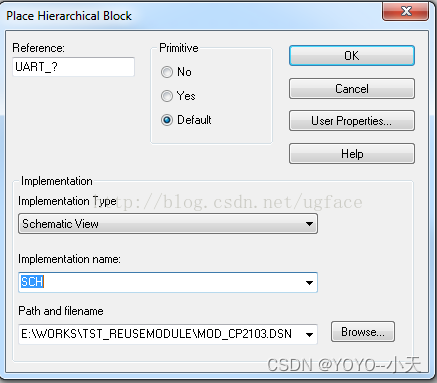

来在原理图层面引用该模块,block的界面设置结果如下图所示。注意首先设置Pathand filename后再选择Implementationname项。 Reference:也可设置成如UART_?形式 Implementation Type:选择schematicview Path and filename:选择模块原理图设计的.DSN文件,此处为MOD_CP2103.DSN Implementation name:在选择好DSN路径后,可下拉找到先前rename后的SCH

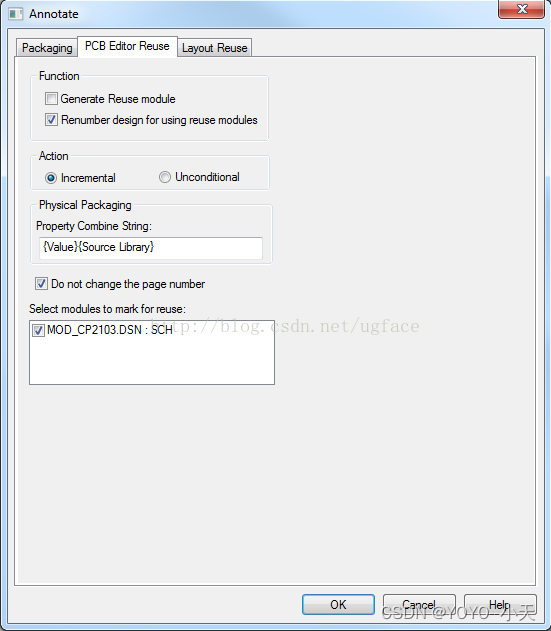

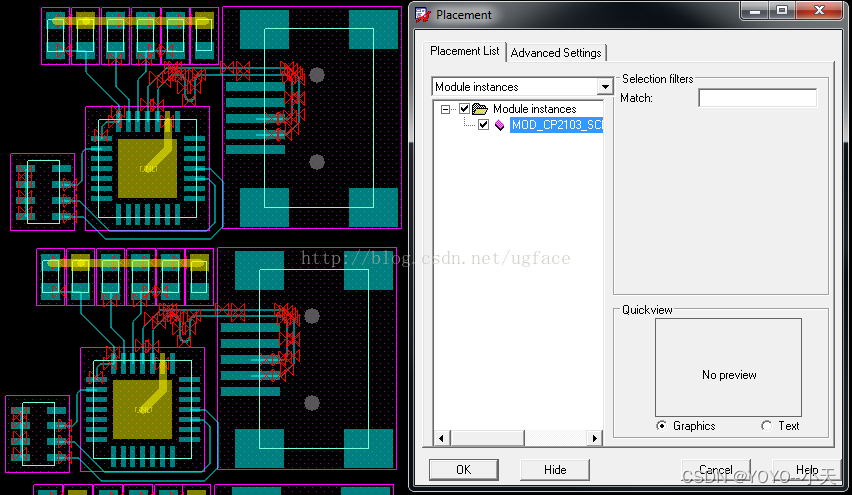

对设计完成的主电路在创建网表前需要进行annotate,此时在annotate的PCBEditor Reuse界面下,为了使用模块,需要做如下设置。 勾选:Renumberdesign for using reuse modules 勾选:Donot change the page number 同时在Selectmodules to mark for reuse框中选择对应的模块 5. 在PCB中放置模块的PCB:在主电路的PCB中导入netlist后,通过Place->Moduleinstances可放置相应的模块到主PCB设计中去。

按照上述操作,可以作为一种层级电路设计的操作手段,关键在于annotate过程中一些选项的使用,或者说不管Hierarchical或Flat模式,对元件而言首要的属性是refdes,只有该属性在电路中保持唯一才能确保正确性。因此,在多次的annotate过程中一定注意unconditional和incremental选项。其次,上述操作的多处涉及到路径的设置,相对路径对于设计的移植性大有好处。 ———————————————— |

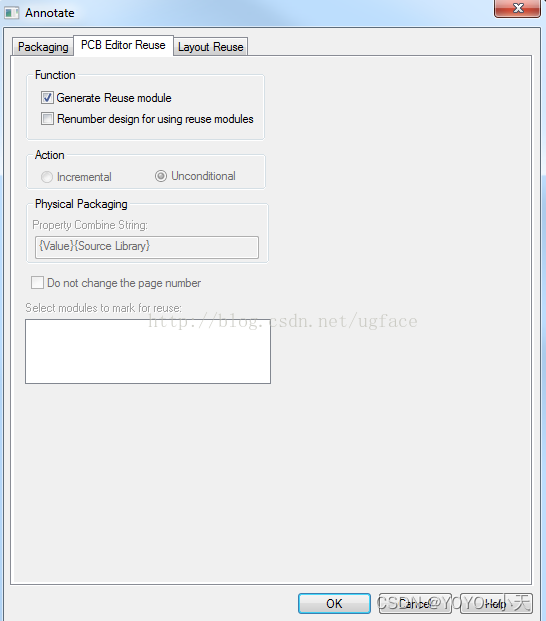

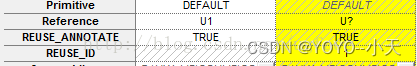

【本文地址】

2. 对构建完毕的原理图添加reuse属性:正常的设计中,元件会按照U1,U2, C1, C2……的模式自动编号或annotate,即对同一设计中元件的reference进行递增且确保不重复的处理。模块复用时,引用模块的电路首先需要知道该元件是一个模块,其次需要对其内部元件与主电路其余部分元件进行统一编号,因此需要对模块增加一定的属性,以通知引用电路,这个属性的加入就是在对模块电路的annotate过程中。与通常annotate不同的是,在对该模块进行annotate的 PCB Editor Reuse页面下,选中Generate Reuse Module,并且在Action部分选为Unconditional后点击Ok。完成后可发现模块中的元件增加了一些Reuse的属性。

2. 对构建完毕的原理图添加reuse属性:正常的设计中,元件会按照U1,U2, C1, C2……的模式自动编号或annotate,即对同一设计中元件的reference进行递增且确保不重复的处理。模块复用时,引用模块的电路首先需要知道该元件是一个模块,其次需要对其内部元件与主电路其余部分元件进行统一编号,因此需要对模块增加一定的属性,以通知引用电路,这个属性的加入就是在对模块电路的annotate过程中。与通常annotate不同的是,在对该模块进行annotate的 PCB Editor Reuse页面下,选中Generate Reuse Module,并且在Action部分选为Unconditional后点击Ok。完成后可发现模块中的元件增加了一些Reuse的属性。

4. 上述完成后,模块部分即构建完毕,而后新建主原理图工程,并防止hierarchicalblock

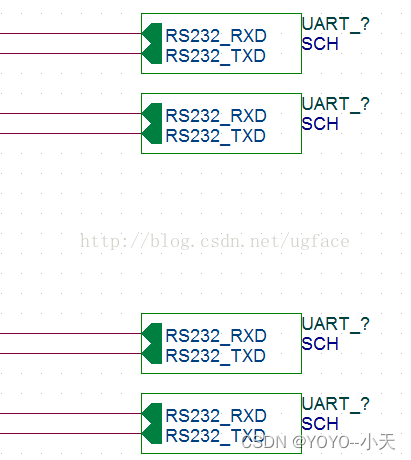

4. 上述完成后,模块部分即构建完毕,而后新建主原理图工程,并防止hierarchicalblock 放置多个后的原理图如下:

放置多个后的原理图如下:

至此,加入电路的其余部分已经设置完毕,则可createnetlist,并进入PCB阶段。

至此,加入电路的其余部分已经设置完毕,则可createnetlist,并进入PCB阶段。 三.结论

三.结论